今天,我们再学习一点点 后仿真相关技能。

那就是,了解 report_timing 中的 -include_hierarchical_pins 选项。

如果我们仅仅使用如下命令,执行后会发现:

pt_shell> report_timing -from FF1/CK -to FF2/d -delay_type max -include_hierarchical_pins

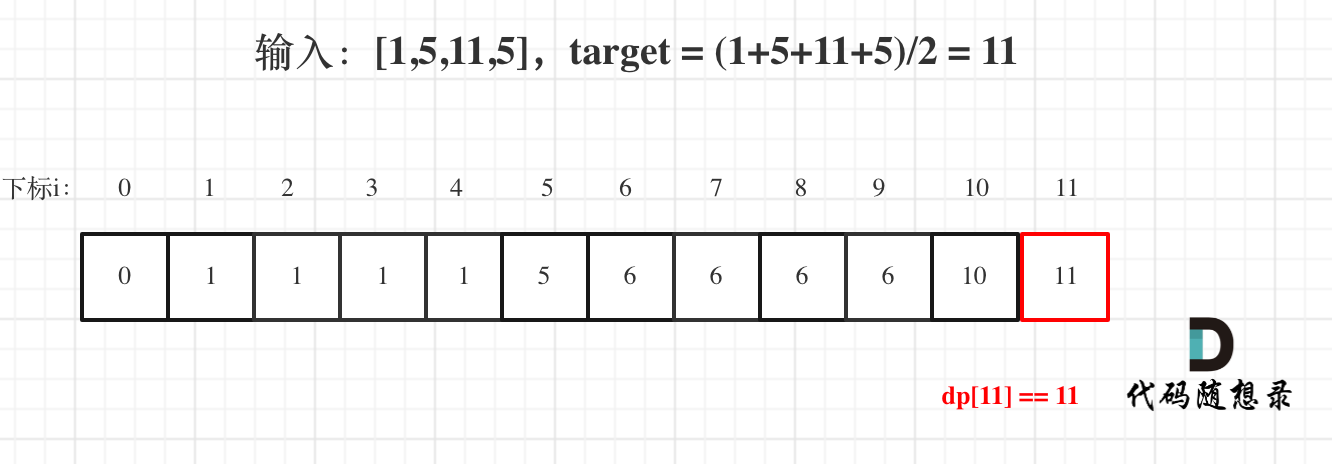

我们使用命令 report_timing 报出的如上路径延时信息,仅仅显示:

(1)FF1 寄存器 CK->Q 路径 延迟

(2)FF1 输出Q点 -> c1/ Y 路径延迟 (其中,c2 的pin 脚 为; A输入,Y输出) 的延时信息

(3)cell 实例 c1/Y -> c2/Y 路径延迟

(4)cell 实例 c2/Y -> FF2/D 路径延迟

(5) 中间跨层次连接net 之间的延迟信息

如果我们添加该选项,那么report_timing 报告的输出,将会涵盖如下虚线路径(红色箭头指示):

pt_shell> report_timing -from FF1/CK -to FF2/d -delay_type max -include_hierarchical_pins -input_pins

那么,还会显示如下红色箭头指示。c1 和 c2 的输入引脚 A 的延迟数据信息。</