本实例将演示如何在RFSOC 47DR开发板上,实现100G光口自环测试。此测试使用光口自环模块实现硬件互联,FPGA中进行25Gbps收发校验,通过vivado的硬件管理器烧写比特流,查看传输误差与眼图。

开发板启动模式设置为JTAG模式,插入光口自环模块,JTAG下载器和电源。RFSOC 47DR上有两个100G光口,标号分别是128和129,测试时需要选择对应的测试文件,光口模块也需要插入,具体位置如下图所示。

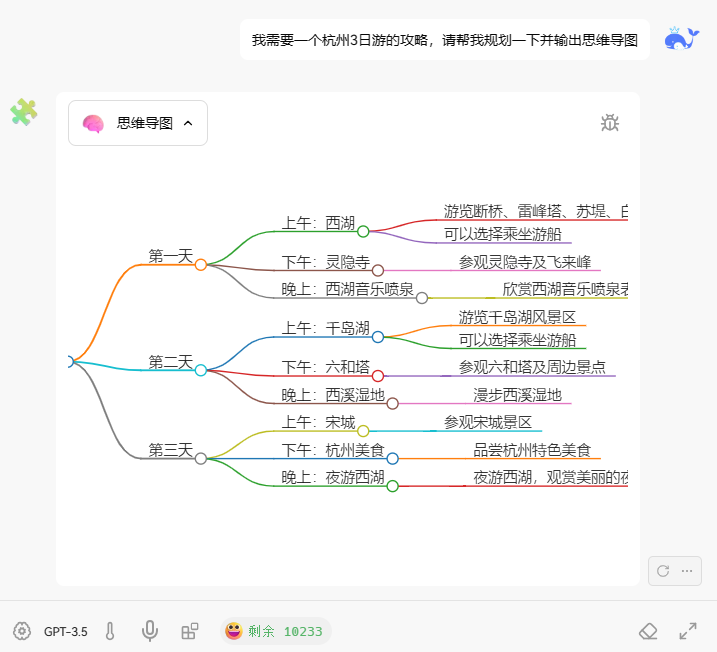

打开vivado的硬件管理器,烧写比特流时需要添加测试文件一同烧写,比特流文件与测试文件我都会提供在文章末尾。若比特流文件与测试文件在同一文件夹内,添加比特流后会自动添加测试文件。

烧写成功后点击Auto-detect links自动检测连接

连接后就可以看到自环的详细信息,每个通道的错误率,传输速度

右键某一个通道-->查看眼图,就可看到眼图的各种信息。

通过百度网盘分享的文件:RFSOC 47DR 100G光口自环测试

链接:https://pan.baidu.com/s/1iV9YF6u_t7GodthbUu3CVA

提取码:6ufv