【学术前沿】基于非易失性存储器硬件特性的存算一体神经网络设计方法

Lixia HAN, Peng HUANG, Yijiao WANG, Zheng ZHOU, Haozhang YANG, Yiyang CHEN, Xiaoyan LIU & Jinfeng KANG, Mitigating Methodology of Hardware Non-ideal Characteristics for Non-volatile Memory Based Neural Networks, doi: 10.1007/s11432-023-4021-y

研究简介

神经网络能够从复杂的非结构化数据中提取深层次的特征和信息,为数据处理提供了高效的解决方案。面向神经网络算法,传统基于冯诺依曼架构的信息处理系统面临着数据搬运造成的功耗和延迟瓶颈,极大地限制了能量效率和算力的提升。基于非易失性存储器的模拟型存算一体范式,可以在存储单元原位地高并行地执行向量矩阵乘法运算,消除了大量数据搬运,具有低功耗和低延迟的特点,在神经网络推理加速系统中显示出巨大的应用潜力。然而,来自器件、阵列和混合信号电路的非理想特性会引发计算误差,从而影响神经网络在存算一体芯片上的推理精度,成为基于非易失性存储器的模拟存算一体加速器向实际应用转化的关键障碍。

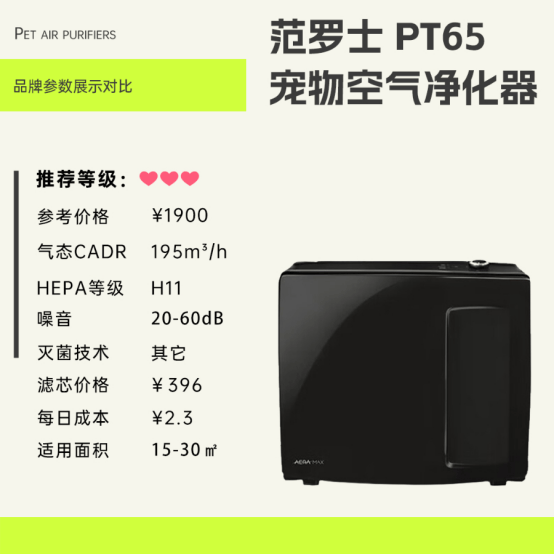

图1:基于非易失性存储器的模拟型存算一体范式面临的非理想因素分类

图2:提高基于非易失性存储器的存算一体神经网络硬件推理精度的方法流程图

来自北京大学和北京航空航天大学的研究人员开展了基于非易失性存储器硬件特性的存算一体神经网络设计方法研究。具体的创新点和意义包括:

-

本研究分析了基于非易失性存储器的存算一体神经网络面临的来自器件,阵列和电路的非理想因素,针对不同非理性因素的物理特性,建立了行为级描述模型,并根据其数学表达形式,将其分为量化误差,波动误差,固定缺陷误差,非线性误差和互连线电压降误差。

-

针对上述非理想因素模型的求解复杂度不同的特点,本研究分别提出了硬件感知训练和权重映射修正方法来提高存算一体神经网络推理精度。

- 硬件感知训练通过在算法训练过程中整合复杂度低的非理想因素来增强算法拟合能力;

- 权重映射修正通过在权重编程前补偿复杂度高的互连线电压降误差来提升存算一体神经网络推理精度。

-

对于CNN识别ImageNet数据集以及Transformer执行WMT中英翻译任务,上述存算一体神经网络设计方法可以有效实现95%以上的算法精度;在基于Flash存算一体芯片的MNIST数据集的实验验证中,存算一体神经网络推理精度达到了99.6%的算法精度。

相关设计方法已作为存算一体软硬件协同设计工具的子模块嵌入开源工具CoMN(https://github.com/booniebears/CoMN/)中。

图3:CNN识别ImageNet数据集以及Transformer执行WMT中英翻译任务的硬件推理精度

图4:基于Flash的模拟型存算一体芯片的MNIST数据集的实验验证(以数字“5”为例)

CoMN

CoMN平台由黄鹏教授的研究小组(北京大学)开发。该平台可供设计人员快速验证和进一步优化基于非易失性存储器的神经网络加速器的设计。模型的版权由开发人员维护,模型根据MIT许可证的条款进行分发。

CoMN 包括三个主要部分: 算法适配器,旨在通过考虑 NVM 设备的非理想性来提高神经网络的推理精度; mapper,开发通过优化管道、权重转换、分区和放置来自动将 CNN 模型映射到 CIM 芯片; 以及硬件优化器,开发用于在早期设计阶段搜索硬件微架构和电路设计空间。

相关材料

- 原文链接:Mitigating Methodology of Hardware Non-ideal Characteristics for Non-volatile Memory Based Neural Networks (sciengine.com)

- CoMN:GitHub - booniebears/CoMN

![NSSCTF练习记录:[SWPUCTF 2021 新生赛]ez_caesar](https://i-blog.csdnimg.cn/direct/928af8b76e3143c8946be8e8e5d4165f.png)

![[Spring] Spring原理(SpringBoot完结)](https://i-blog.csdnimg.cn/direct/1c7cb850baa94e748c91a03f26fb0b48.png)