概述

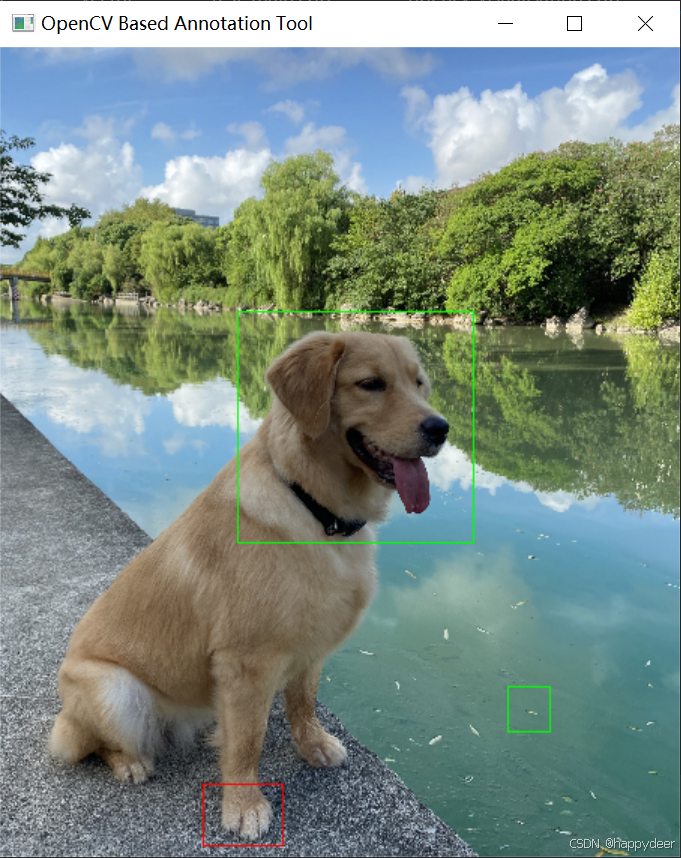

平面数据处理器(Planar Data Processor, PDP)沿宽x高的前两个维度平面执行操作,在NVDLA版中,PDPD旨在实现池化层,module定义在NV_NVDLA_pdp.v。支持最大、最小和平均池化方法。平面内的几个相邻输入元素将被发送到非线性函数来计算一个输出元素。下图显示了最大池的一个示例。3x2相邻元素中的最大值是合并结果值

下图显示了PDP子单元的内部模块,以及与其他单元和子单元的连接。该图从概念上捕捉了功能,但没有显示实际的RTL模块和层次结构。平面数据处理子单元从SDP或MCIF/SRAMIF接收数据,并将数据发送到MCIF/SRAMIF。

池化操作在一个平面内完成,不同平面之间没有干扰。下图显示了在一个平面上池化的完整方案,两个相邻内核的偏移量称为步距(stride)。当步距小于核的R和S时,存在重叠线,一些行可能被两个以上的相邻内核使用。输入数据按光栅扫描顺序流动,对于每个池内核,操作的数据也以光栅扫描顺序流动。

如果输入数据元素是内核的第一个元素,它将被存储到共享行缓冲区。共享行缓冲区中的数据被称为部分结果。如果一个输入数据元素既不是内核的第一个元素也不是最后一个元素,它将使用共享缓冲区中已有的部分结果进行操作,结果将存储到原始部分结果的同一条目中。部分结果计算在预处理块中完成。

- 在最大/最小池化方案的情况下,部分结果是输入元素的最大/最小值和原始部分结果。

- 在平均池方案的情况下,部分结果是输入元素和原始部分结果的总和。

如果输入数据元素是内核的最后一个元素,它将与来自共享行缓冲区的已有部分结果一起操作,以生成pre-final结果。后处理模块将从共享行缓冲区获取pre-final结果,并在适当操作后生成最终结果。这个最终结果被发送到SRAMIF或MCIF。

- 在最大/最小池化方案的情况下,pre-final结果是最终结果,不需要额外的操作。

- 在平均池化方案的情况下,最终结果可以通过以下方式计算

除法对于硬件实现来说是昂贵的,所以用一对scale_factors将除法转化为乘法。

除法对于硬件实现来说是昂贵的,所以用一对scale_factors将除法转化为乘法。

共享同一行数据的内核的最大数量由ceiling(Kernel _ height / Stride_H)决定 。一个平面内所需的总缓冲器条目数是width _ out×ceiling(Kernel _ height / Stride_H) ,并在RTL设计中分配总缓冲区入口号total_buf_entry 在一个平面内如下,每个entry 112位:

由于池化操作是一种下采样方法,因此有大量信息被丢弃。大型内核中的池化破坏性太大。在当前分析的网络中,有三种最常见的情况,一种是池大小为3x3,步幅为2x2。另一个是池大小2x2,步幅2x2,最后一个是池大小3x3,步幅1x1。还有另外两种较少使用的情况:一种是池大小为3x3,步幅为3x3。另一个是池大小7x7,步幅1x1,常用网络的池化数据如下:

所以2 ~ 8个池内核大小(宽度和高度)范围和1~8个步长范围对于正常使用来说足够了。在RTL设计中,我们将池化内核大小范围设置为1~8,将步幅范围设置为1 ~ 16。

平面数据处理子单元有两条输入路径。一个是单点数据处理子单元,另一个是外部RAM (MC/SRAM)。平面处理子单元有一个输出数据路径。输出数据总是发送到PDP外部的RAM(MC/SRAM)。在通常的实践中,在卷积层之后插入一个池化层。为了节省内存访问消耗,如果满足以下条件,平面数据处理子单元应直接从点处理单元接收数据。假设输出宽度是,以字节表示的总缓冲区大小为

,重叠行号

,以字节为单位的数据宽度是数据宽度 ,空间平面的数量称为正在进行的通道数量

,正常情况下,

应该等于kernel_per_group(对于INT16/FP16为16,对于INT8流水线为32),以下是平面加工的动态操作条件。

当输入数据来自点处理子单元时,输入数据序列与卷积输出序列相同,如下图所示。

输出顺序如下图所示。

如果不满足planar processing on-the-fly操作条件,planar processing应在off-fly模式下工作,它从PDMA接收数据,正在进行的通道数始终为16。分两种情况,一种是非分幅,一种是分幅。输入数据序列如下图所示。

输出数据序列如下图所示。

缓冲区大小估计

平面数据处理子单元中有三个主要的缓冲区:共享行缓冲区、读DMA缓冲区和写DMA缓冲区。对于共享行缓冲区,其大小决定了PDP是否可以直接处理来自SDP的数据。基于输入数据立方体高度,池化内核高度

,池内核在高度方向上

,输出数据立方体宽度

,组大小(int16/FP16的16个元素或int8的32个元素,~32byte),Groupsize和bytes_per_element(int8 为14/8,INT16为28/8,FP16为28/8)。

如果共享行缓冲区容量小于所需的消耗大小,PDP必须在离线模式下工作,因此会有性能下降,因为需要额外的时间来将数据存储到MC/SRAM,然后取回PDP进行池化处理。

上表中,最小case大多数下小于7KBytes,因此,为了平衡性能,将共享行缓冲区大小设置为7kBytes。

对于读DMA缓冲区,确定其大小有两个限制,一个是涵盖MC访问延迟,假设为128个周期。另一个是接入带宽,峰值性能的情况下是每个周期8字节(int8中8个元素,int16/fp16中4个元素)。所以读DMA缓冲区的大小是128×8 = 1kBytes。

功耗

NVDLA 1.0中池层的平面处理子单元目标,根据对当前网络的分析,平面处理使用率预计不会很高。

根据池层数百分比,平面处理子单元很可能大部分时间处于空闲状态。因此,子单元级时钟门控非常重要。