ISE14.7后仿真、烧录教程

ISE14.7后仿真、烧录教程

系统版本:win10,EDA工具版本:ISE14.7,modelsim SE 10.4,本文主要包含两部分内容,首先是基于ISE的后仿真,基于ISE和modelsim的联合后仿真,然后是基于ISE的烧录固化教程。

基于ISE的后仿真

声明:本文提到的后仿真是布局布线Implement后的后仿真,综合synthesize后的后仿真和Implement之后的后仿真不同,请注意。

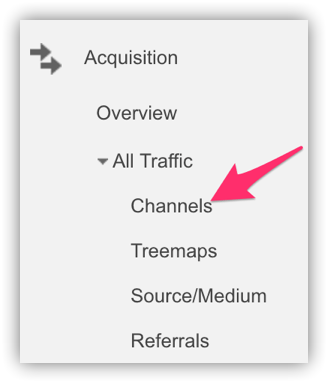

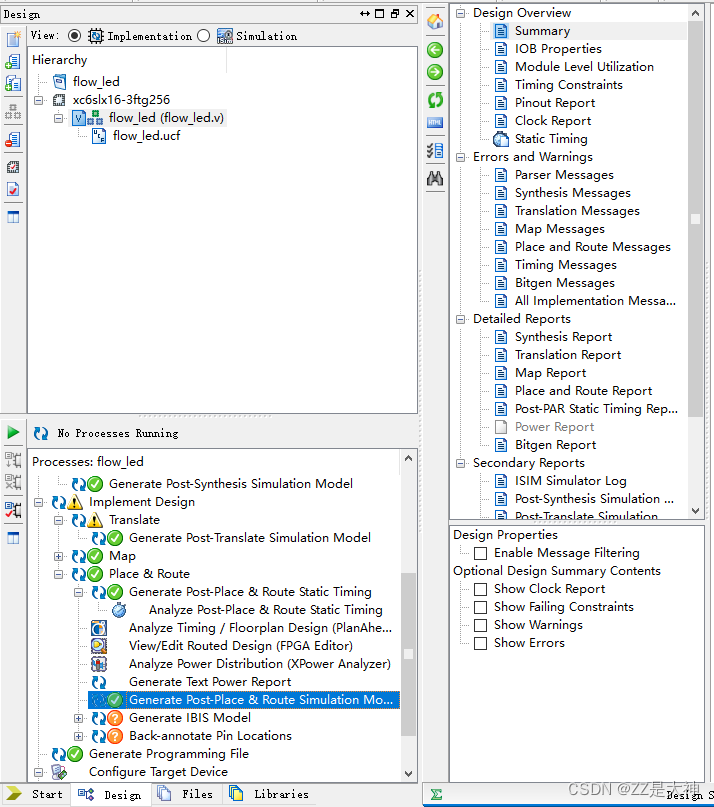

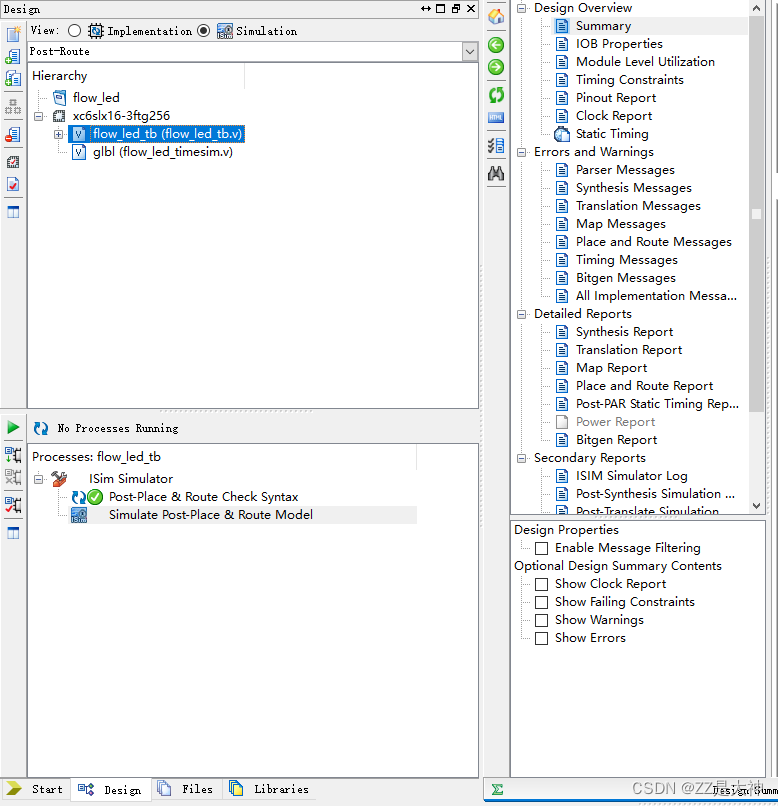

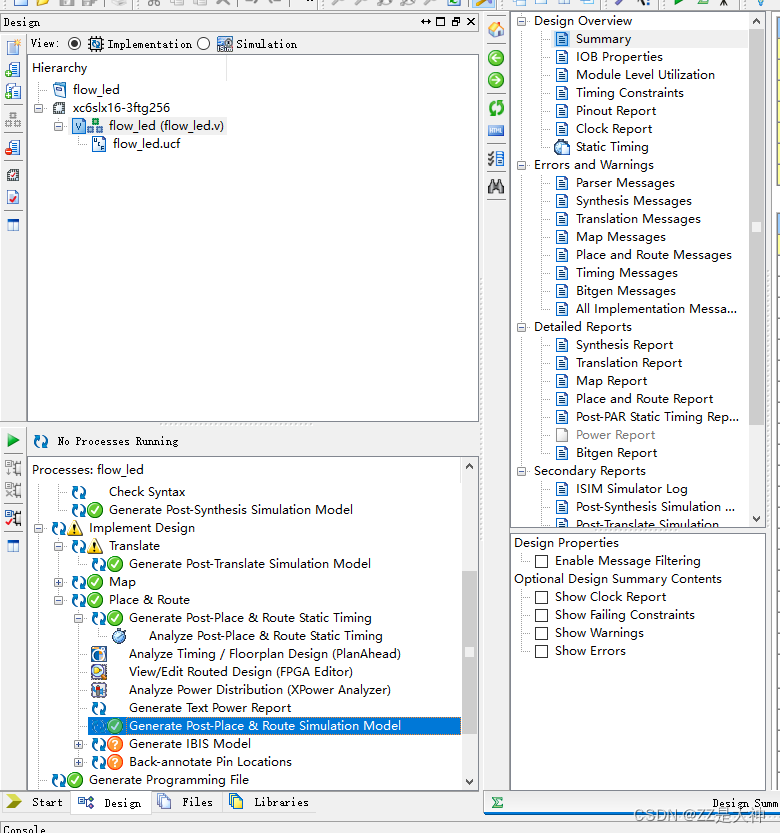

在进行后仿真之前要确保verilog.v文件通过Implement Design,其中 Generate Post-Place & Route Simulation Model系统默认不运行,需要手动运行,运行成功之后,选择simulation

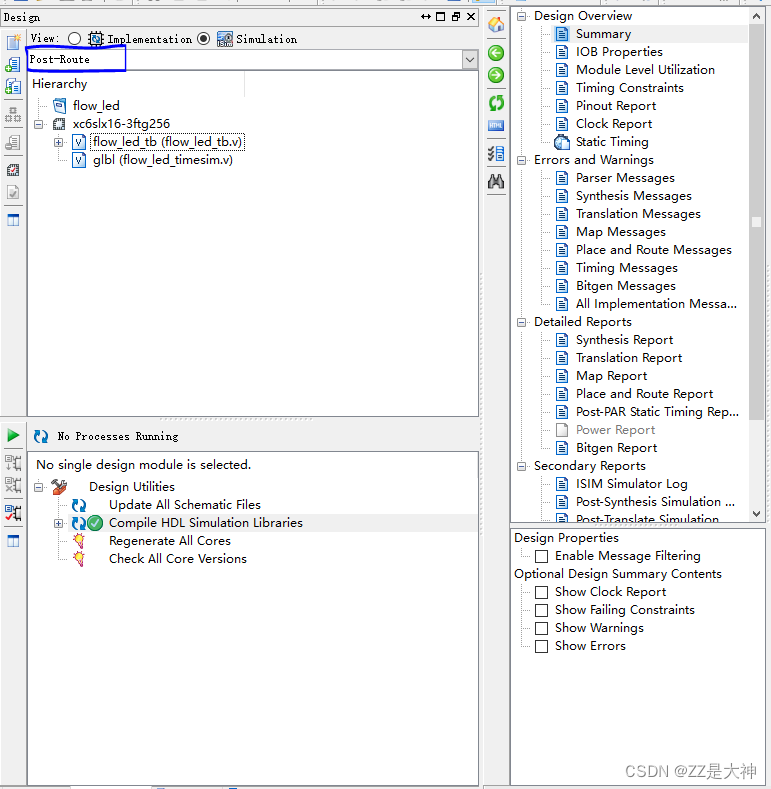

选择下拉框,选中Post-Route,即可进行布局布线后的后仿真。在仿真之前需要添加testbench文件,并对文件进行编译,编译通过后点击Simulate Post-Place & Route Model即可进入ISE自带的ISIM仿真波形界面

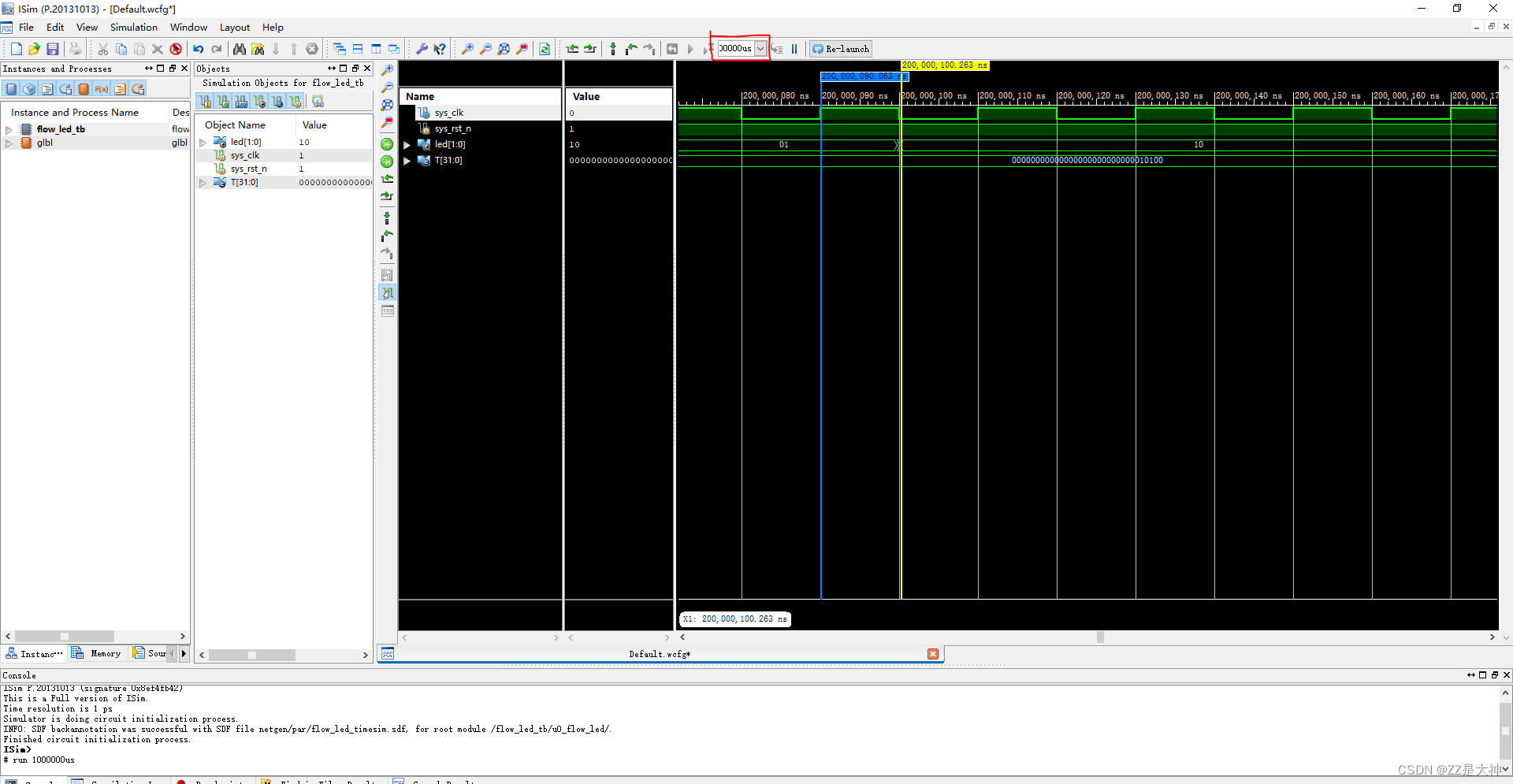

红色框设置仿真时长,仿真时长也可以在testbench文件中定义,通过finial语句结束仿真,可以从仿真波形结果中看出,输出波形和时钟上升沿存在约10ns延迟,并且输出信号存在电平不稳定的一段毛刺。

基于ISE和Modelsim联合后仿真

前仿真的方法比较简单,主要用于逻辑验证,后仿真不仅验证逻辑,还需要时序文件,因此后仿真需要支持FPGA的库文件,sdf反标时序文件,verilog.v文件编译后的.v文件,以及testbench文件。

基于ISE和Modelsim联合后仿真虽然复杂,但是modelsim的仿真性能更好,最直观的体验就是ISE自带的ISIM软件仿真1s需要大约几分钟,Modelsim仿真速度更快,因此在FPGA的开发中,modelsim常常被使用。

库文件编译

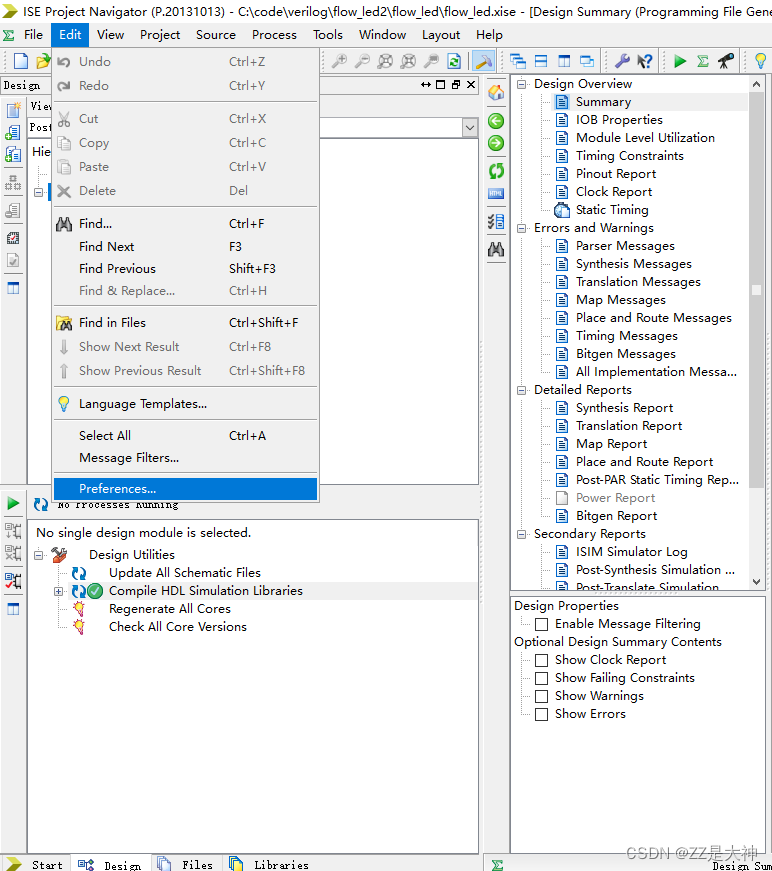

ISE自带的Xilinix库文件并不能被modelsim直接调用,需要使用modelsim对这些库文件进行编译,具体操作步骤如下:

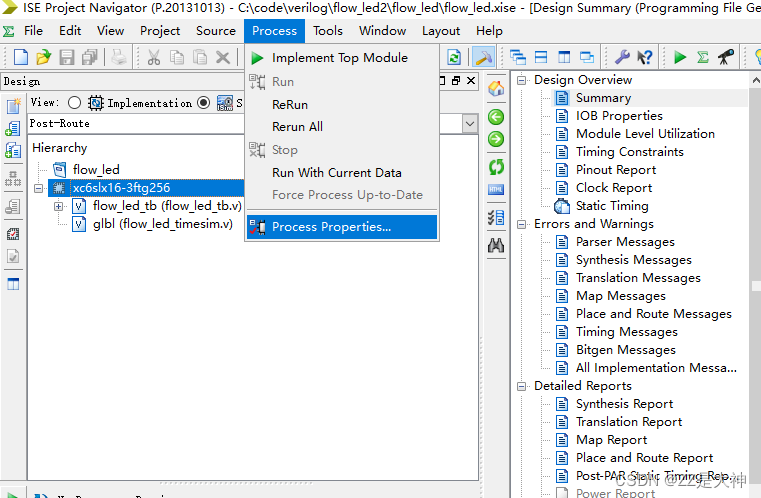

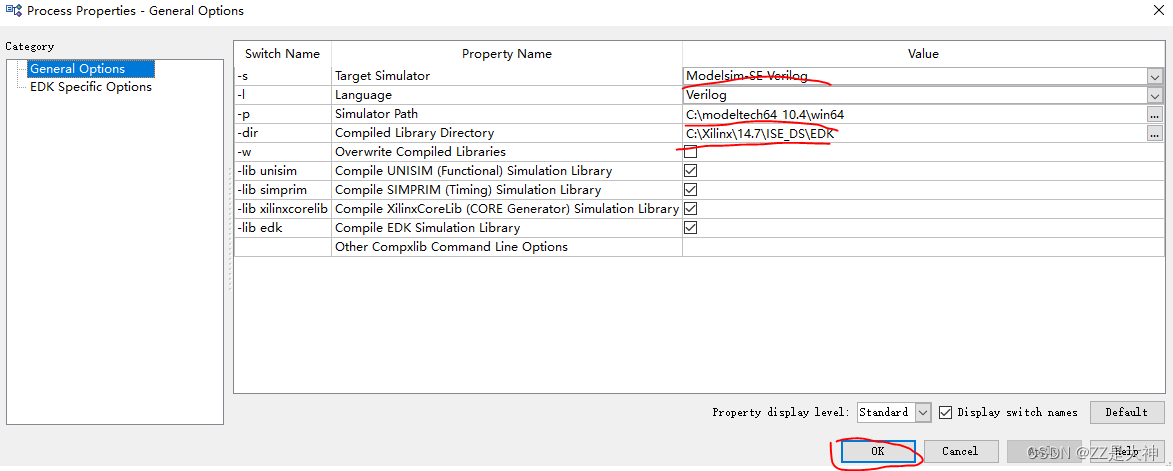

将Modelsim的路径添加到ISE中

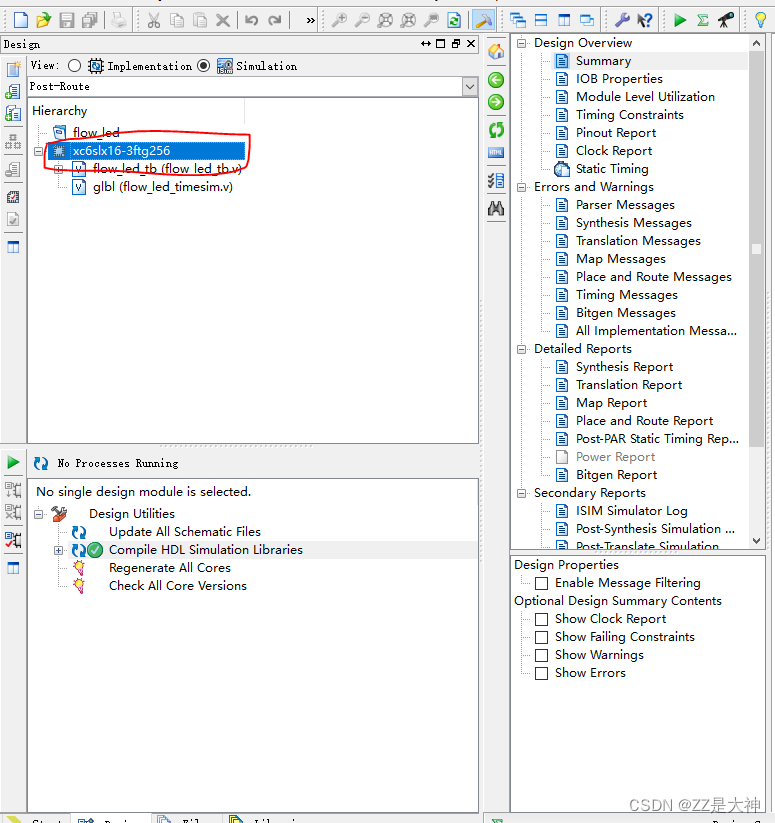

选中芯片库文件

使用Modelsim编译器,EDK是编译库文件存储的文件夹

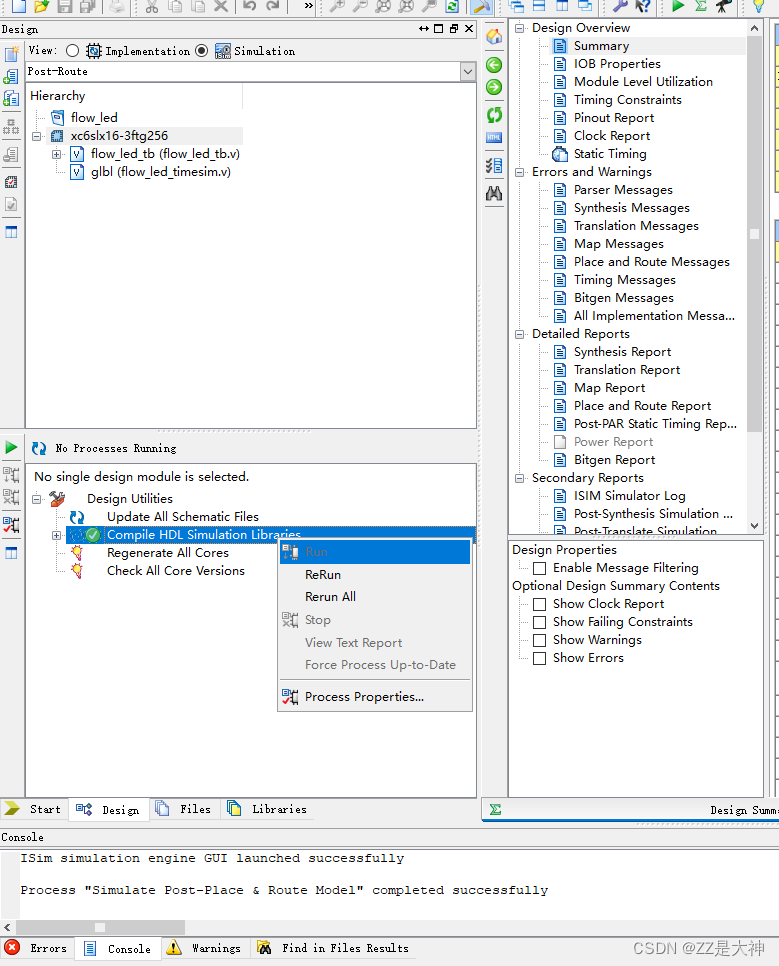

右键,run,开始进行库文件编译,编译需要20分钟,在Console中可以看到编译进程

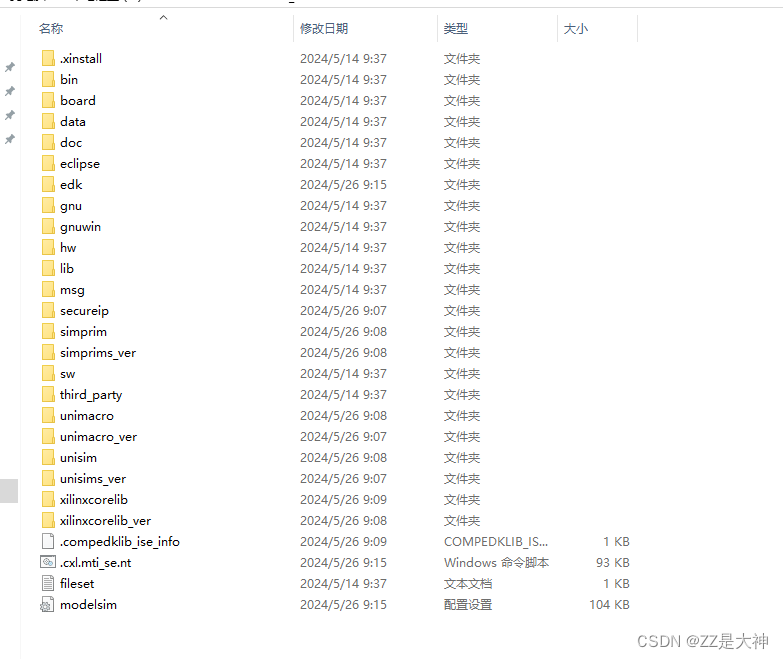

库文件,编译完成后,在EDK文件下可以看到新增了部分文件夹,这就是该型号FPGA芯片对应库文件编译后的文件

Modelsim中进行后仿真

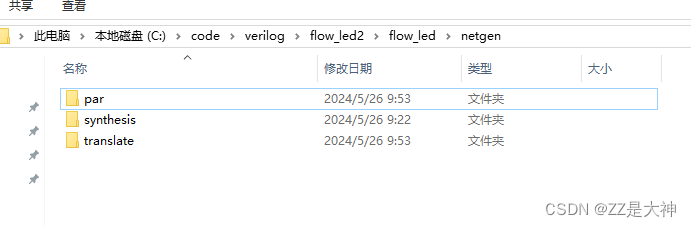

ISE在进行Generate Posr-Place这一操作后,会在工程文件夹/netgen文件夹下生成par文件夹

该文件夹下包含三个文件,其中SDF文件就是反标文件,包含布局布线后的延时参数,V文件就是RTL级V文件在编译后生成的由底层元件构成的V文件,在后仿真中,需要使用底层元件的V文件,testbench文件以及SDF文件

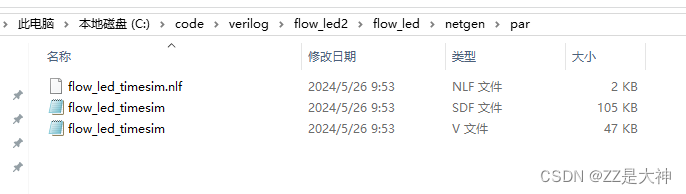

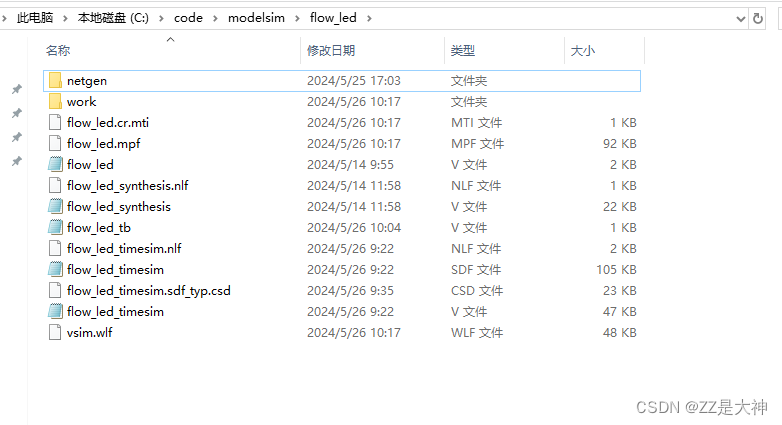

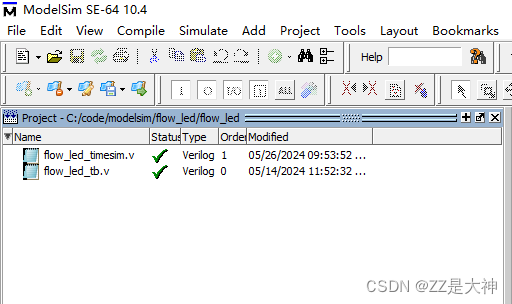

在进行modelsim仿真时,新建仿真工程文件,然后将netgen文件夹拷到modelsim工程文件目录下**,不然仿真会报错,netgen文件夹和modelsim工程文件夹中的word文件夹在同一目录下

在工程文件中添加testbench文件和使用底层元件的V文件,不是编写的RTL级的V文件,而是netgen/per文件夹下的V文件,编译通过后,进入work目录下

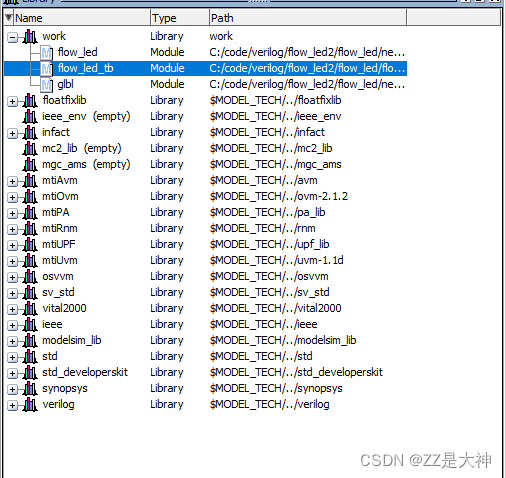

此时Work文件夹下包含三个文件,testbench文件,V文件和glbl文件

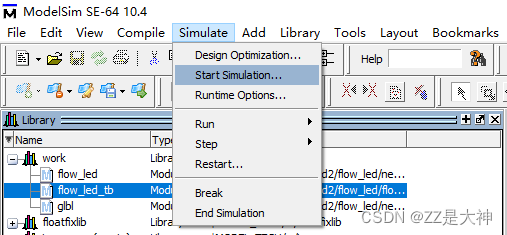

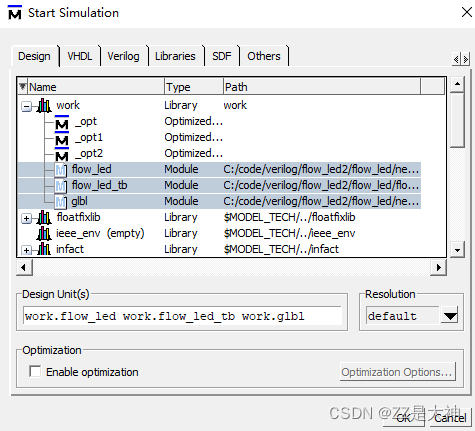

选中Design,添加work文件夹下的三个文件到Design Unit中,不要勾选Enable optimization

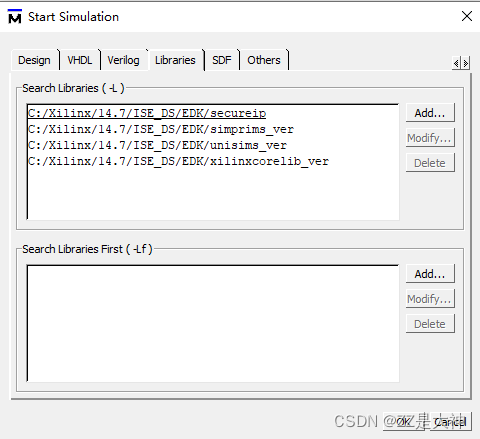

选中Library,将EDA文件夹下编译好的4个库文件导入

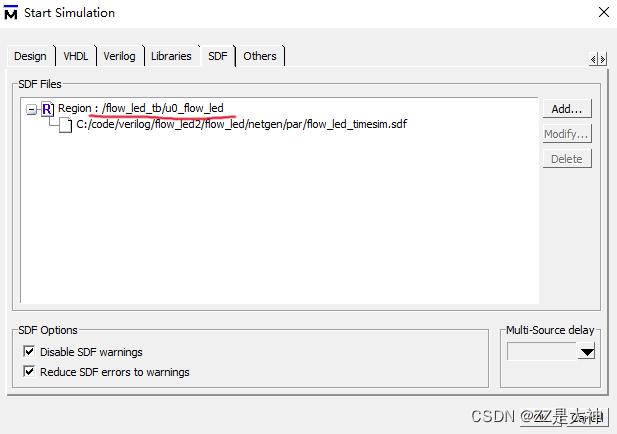

导入SDF文件,确保导入的SDF文件和Modelsim工程文件夹下拷贝的netgen/per文件下的SDF文件保持一致即可,切记要勾选Disable SDF wainings 和Reduce SDF errors ti wainings,不然会报错,点击OK,补充:region需要命名为/tb文件名/tb文件中的元件实体名,本项目tb文件中的元件实体名为uut

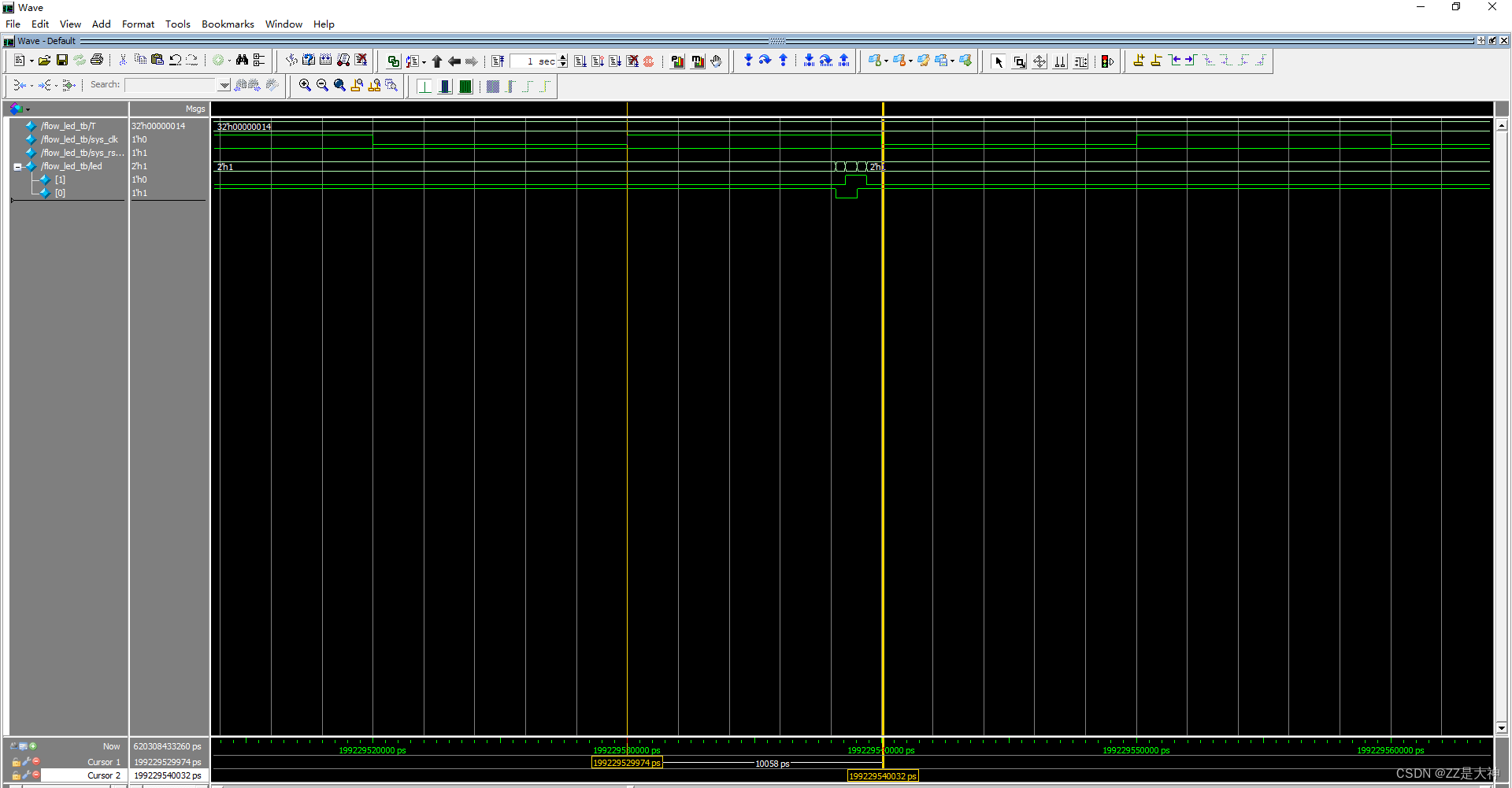

通过后仿真波形可以看出输出和时钟上升沿存在10ns延迟,并且输出存在明显的毛刺。

烧录固化

参考链接:https://blog.csdn.net/ciscomonkey/article/details/90142425

注释:仅供学习参考。