标签:PCB教程 PCB设计步骤 cadence教程 Allegro教程

以下是我学习该视频教程的笔记,记录下备忘,欢迎大家在此基础上完善,能回传我一份是最好了,先谢过。

备注:

1、未掌握即未进行操作

2、操作软件是15.5版本,若有修改则为16.5版本

3、1-25暂无笔记

正文:

26、非电气引脚零件的制作

1、建圆形钻孔:

(1)、parameter:没有电器属性(non-plated)

(2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要比drill hole大一点。

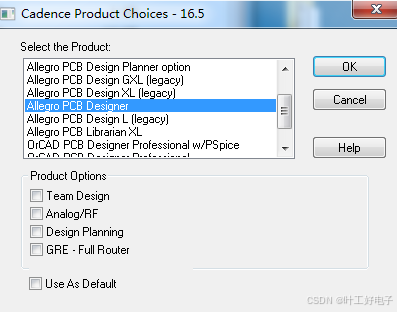

27、PCB电路板的建立

使用如下打开

主要内容:建立电路板及绘制相关区域

步骤:

0、建立电路板:File - New - 选择路径及Board

1、设置绘图区参数,包括单位,大小:Setup - Drawing Size

2、定义outline区域:Add - Line(Optons - Board Geometry - Outline)- (可使用命令模式输入坐标 x 0 0和ix iy)

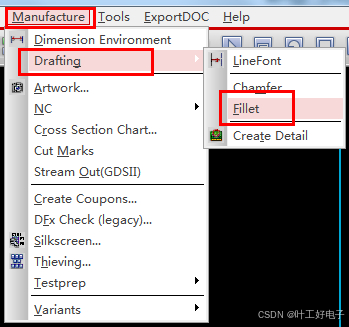

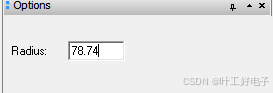

备注:添加导角(倒角):Manufacture - Dimension/Draft - Chamfer(方形导角)或者Fillet(圆形导角) - 左键依次选择需要导角的边。

16.5

3、定义route keepin区域:Setup - Areas - Route keepin - (可使用命令模式输入坐标 x 0 0和ix iy)(可使用Z-copy操作:Edit - Z-Cpoy - 在Options里subclass 中选择Route Keepin,contract:内缩,Expand:外扩,Offset:内或外的偏移数量 )

备注:一般大板子(空间够大):一般走线(route Keepin)限制在板框40mil以内,放置元件(package keepin)在80mil以内

route keepout 一般是用于螺丝孔,使用route keepout包围螺丝孔意味着该区域内不可布线。

4、定义package keepin区域:Setup - Areas - Package keepin - (可使用命令模式输入坐标 x 0 0和ix iy)(可使用Z-copy操作)

5、添加定位孔:place - manually - advance setting - 勾选Library - Placement List 中下拉框中选择Package Symbols或者Mechanical symbols中选择定位孔

28、Allegro PCB 的参数设置

主要内容:内电层的建立及其覆铜

Allegro定义层叠结构:对于最简单的四层板,只需要添加电源层和底层,

步骤如下:

1、Setup –> cross-section

2、添加层,电源层和地层都要设置为plane(内电层),同时还要在电气层之间加入电介质,一般为FR-4

3、指定电源层和地层都为负片(negtive)

4、设置完成可以再Visibility看到多出了两层:GND和POWER

5、铺铜(可以放到布局后再做)

6、Edit->z-copy –> find面板选shape(因为铺铜是shape) –> option面板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape:动态覆铜)- 左键选择图形(比如route keepin) - 完成GND层覆铜

7、相同的方法完成POWER层覆铜

补充:Allegro生成网表

1、重新生成索引编号:tools –> annotate

2、DRC检查:tools –> Design Rules Check,查看session log。

3、生成网表:tools –> create netlist,产生的网表会保存到allegro文件夹,可以看一下session log内容。

29、网表的导入

主要内容:网表导入,栅格设置及 drawing option的介绍

1、file –> import –> logic –> design entry CIS(这里有一些选项可以设置导入网表对当前设计的影响)

2、选择网表路径,在allegro文件夹。

3、点击Import Cadence导入网表。

4、导入网表后可以再place –> manully –> placement list选components by refdes查看导入的元件。

5、设置栅格点,所有的非电气层用一套,所有的电气层(ETCH)用一套。注意手动放置元件采用的是非电气栅格点。

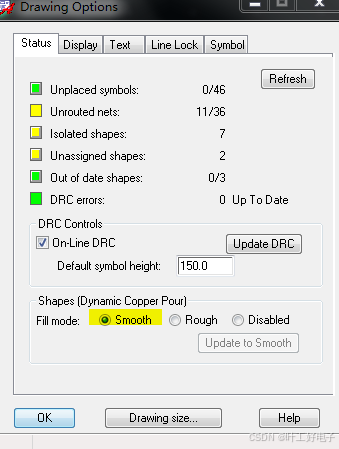

6、设置drawing option,status选项会显示出没有摆放元件的数量,没有布线的网络数量

30、PCB手动布局

1、place –> manully –> components by refdes可以看到工程中的元件,可以利用selection filters进行筛选。另外也可以手工摆放库里的元件。还可以将对话框隐藏(hide),并且右键 –> show就可以显示了。

2、如何镜像摆放到底层?

方法一:先在option选mirror,在选器件

方法二:先选器件,然后右键 –> mirror

方法三:setup –> drawing option –> 选中mirror,就可进行全局设置

方法四:对于已摆放的零件,Edit –> mirror在find面板选中symbol,再选元件

这样放好元件后就会自动在底层。

3、如何进行旋转?

方法一:对于已经摆放的元件,Edit –> move 点击元件,然后右键 –> rotate就可以旋转

方法二:摆放的时候进行旋转,在option面板选择rotate

35、Allegro快速摆放元件

1、开素摆放元件:place –> quickplace –> place all components

2、如何关闭和打开飞线?

关闭飞线:Display –> Blank Rats –> All 关闭所有飞线

打开飞线:Display –> Show Rats –> All 打开所有飞线

3、快速找器件:Find面板 –> Find By Name –> 输入名字

33、34、按照ROOM属性布局上+下(可跳过,不常用)

主要内容:添加ROOM属性,并放置元件

主要步骤:

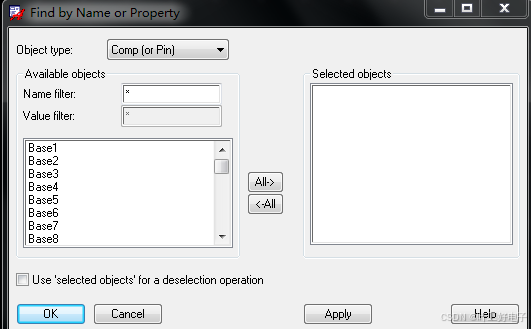

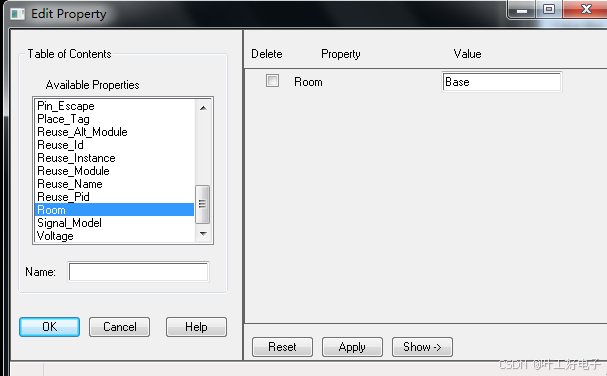

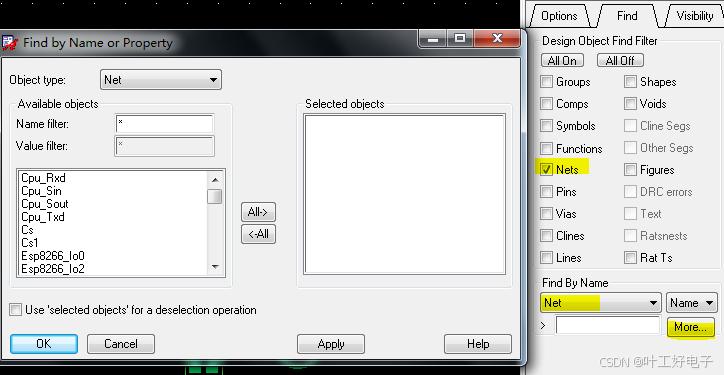

1、元件添加ROOM属性:Edit - Properties (在Find 中 Find By name 点击More)出现如下

挑选需要设置的元件,点击Apply,选择ROOM属性,并设置value

2、添加ROOM区间:Setup - Outline - RoomOutline - 画区域 - 点击RoomOutline中的OK

3、通过Room方式快速放置元件:Quickplace - place by room - 挑选需要的Room或者All Room

4、通过原理图添加元件ROOM属性:选中元件 - 右键 - Edit property - FilterBy中选择Cadence Allegro - ROOM - 设置名字

35、快速布局

主要内容:一次性摆出所有元件(较为常用)

1、快速放置步骤;place - QuickPlace - Place All component - 放置位置比如TOP还是Bottom等(Edig/Board side)

补充(16.5)交互布局

必须从原理图导出来的PCB才可以,选中原理图元件(可以使用filter选择只选元件part),在PCB editor中要是MOVE命令的状态,之后就可以移动在原理图中的元件了。可以一个模块一个模块的方式进行选择,与移动,与room相似,但是不需要设置。

2、关闭鼠线步骤:Display - Blank Rats - All

3、快速查找元器件步骤:Edit - Move - Find(选择symbol for pin)- 输入位号

36、PCB元件的基本操作

1、摆放的方法:Edit –> move或mirror或rotate

2、关于电容滤波,当有大电容和小电容同时对一点滤波时,应该把从小电容拉出的线接到器件管脚。即靠近管脚的为最小的电容。

3、各层颜色设置:top –> 粉色;bottom –> 蓝色;

37、约束规则的设置概要

主要内容:介绍约束规则

1、约束的设置:setup –> constrains –> set standard values 可以设置线宽,线间距。间距包括:pin to pin、line to pin、line to line等

2、主要用spacing rule set(线与线间距等) 和 physical rule set(线宽与过孔设置)

38、39、约束规则设置具体方法

主要内容:具体设置

1、设置新的线宽约束规则:setup –> constrains –> (Physical)set values - 添加新的名字以及所需Via

2、给网络设置属性并添加约束规则:Edit - properties - 在Find中如下设置,并点击more,挑选相应Net

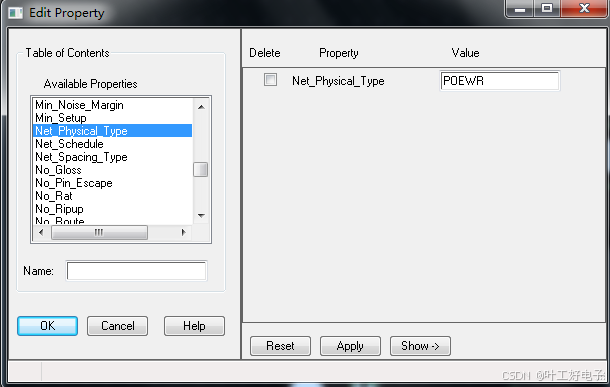

点击Apply - 出现如下窗口如下设置,点击OK完成属性配置

3、Net属性与规则相关联:setup –> constrains –> (Physical)assignment table - 在Physical constrains set 中下拉选择需要的规则(线宽选择net physical type,空间间距选择Net Spacing type) - 设置名(推荐命名:LW_ 、 SPACE_) - 点击 apply 点击OK

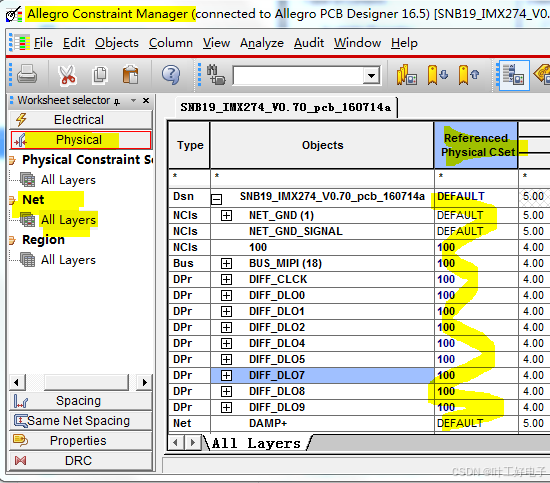

补充(16.5):2,3两步可以使用一步完成

可以使用Constraint Manager

4、设置空间间距规则:setup –> constrains –> (Spacing rule set)set values - 设置值(一般Pin to Pin不变,其余按要求修改)

5、在进行设置时,注意在Constrain Set Name选择Default。这样只要是没有特殊指定的网络,都是按照这个规则来的。

6、一般设置规则:pin to pin为6mil,其他为8mil。

7、Phsical Rule中设置最大线宽,最小线宽,颈状线(neck),差分对设置(这里设置的优先级比较低,可以不管,等以后专门对差分对进行设置),T型连接的位置,指定过孔

8、添加一个线宽约束:先添加一个Constrain Set Name,在以具体网络相对应。

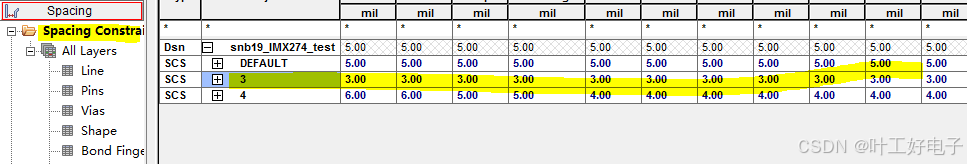

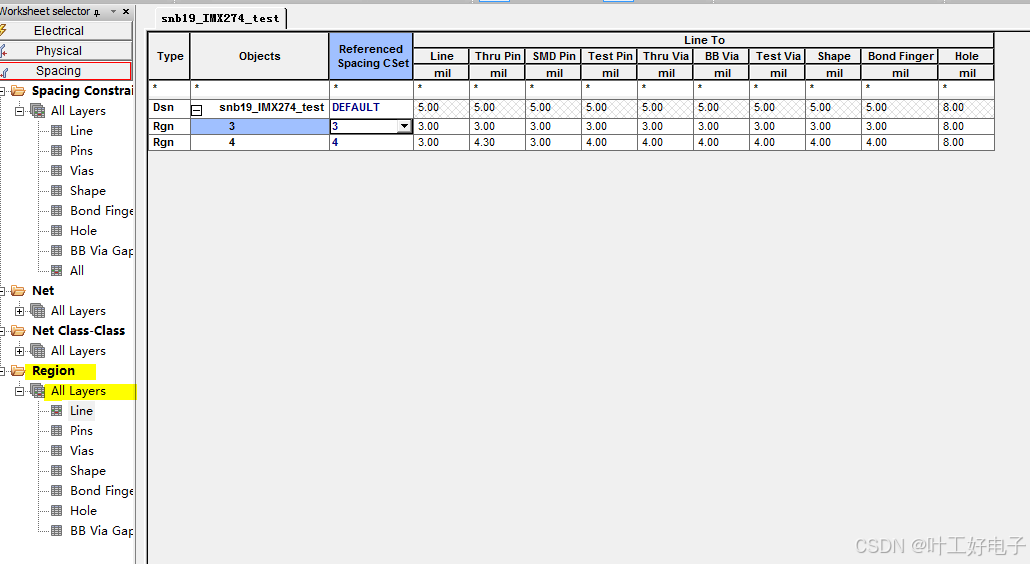

40、区域规则设置

主要内容:设置特殊区域,并对于某一个区域进行特殊约束,比如BGA

作用:有些区域规则与整体板子要求不同,需要设置与整体板子不同的空间规则,物理规则等,此时就需要特殊处理

1、设定特定区域的规则,例如,对于BGA器件的引脚处需要设置线宽要窄一些,线间距也要窄一些。

2、设定特定区域具体步骤:setup –> constraints –> constraint areas –> 选中arears require a TYPE property –> add 可以看到options面板的class/subclass为Board Geometry/Constraint_Area –> 在制定区域画一个矩形 –> 点击矩形框,调出edit property –> 指定间距(net spacing type)和线宽(net physical type) 并创建名字 - 点击apply和OK –> 分别在Spacing rule set 和 Physical rule set中的assignment table进行指定

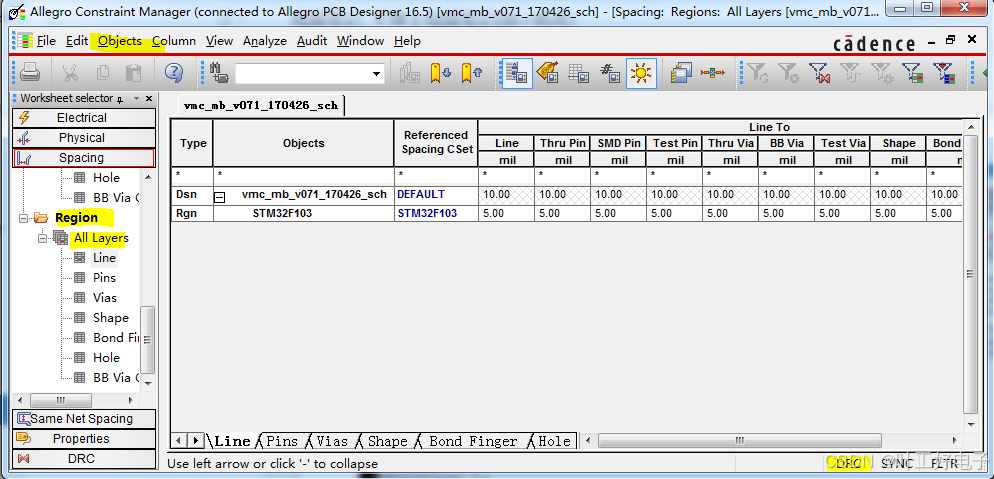

备注:16.5 设定区域具体步骤

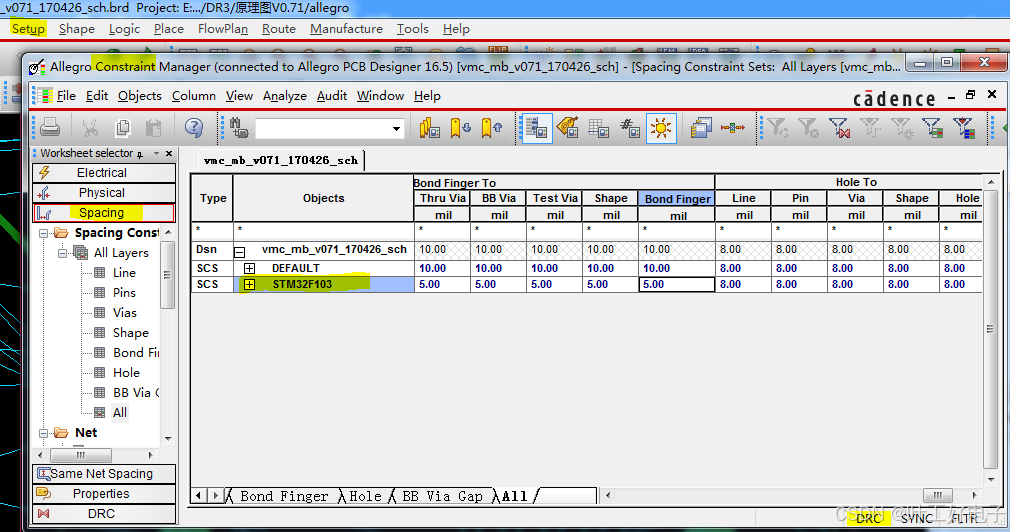

先设定区域里的规则:以spaceing 为例 setup -》constrain -》spacing ,右键DEFAULT,点击Create-》Spacing CSSET,如下图所示

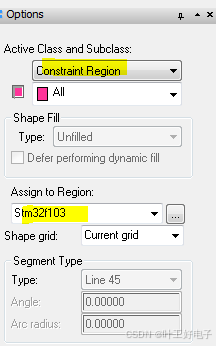

建立后,建立特殊区域,以spacing为例

选择region -》选中all layers ,点击Object -》Create-》region 输入region名字:STM32F103,在referenced spacing cset下拉中选择STM32F103

建立region区

shape -》rectangle -》选择如下图所示,即可。

41、XNet和总线的创建

主要内容:如何进行创建总线及XNet

作用:比如DSP和RAM的地址总线和数据总线需要进行约束或者进行等长处理,仿真的前期操作。

备注:在PCB设计布线前期,需要对BUS线进行等长约束规则设计,或者在PCB仿真时都需要进行XNET的设置。为什么要进行XNET的设置,是因为:在PCB设计中,很多信号线不都是从始端终端的,中间要经过很多的电阻、电容这样的阻容类元件,我们需要设置XNET来使得阻容元件两边的不同名的NET合并为一个XNET,这样以便于对于NET等长的设置。

1、打开约束管理器(electronical constraint spreadsheet):Setup - electronical constraint spreadsheet

2、显示指定网络飞线:Display –> show rats –> net 然后在约束管理器中选择要显示的网络

3、如果要设置等长线,但是在线上有端接电阻,那么需要进行设置(x net),使得计算的时候跨过端接电阻。这就需要为每一个端接电阻设置仿真模型库,设置完成以后,就可以在约束管理器中的看到网络变为了x net

4、添加信号仿真模型库:Analyze –> SI/EMI Sim –> Library 添加模型库 –> Add existing library –> local library path

5、对每个新建添加模型:Analyze –> SI/EMI Sim –> Model 会显示出工程中的器件,然后为每个器件添加仿真模型。对于系统库里面的元件有自己的模型库,可以利用Auto Setup自动完成。对于系统库里面没有的模型,选择find model

6、在约束管理器中,点击object –> 右键,即可利用filter选择需要选择的网络,可以选择差分对,x net等。

7、创建总线:在约束管理器中,选择net –> routing –> wiring 然后选择需要创建为总线的网络 –> 右键,create –> bus

42、43、网络拓扑结构的建立

主要内容:创建网络拓扑结构及约束

作用:比如说DSP的地址线需要连接Flash和SDRAM,这时候的连接时个T型结构,此时需要设置T点到Flash和SDRAM的距离相等或者一些别的约束比如阻抗等,就需要用到网络拓结构

1、方法一:使用约束管理器:步骤较多,需要使用时进行视频回顾

2、方法二:使用sigxplorer:使用到在回顾

44、线长约束规则设置

主要内容:设置线长

作用:一般用于地址线,数据线等

1、对线长的要求,实际就是设置延时,可以按照长度来设置,也可以按照延时来设置

2、打开约束管理器 –> Electronic constraint set –> All constraint –> User – defined 选择在设置拓扑结构时设置好的网络 –> 右键选择SigXplore –> 在pro delay里选择。也就是说如果要想设置线长约束,需要先定义一个拓扑结构,然后再指定这个拓扑结构的网络约束。

45、相对延迟约束规则设置(即等长设置)

1、在设置相对延迟约束之前也需要先建立拓扑约束

2、在拓扑约束对话框 –> set constraint –> Rel Prop Delay 设定一个新规则的名称 –> 指定网络起点和终点 –> 选择local(对于T型网络的两个分支选择此选项)和global(对于总线型信号)

47、布线准备

主要内容:布线前的一些准备设置

作用:方便布线

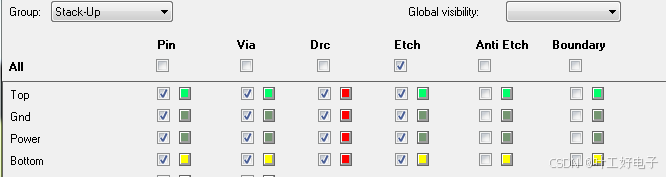

1、设置颜色:Display –> color/visibility 其中group主要设置:stack-up,geometry,component,area

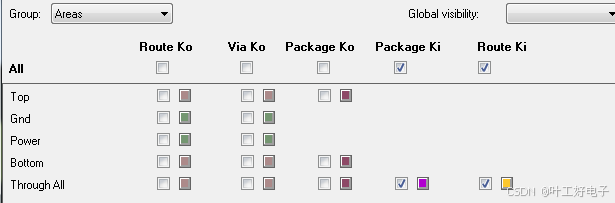

一般勾选如下

2、对电源与地鼠线处理(不显示电源与地鼠线,因为以后可直接打过孔到内电层):Edit - Properties - 在Find中选择Net,点击more - 挑出VCC和GND的所有网络 - Apply - 在Edit Property中选择Ratsnest_Schedule - 下拉框中选择Power and Ground - Apply - OK

3、高亮设置:Display –> color/visibility –> display选项:temporary highlight(暂时高亮)和permanent highlight(永久高亮) 然后再在display –> highlight选择网络就可以高亮了。

但是此时高亮的时候是虚线,可能看不清,

可以在setup –> user preferences –> display –> display_nohilitefont 打开此选项 也可以设置display_drcfill,将DRC显示也表示为实现,容易看到。

DRC标志大小的设置在setup –> drawing option –> display –> DRC marker size

4、布局的时候设置的栅格点要大一些,在布线的时候,栅格点要小一些

5、执行每一个命令的时候,注意控制面板的选项,包括option,find,visibility

6、不同颜色高亮不同的网络:display highlight –> find面板选择net –> option面板选择颜色,然后再去点击网络。一般选择VCC和GND,方便用于划分块和一些布线。

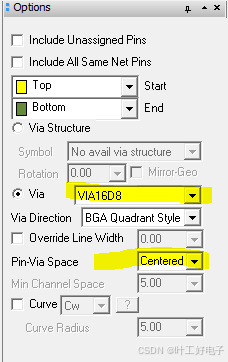

48、Fanout 操作(以下方法是16.5)

方法一

1、Route - Create Fanout

2、选择过孔和位置

3、出现很多DRC错误,因为要设置region(在BGA区域框选起来做特殊规则处理)

4、setup - Constraints - Spacing(创建一个3的约束,实际至少要4以上,要不然厂家工艺不行)

5、在region中建立一个3,在CSet中选择3

6、建立region区域

shape - rectangle -

框选BGA部分即可。

方法二

route - PCB router - fanout by pick 右键 setup

49、50、手工布线

主要内容:

作用:走线及走线菜单option介绍

1、走线:Route - Connect

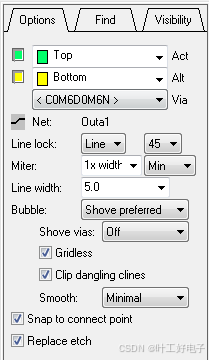

2、菜单option介绍

Via:在物理规则中设置的过孔(COM6D0M6N)

Line Lock:拐角是直线还是弧线,45表示角度

Miter:控制转角大小,可直接输入2X,3X等

line width;线宽,可直接输入数值修改线宽

Bubble:

Hug only:环抱

shove preferred 推挤

Hug preferred:遇到障碍物优先选择报警

Shove vias:

Off:不允许推挤过孔

Minimal:

Full:都可推开过孔

Snap to connect point:连接引脚中心

Replace etch:替换走线

3、换层:双击可出现过孔

4、简易走线可自动布线:选择Net(左键单击引脚) - 右键 Finish

5、控制出线方向:选择Net(左键单击引脚) - 右键 Toggle(开关)

问题:过孔种类选择??什么依据

Toggle经过操作后还是不知什么情况下使用它??

51、总线走线

52、高速信号走线

主要内容:设置延时窗口和走线长度窗口

作用:方便布线是实时检查

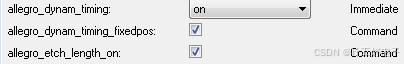

1、设置用户自定义相关窗口:Setup - User Preference Editor - 在categories 选择Etch - 在categories.Eych中选择

第一个是打开动态显示时间窗口,第二个是固定动态显示时间窗口,第三个是打开走线长度实时显示窗口

备注:如果Net未设置最大延时(最大走线)不会显示动态延时时间

53、差分布线

0、差分线设置:在setup - Constraints - electrical中,设置新route,新建object,在差分对栏设置Static Phase Tolerance和Min Line Spacing,然后在Net的route中将差分线组合成差分对,再将之间的设置的object名填入到Referenced Electrical CSet中即可。

1、差分线走线:route –> conect然后选择差分对中的一个引脚,如果已经定义了差分对,就会自动进行差分对布线。

2、如果在差分布线时想变为单端走线,可以点击右键:single trace mode

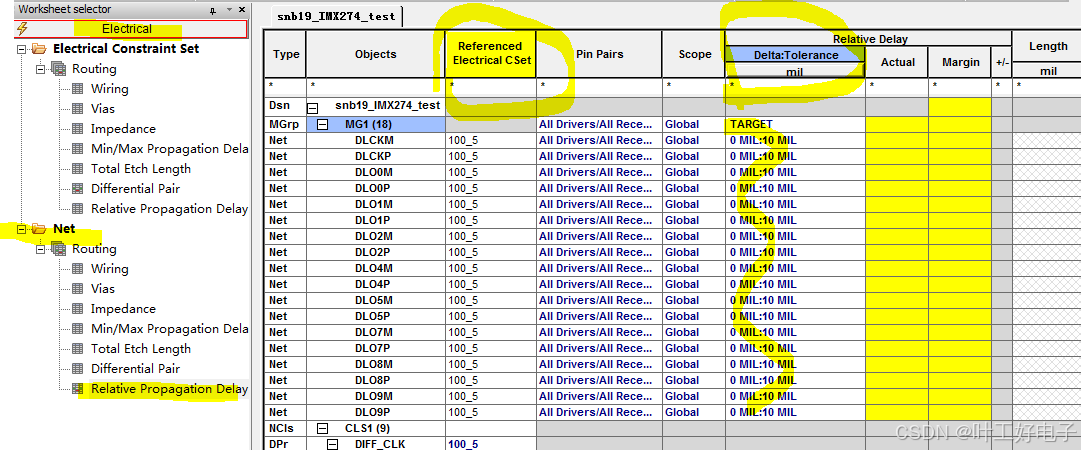

3、设置等长(补充)match group

setup - Constraints - electrical - net - Referenced Electrical CSet - 选中所有差分对(需要绕等长的,使用Ctrl键多选)- 右键 create - match group,在Delta:Tolerance一栏中填写误差,先选择时钟线做参考,在Delta:Tolerance中填写target,在其余填写误差0mil:10mil如下图。

当右边(Actual和Margin)绕为绿色时即表示OK。

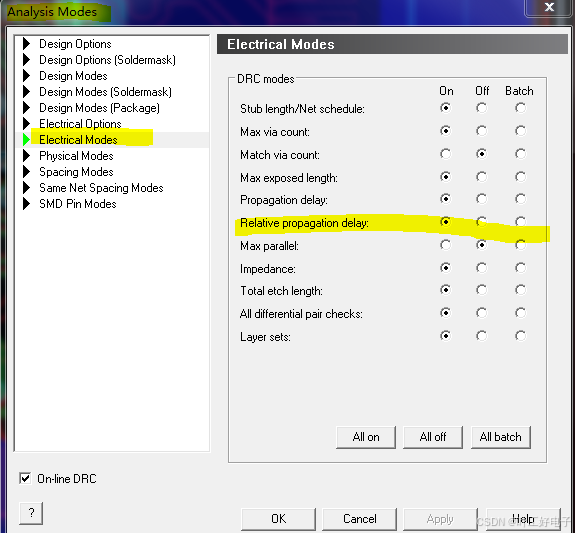

注意:要让右边绿色必须要如下设置 setup - Constraint - mode

54、蛇形走线

1、群组走线:route –> 选择需要布线的飞线这样就可以多根线一起走线了 –> 但快到走线的目的焊盘时,右键 –> finish 可以自动完成 –> 再利用slide进行修线

2、常用的修线命令:

(1)、edit –> delete 然后再find中可以选择Cline(删除整跟线)、vias、Cline Segs(只删除其中的一段)

(2)、route –> slide 移动走线

(3)、route –> spread between voids 并在控制面板的options栏输入void clearance即可进行自动避让。

55、铺铜

主要内容:讲述铺铜的相关操作

铺铜的作用:PCB的敷铜一般都是覆地铜,增大地线面积,有利于地线阻抗降低,使电源和信号传输稳定,在高频的信号线附近敷铜,可大大减少电磁辐射干扰,起屏蔽作用。总的来说增强了PCB的电磁兼容性。另外,大片铜皮也有利于散热。

孤岛:孤立的铜皮,应该删掉的,留着会引起层间电磁震荡(待考证),引发信号完整性问题

正片不用考虑Flash,为什么要使用负片呢?

0、可以使用Z-Copy进行整层铺铜。

1、建议初学者内电层用正片,因为这样就不用考虑flash焊盘,这时候所有的过孔和通孔该连内电层的就连到内电层,不该连的就不连。而如果用负片,那么如果做焊盘的时候如果没有做flash焊盘,那么板子就废了。

2、在外层铺铜:shape –> rectangular 然后再option中进行设置

(1)、动态铜(dynamic copper)

(2)、制定铜皮要连接的网络

3、铺铜后如何编辑边界:shape –> edit boundary ,选中铜皮(会高亮),就可以对铜皮就行修改边界

4、如何删除铜皮:edit –> delete –> 在find中选择shape –> 点击铜皮就行删除

5、修改已铺铜的网络:shape –> select shape or void –> 点击铜皮,右键assign net

6、如何手工挖空铜皮:shape –> manual void –> 选择形状

7、删除孤岛:shape –> delete islands –> 在option面板点击delete all on layer

8、铺静态铜皮:shape –> rectangular –> 在option面板选择static solid

9、铜皮合并,当两块铜皮重叠了以后要进行合并:shape –> merge shapes 逐个点击各个铜皮,就会合并为一个铜皮。合并铜皮的前提是铜皮必须是相同网络,别去铜皮都是一种类型(都是动态或者都是静态)

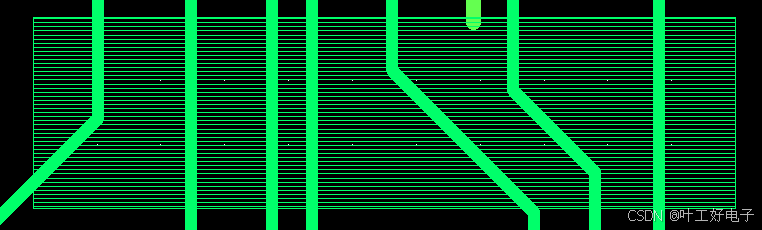

问题:铺铜效果如下,与正常不同

解决方法:Setup - Draw options

56、内电层分割

主要内容:內电层分割步骤

问题:不同的电源与电源之间的铜箔间距怎么定?电源差值与铜箔间距的距离依据什么??

1、在多电源系统中经常要用到

2、在分割前为了方便观察各个电源的分布,可以将电源网络高亮显示:Display - Height light - 在Options中选择颜色,在Finde中选择Net

3、分割铜皮:add –> line –> 在option面板选择class为anti etch,subclass为power,制定分割线线宽(需要考虑相临区域的电压差),如果电压差较小,用20mil即可,但是如果是+12V与-12V需要间隔宽一些,一般40~50mil即可。空间允许的话,尽量宽一些。然后用线进行区域划分

4、区域net分配:edit –> split plane –> create 打开create split palne,选择要分割的层(power)及铜皮的类型 –> 制定每个区域的网络(完毕后可通过Display Visibility中关闭AntiEtch)

5、全部去高亮:display –> delight –> 选择区域

6、去除孤岛:shape –> delete island 可以将孤岛暂时高亮显示 –> 点击option去除孤岛

7、尽量不要再相邻层铺不用电源的铜皮,因为这样会带来电源噪声的耦合,在电源层之间要至少相隔一层非介质层

57、后处理

1、添加测试点

2、重新编号,便于装配。在原理图设计时时按照原理图中的位置进行编号的,但是这样在PCB中编号就是乱的。这就需要在PCB中重新编号,然后再反标注到原理图,步骤:Logic –> Auto Rename Refdes –> rename –> more 可以设置重新编号的选项 选择preserve current prefixes即保持当前的编号前缀。

3、最好是在布线之前,对元件进行重新编号,否则,如果是在布线完成后再重新编号,可能会带来一些DRC错误。有一些DRC与电气特性是无关的,可能是由编号引起的,这时就可以不管这些DRC错误。

4、在原理图中进行反标注:打开原理图工程文件 –> tools –> back annotate –> 选择PCB Editor –> 确定即可

5、布线完成后,进行完整的检查,检查可能存在的各种DRC错误

6、查看报告:tools –> report或者quick reports –> 最常用的是unconnect pin report(未连接引脚);还有查看shape的一些报告,检查动态铜皮的状态,如果有的状态不是smooth就需要到setup –> drawing option中进行更新 –> update to smooth

7、shape no net 即没有赋给网络的shape;shape island 检查孤岛;design rules check report

8、在setup –> drawing option中可以看到unrouted nets,unplaced symbol,isolate shapes等。这只是一个大致的统计信息。但是要求所有的选项都是绿色的,即都没有错误。

9、数据库检查:如果确定所有的设计都没有错误了,推荐进行一次数据库的检查,将错误完全排除掉。步骤:tools –> update DRC –> 选中两个选项 –> check 保证数据库是完整的

问题:数据库检查是出现 ILLEGAL NULL PAD

解决:运行tools/padstack/modify design padstack 选择purge/all把非法的PAD都清除掉试下

58、丝印处理(为出光绘做准备)

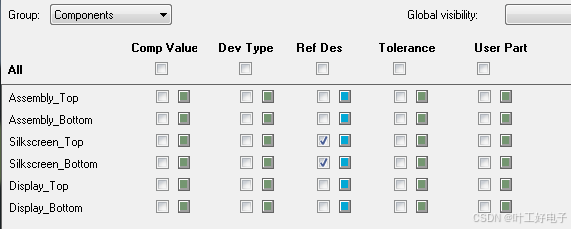

1、生成丝印层是,与电气层没有关系了,所以可以把走线以及覆铜都关闭:display –> color visibility 关掉etch,要留着pin和via,因为调整丝印时需要知道他们的位置。

2、在display –> color and visibility –> group选择manufacturing –> 选择autosilk_top和autosilk_bottom 因为丝印信息是在这一层的。不需要选择其它层的silkscreen

3、生成丝印:manufacturing –> silkscreen –> 选择那些层的信息放在丝印层,一般要选上package geometry和component reference designator –> 点击silkscreen,软件自动生成这个信息

4、调整丝印,先在color and visibility中关掉ref des assembly_top和assembly_bottom,及一些别的,只留下Pin,Via 和Autosilk_Top(比如先布顶层)

5、调整字体大小:edit –> change –> 在find面板选中text –> option面板选中line width和text block,不选择text just –> 画框将所有的文字改过来。line width是线宽,text block是字体大小。注意option选项中的subclass不要动,否则修改后,就会把修改结果拷贝到那一层了。

6、调整丝印位置:move –> 选择编号进行修改

7、加入文字性的说明:add –> text –> 在option中选择manufachuring/autosilk_top (按照公司的应该在Board 中的丝印层),以及字体的大小,然后点击需要添加的位置,输入即可

59、钻孔文件

主要内容:钻孔表格及文件的输出

作用:钻孔文件是电路板制作厂商数控机床上要用到的文件,后缀为.drl

1、、设置钻孔文件参数:manufacture –> NC –> NC Parameters –> 设置配置文件(nc_param.txt)存放路径,全部保持默认即可

2、产生钻孔文件:manufacture –> NC –> NC drill –> Drilling:如果全部是通孔选择layer pair;如果有埋孔或者盲孔选择(by layering)—> 点击drill就可产生钻孔文件 –> 点击view log查看信息

备注:注意NC drill命令只处理圆型的钻孔,不处理椭圆形和方形的钻孔,需要单独进行处理:manufacture –> NC –> NC route –> route 可能会产生一些工具选择的警告,可以不必理会。完成后会产生一个.rou文件

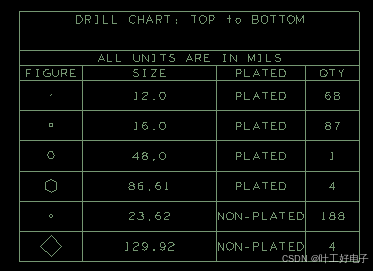

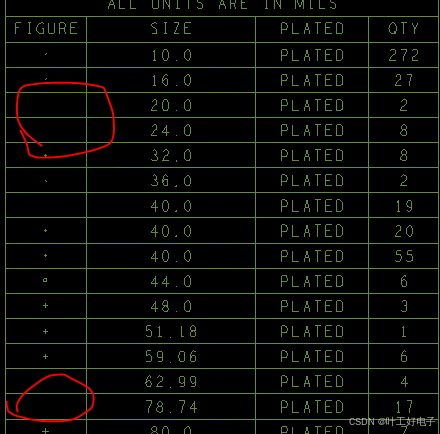

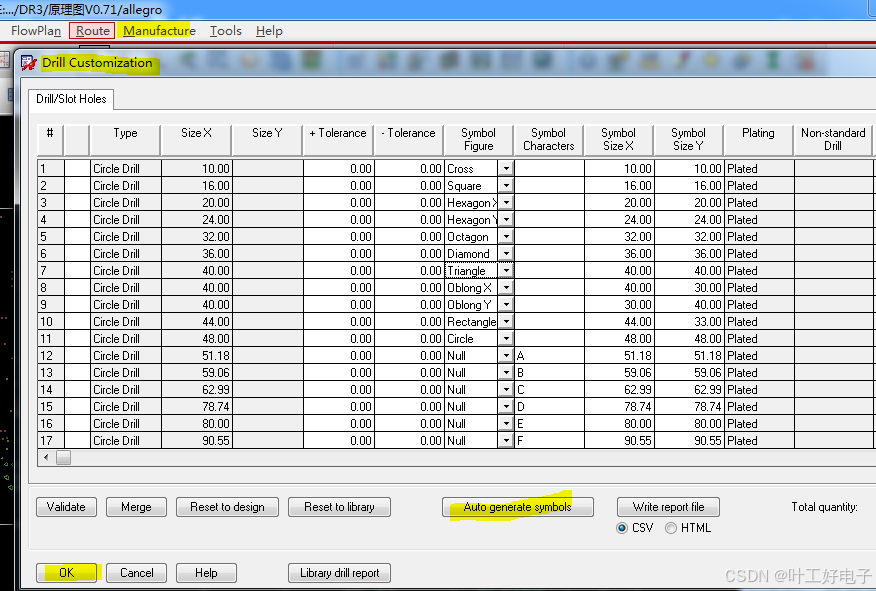

3、生成钻孔表和钻孔图:display –> color and visibility –> 关闭所有颜色显示,在geometry中单独打开outline,只打开电路板的边框 –> manufacture –> NC –> drill legend (铭文)生成钻孔表和钻孔图 –> ok –> 出现一个方框,放上去即可

问题:这个figure的选择以及作用未知??

是不是所有的过孔都能够出现在钻孔文件中?

会有出现没有实例的figure,设置:

设置:man ->NC ->Drill C ->Auto

重新放置钻孔表后:

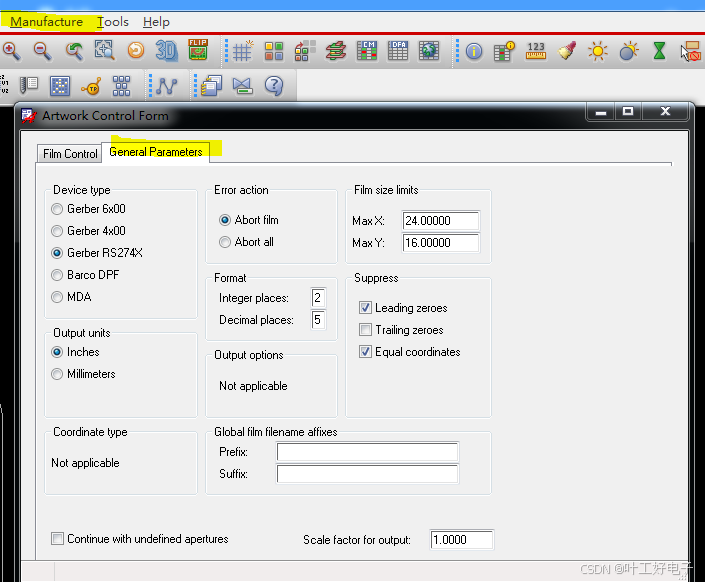

60、出光绘文件

1、出光绘文件:manufacture –> artwork,注意以下几个选项:

Film Control:

(1)、undefined line width:一般设置为6mil或者8mil(每一个图层上均要设置,否则可能不能够正常显示outline)

(2)、plot mode:每一层是正片还是负片(公司是使用正片,方便PCB,复杂厂家制板,厂家需要删除via,否则我们需要制作热焊盘)

(3)、vector based pad behavior:出RS274X格式文件时,一定要选中这个选项,如果不选这个选项,那么出光绘的时候,负片上的焊盘可能会出问题。

General Parameters:

(1)、Device type:选择Gerber RS274X,可以保证国内绝大多数厂商可以接受

2、在出光绘文件之前可以设定光绘文件的边框(也可以不设置):setup –> areas –> photoplot outline

3、如果要出顶层丝印信息的光绘文件,需要先把这一层的信息打开:display –> color/visibility –> all invisible 关掉所有。对于输出每一层最好都包括outline层。

4、对于顶层丝印层,需要打开以下三个选项:

geometry:[board geometry]: silkscreen_top [package geometry]: silkscreen_top

manufacturing:[manufacturing]: autosilk_top,component ->refdes(TOP),参考下图(最后)

然后,manufacture –> artwork –> film control –> 在available films中选择TOP,右键add –> 输入这个film的名字(例如silkscreen_top)这样就可以在available films中添加上了这个film,并且里面有刚才选择的三个class/subclass。检查下是否有自己绘制的丝印以及位号是否都在。

5、利用相同的方法,在产生底层的丝印

6、添加阻焊层,先在manufacture中添加上soldermask_top层,然后再在display –> color/visibility中选择一个几个class/subclass:

stack-up:[pin]: soldermask_top; [via]: soldermask_top

geometry:[board geometry]: soldermask_top; [package geometry]: soldermask_top

再在soldermask_top右键 –> match display 就会让这个film和选择的class/subclass进行匹配了

同样的办法添加底层阻焊层。

7、添加加焊层,先在manufacture中添加上pastemask_top层,然后再在display –> color/visibility中选择一个几个class/subclass:

stack-up:[pin]: pastemask_top; [via]: pastemask_top

geometry:[board geometry]: 没有; [package geometry]: pastemask_top

再在soldermask_top右键 –> match display 就会让这个film和选择的class/subclass进行匹配了

同样的办法添加底层加焊层。

8、添加钻孔表,先在manufacture中添加上drill_drawing层,然后再在display –> color/visibility中选择一个几个class/subclass:

manufacturing:[manufacturing]: Nclegend-1-4

geometry:[board geometry]: outline

再在drill_drawing右键 –> match display 就会让这个film和选择的class/subclass进行匹配了

9、板子需要的底片:

(1)、四个电气层(对于四层板)

(2)、两个丝印层

(3)、顶层阻焊层和底层阻焊层(solder mask)

(4)、顶层加焊层和底层加焊层(paste mask)

(5)、钻孔图形(NC drill lagent)

10、修改:如何在已经设定好的film中修改class/subclass:点击相应的film –> display就可以显示当前匹配好的class/subclass –> 然后再在display中修改 –> 然后再匹配一遍

11、需要对每个film进行设置film option,VCC和GND需要设置成负片形式(文件小),这里的正负片是针对底片来说的,之前在添加內电层是设置的正负片是针对shape来说的。

12、生成光绘文件:film option中select all –> create artwork

需要运行dbdoctor(tool - database check)

13、光绘文件后缀为.art

14、需要提供给PCB厂商的文件:.art、.drl、.rou(钻非圆孔文件)、参数配置文件art_param.txt、钻孔参数文件nc_param.txt

备注:有时候是更新PCB,出光绘会出现问题,查看allegro 中没有art_param.txt 文件,

方法:点击OK即可。

补充公司光绘包含的层(4层板为例)