【RISC-V设计-07】- RISC-V处理器设计K0A之CSR

文章目录

- 【RISC-V设计-07】- RISC-V处理器设计K0A之CSR

- 1.简介

- 2.顶层设计

- 3.端口说明

- 4.寄存器说明

- 5.代码设计

- 6.总结

1.简介

控制和状态寄存器(Control and Status Register,简称CSR)是用于控制和反映处理器核心状态及执行环境的特殊寄存器。RISC-V 架构中专门划分出了4K CSR 空间。这个单独定义的 CSR 空间为处理器的控制和状态管理提供了一个集中且明确的区域。它使得与处理器相关的各种配置和状态信息能够被高效地组织和访问。

其优势包括:

- 提高了系统的可扩展性:新的功能和特性可以通过在 CSR 空间中添加新的寄存器来实现,而不会干扰现有的指令集架构。

- 增强了编程的便利性:开发者能够通过统一的方式访问和操作与处理器相关的关键信息。

在 RISC-V 架构中,CSR 地址的划分具有明确的规则和特定的范围。

通常,CSR 地址被划分为不同的区域,以对应不同的功能和用途。一些地址范围可能被分配用于处理器的核心控制,如设置处理器的运行模式、中断控制等。另一些地址范围可能用于存储与性能监测相关的信息,如指令执行的周期数、缓存命中率等。

以常见的划分方式来说:

- 0x000 到 0x1FF 范围内的地址可能用于基本的处理器控制和状态信息。

- 0x200 到 0x3FF 可能用于与特定扩展功能相关的 CSR 。

但这种划分并非是绝对固定的,不同的 RISC-V 实现可能会根据具体的需求和设计进行微调。

在本设计中,CSR主要用于挂载核内中断控制器,通过这种方式,能够实现对外部中断输入的集中管理和控制。支持 16 个外部中断输入意味着系统具备了处理多种外部事件的能力。

2.顶层设计

3.端口说明

| 序号 | 端口 | 位宽 | 方向 | 说明 |

|---|---|---|---|---|

| 1 | core_clk | 1 | input | 内核时钟 |

| 2 | core_rstn | 1 | input | 内核复位信号,低有效 |

| 3 | idu2csr_we | 1 | input | CSR读写总线,写使能 |

| 4 | idu2csr_addr | 12 | input | CSR读写总线,地址 |

| 5 | idu2csr_wdata | 32 | input | CSR读写总线,写数据 |

| 6 | csr2idu_rdata | 32 | output | CSR读写总线,读数据 |

| 7 | csr2cic_gie | 1 | output | 全局中断使能 |

| 8 | csr2cic_mie | 16 | output | 机器模式下每个中断源的使能 |

| 9 | csr2cic_mip | 16 | output | 机器模式下每个中断源的等待 |

| 10 | cic2csr_irq | 16 | input | 中断请求 |

| 11 | cic2csr_mcause | 5 | input | 中断原因 |

| 12 | csr2idu_mepc | 18 | output | 机器异常程序计数器 |

| 13 | csr2idu_mtvec | 18 | output | 机器模式下中断向量 |

| 14 | idu2csr_mepc_set | 1 | input | 机器模式下中断发生时的PC保存请求 |

| 15 | idu2csr_mepc_nxt | 18 | input | 机器模式下中断发生时的PC保存数据 |

4.寄存器说明

寄存器的地址设计和 RISC-V 的标准兼容,这是一个遵循规范和确保兼容性的重要举措。RISC-V 标准对寄存器地址的定义具有明确的规则和约定,遵循这些标准能够带来多方面的好处。首先,确保了与其他符合 RISC-V 架构的组件和系统的良好兼容性。这意味着在不同的 RISC-V 实现之间,可以更轻松地进行交互和集成。

| 地址 | 寄存器 | 特性 | 默认值 | 说明 |

|---|---|---|---|---|

| 0x300 | MSTATUS | RW | 0x00000000 | bit3: 全局中断使能 |

| 0x301 | MISA | RO | 0x40000010 | RV32E CPU |

| 0x304 | MIE | RW | 0x00000000 | 16个外部中断的使能位 |

| 0x305 | MTVEC | RW | 0x00000000 | 中断向量,低2bit为0 |

| 0x341 | MEPC | RW | 0x00000000 | 机器异常程序计数器,低2bit为0 |

| 0x342 | MCAUSE | RO | 0x00000000 | 中断原因,bit31为1表示存在中断,bit3-bit0表示中断编号 |

| 0x344 | MIP | RW1C | 0x00000000 | 中断请求的等待 |

| 0xF12 | MARCHID | RO | 0x4b2d3041 | 字符“K0-A"的ASCII码 |

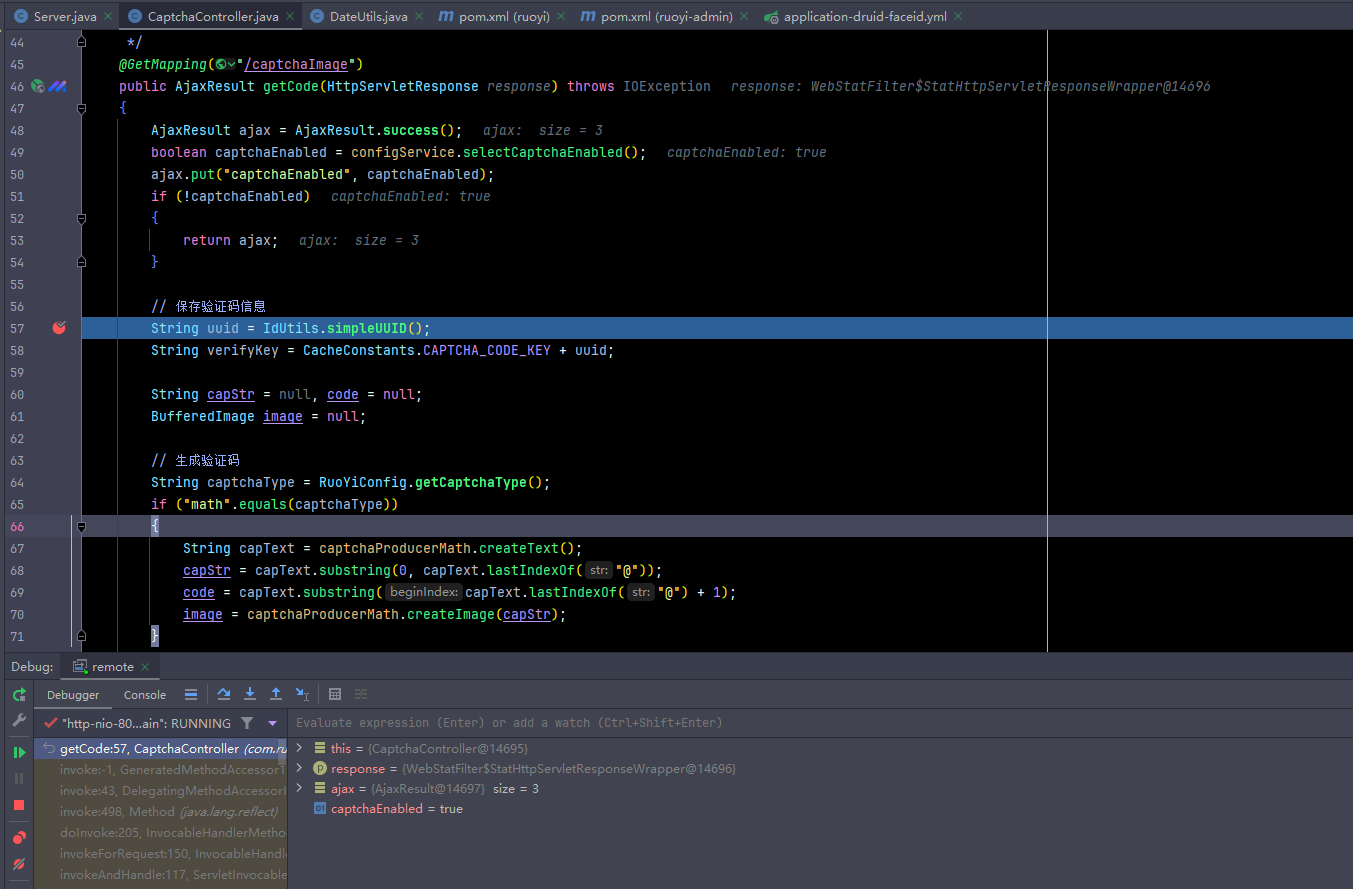

5.代码设计

// -------------------------------------------------------------------------------------------------

// Copyright 2024 Kearn Chen, kearn.chen@aliyun.com

//

// Licensed under the Apache License, Version 2.0 (the "License");

// you may not use this file except in compliance with the License.

// You may obtain a copy of the License at

//

// http://www.apache.org/licenses/LICENSE-2.0

//

// Unless required by applicable law or agreed to in writing, software

// distributed under the License is distributed on an "AS IS" BASIS,

// WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

// See the License for the specific language governing permissions and

// limitations under the License.

// -------------------------------------------------------------------------------------------------

// Description :

// 1. Control and Status Register

// -------------------------------------------------------------------------------------------------

module k0a_core_csr (

input wire core_clk ,

input wire core_rstn ,

input wire idu2csr_we ,

input wire [11:0] idu2csr_addr ,

input wire [31:0] idu2csr_wdata ,

output wire [31:0] csr2idu_rdata ,

output reg csr2cic_gie ,

output reg [15:0] csr2cic_mie ,

output reg [15:0] csr2cic_mip ,

input wire [15:0] cic2csr_irq ,

input wire [4:0] cic2csr_mcause ,

output reg [17:0] csr2idu_mepc ,

output reg [17:0] csr2idu_mtvec ,

input wire idu2csr_mepc_set ,

input wire [17:0] idu2csr_mepc_nxt

);

localparam CSR_MARCHID = 12'hf12;

localparam CSR_MSTATUS = 12'h300;

localparam CSR_MISA = 12'h301;

localparam CSR_MIE = 12'h304;

localparam CSR_MTVEC = 12'h305;

localparam CSR_MEPC = 12'h341;

localparam CSR_MCAUSE = 12'h342;

localparam CSR_MIP = 12'h344;

wire csr_marchid_sel = idu2csr_addr == CSR_MARCHID;

wire csr_mstatus_sel = idu2csr_addr == CSR_MSTATUS;

wire csr_misa_sel = idu2csr_addr == CSR_MISA;

wire csr_mie_sel = idu2csr_addr == CSR_MIE;

wire csr_mtvec_sel = idu2csr_addr == CSR_MTVEC;

wire csr_mepc_sel = idu2csr_addr == CSR_MEPC;

wire csr_mcause_sel = idu2csr_addr == CSR_MCAUSE;

wire csr_mip_sel = idu2csr_addr == CSR_MIP;

always @(posedge core_clk or negedge core_rstn)

begin

if(!core_rstn)

csr2cic_gie <= 1'b0;

else if(csr_mstatus_sel & idu2csr_we)

csr2cic_gie <= idu2csr_wdata[3];

end

always @(posedge core_clk or negedge core_rstn)

begin

if(!core_rstn) begin

csr2cic_mie <= 16'd0;

end else if(csr_mie_sel & idu2csr_we)

csr2cic_mie <= idu2csr_wdata[15:0];

end

always @(posedge core_clk)

begin

if(csr_mtvec_sel & idu2csr_we)

csr2idu_mtvec <= idu2csr_wdata[19:2];

end

always @(posedge core_clk)

begin

if(idu2csr_mepc_set)

csr2idu_mepc <= idu2csr_mepc_nxt;

else if(csr_mepc_sel & idu2csr_we)

csr2idu_mepc <= idu2csr_wdata[19:2];

end

always @(posedge core_clk or negedge core_rstn)

begin

if(!core_rstn)

csr2cic_mip <= 16'd0;

else if(csr_mip_sel & idu2csr_we)

csr2cic_mip <= idu2csr_wdata[15:0] | cic2csr_irq;

else if(csr2cic_gie)

csr2cic_mip <= csr2cic_mip | cic2csr_irq;

end

assign csr2idu_rdata = {32{csr_marchid_sel }} & 32'h4b2d3041 |

{32{csr_mstatus_sel }} & {28'h180, csr2cic_gie, 3'd0} |

{32{csr_misa_sel }} & 32'h40000010 |

{32{csr_mie_sel }} & {16'd0, csr2cic_mie} |

{32{csr_mtvec_sel }} & {12'd0, csr2idu_mtvec, 2'd0} |

{32{csr_mepc_sel }} & {12'd0, csr2idu_mepc, 2'd0} |

{32{csr_mcause_sel }} & {cic2csr_mcause[4], 27'd0, cic2csr_mcause[3:0]} |

{32{csr_mip_sel }} & {16'd0, csr2cic_mip} ;

endmodule

6.总结

在本文所介绍的 CSR 实现中,为追求极致简洁而未依照 RISC-V 标准在内部实现计数器的设计,这一决策具有一定的特点和影响。这种选择带来的好处是能够减少设计的复杂性和资源消耗。通过舍弃计数器的设计,可能降低了硬件实现的成本和面积,使得整个系统更加紧凑和高效。如果在本设计的应用场景中,对计数器的需求并不强烈或者可以通过外部的方式来满足计数要求,那么这种追求简洁的设计策略就是合理且有效的。