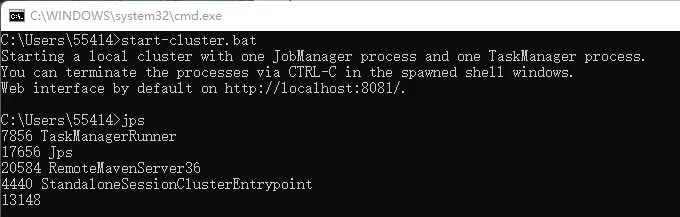

引言 vc-spyglass sdc检查时遇到的问题

正如vc spyglass sdc check提示Error: 当两个时钟设置成物理互斥或逻辑互斥时,需要另外加上这两个时钟是异步设置的约束。

个人经历:

由于本人经验尚浅,之前遇到的项目,个人理解是设置了物理互斥就代表了两个时钟是异步的,因此之前也没有另外加-async的异步设置。

提问:

鉴于vc sdc check提示的Error,我想请问各位大佬遇到这种物理/逻辑互斥的情况,还有另外加上set_clock_groups -async的约束吗?欢迎留言评论。

物理互斥与异步设置总结

在SDC(Synopsys Design Constraints)约束中,set_clock_groups -physically_exclusive 和 set_clock_groups -asynchronous 是用来定义时钟组之间的关系的。它们的用途和行为有所不同:

-

set_clock_groups -physically_exclusive:指定一组时钟是物理上互斥的,即这些时钟不能同时活动。这在设计中有物理约束的场景中使用,例如在一些功耗管理策略中,不同的电源域中的时钟可能是互斥的。 -

set_clock_groups -asynchronous:指定一组时钟是异步的,即这些时钟之间没有时序关系,时序分析工具不需要分析这些时钟之间的路径。这通常用于不同时钟域之间的约束,明确告诉时序分析工具不需要跨时钟域的时序分析。

优先级和覆盖关系

根据SDC约束的行为和优先级:

set_clock_groups -physically_exclusive和set_clock_groups -asynchronous是不同类型的约束,通常会同时存在而不会互相覆盖。-physically_exclusive是一种物理约束,表示时钟的互斥性;-asynchronous是一种时序分析约束,表示时钟之间的异步性。

这意味着,当你在SDC文件中先设置了 set_clock_groups -physically_exclusive,然后又设置了 set_clock_groups -asynchronous,两种约束都会存在,并且各自起作用。

实际影响

- 物理上互斥:当时钟被设置为物理上互斥时,设计工具会理解这些时钟不能同时活动,并可能在功耗管理策略或特定设计约束中使用这些信息。

- 时序分析:当时钟被设置为异步时,时序分析工具会忽略这些时钟之间的时序路径,不会在这些时钟之间进行跨时钟域的时序分析。

示例

假设有两个时钟 clk1 和 clk2:

# 设置 clk1 和 clk2 物理上互斥

set_clock_groups -physically_exclusive -group {clk1} -group {clk2}

# 设置 clk1 和 clk2 异步

set_clock_groups -asynchronous -group {clk1} -group {clk2}

在这种情况下,工具会理解:

clk1和clk2是物理上互斥的(即不能同时活动)。clk1和clk2之间没有时序关系(即工具不会分析跨这两个时钟域的时序路径)。

结论

两种约束 -physically_exclusive 和 -asynchronous 会同时存在,不会互相覆盖。各自的约束属性会被工具理解并应用于设计中,因此可以同时使用这两种约束来分别管理时钟的物理互斥性和异步性。