目录

一. 简介

二. Verilog简介和基本程序结构

三. 应用场景

四. Verilog的学习方法

五.调式方法

一. 简介

硬件描述语言(Hardware Description Language,HDL)是用于描述数字电路和系统的形式化语言。

常见的硬件描述语言包括 VHDL(VHSIC Hardware Description Language)和 Verilog。

硬件描述语言具有以下特点和优势:

- 抽象层次高:可以在不同的抽象层次上描述电路,从系统级到门级,方便对复杂数字系统进行建模和设计。

- 可读性强:采用类似编程语言的语法,使得设计人员能够清晰地表达电路的功能和结构。

- 可仿真性:能够进行功能仿真和时序仿真,在设计早期发现潜在的问题,降低设计风险。

- 可综合:可以将描述的电路转换为实际的硬件电路,例如通过综合工具生成门级网表。

- 便于团队协作:统一的语言规范有助于多个设计人员协同工作,提高开发效率。

使用硬件描述语言进行数字电路设计,可以提高设计的效率和质量,缩短开发周期,并且便于对设计进行维护和修改。

二. Verilog简介和基本程序结构

Verilog 是一种用于描述数字电路和系统的硬件描述语言。

Verilog 的主要特点包括:

- 简洁的语法:易于学习和使用。

- 多层次的描述能力:可以在行为级、寄存器传输级和门级等不同层次描述电路。

- 强大的建模能力:能够对组合逻辑、时序逻辑、存储单元等进行精确建模。

Verilog 的基本程序结构通常包括以下几个部分:

- 模块声明(Module Declaration):使用

module关键字开始,指定模块的名称和端口列表。

module module_name (port1, port2,...);

- 端口声明(Port Declaration):定义模块的输入、输出和双向端口。

input port1;

output port2;

inout port3;

- 数据类型声明(Data Type Declaration):如

wire(用于连接逻辑)和reg(用于存储值)等。- 内部信号声明(Internal Signal Declaration):用于模块内部的连接和临时存储。

- 逻辑描述(Logic Description):使用各种语句和结构描述电路的功能,如

always块用于描述时序逻辑,assign语句用于描述组合逻辑等。- 模块结束(Module End):使用

endmodule结束模块定义。

以下是一个简单的 Verilog 示例,实现一个 2 输入与门:

module and_gate (input a, input b, output out);

assign out = a & b;

endmodule

三. 应用场景

Verilog 具有广泛的应用场景,主要包括以下几个方面:

- 集成电路设计:用于设计芯片内部的数字逻辑电路,从简单的门级电路到复杂的系统级芯片(SoC)。

- 数字系统设计:如微处理器、控制器、数字信号处理器(DSP)等的设计。

- 现场可编程门阵列(FPGA)开发:通过编写 Verilog 代码来配置 FPGA 实现特定的功能。

- 专用集成电路(ASIC)设计:在 ASIC 设计流程中,描述电路功能和进行逻辑综合。

- 验证和测试平台开发:编写测试激励和验证模块,对设计的电路进行功能验证和性能测试。

- 嵌入式系统设计:为嵌入式系统中的数字部分进行建模和设计。

- 通信系统设计:如调制解调器、编解码器等数字通信模块的设计。

- 计算机硬件设计:包括内存控制器、总线接口等的设计。

四. Verilog的学习方法

以下是一些学习 Verilog 语言的建议和步骤:

-

基础知识学习

- 了解数字电路的基本概念,如逻辑门、组合逻辑、时序逻辑、计数器、寄存器等。这将为理解 Verilog 的建模提供基础。

- 学习 Verilog 的语法规则,包括数据类型、模块结构、端口定义、操作符、语句等。

-

参考优秀教材和在线资源

- 选择权威的 Verilog 教材,如《Verilog HDL 数字设计与综合》等。

- 利用在线教程、博客和视频课程,许多网站提供了详细的 Verilog 教学内容。

-

实践练习

- 从简单的示例开始,如实现基本的逻辑门、加法器等。

- 逐渐增加难度,设计更复杂的电路,如有限状态机、计数器、数据通路等。

-

使用开发工具

- 安装 Verilog 编译和仿真工具,如 ModelSim、QuestaSim 等。

- 通过实际编写代码、编译和仿真来验证设计的正确性。

-

参与项目和案例

- 参与实际的项目或开源项目,将 Verilog 应用于具体的问题解决中。

- 分析他人的优秀代码,学习其设计思路和技巧。

-

深入学习高级主题

- 研究时序约束、综合优化、可测试性设计等高级主题,以提高设计的质量和性能。

-

交流与讨论

- 加入相关的技术论坛或社区,与其他学习者和专业人士交流经验,解决遇到的问题。

五.调式方法

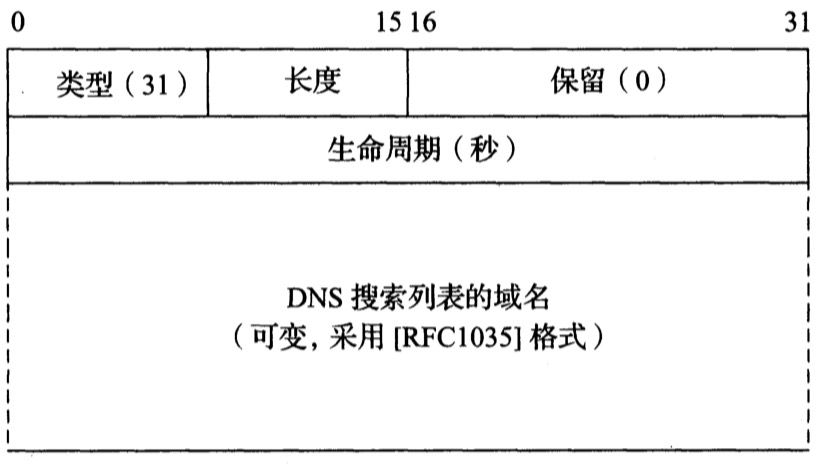

- 仿真工具:使用专业的仿真工具,如 ModelSim、Vivado Simulator 等。通过设置断点、单步执行、查看信号值和波形等功能来跟踪代码的执行过程和信号变化。

- 打印输出:在关键位置使用

$display或$monitor系统任务来输出相关信号的值或提示信息,以便了解代码执行中的中间状态。 - 层次化调试:将大型设计分解为较小的模块,先单独调试各个模块,确保它们的功能正确,然后再集成调试整个系统。

- 断言语句:使用

assert语句来检查关键的条件是否满足预期,如果不满足则触发错误提示。 - 代码审查:仔细检查代码的逻辑、语法和端口连接,确保没有明显的错误。

- 逻辑分析仪:对于在硬件上实现的设计,可以使用逻辑分析仪来捕获实际的信号并进行分析。

- 分阶段调试:先关注主要的功能逻辑,确保其正确,然后再处理边界情况和异常情况。

- 比较参考模型:如果可能,创建一个已知正确的参考模型(可以用其他语言或简单的 Verilog 实现),将结果与正在调试的设计进行比较。

- 记录调试信息:在代码中添加注释,记录调试过程中的发现和修改,以便后续回顾和优化。

![[C++]——同步异步日志系统(6)](https://i-blog.csdnimg.cn/direct/2e7a2281e1714ff8a0e2c179dc9cc4b2.png)