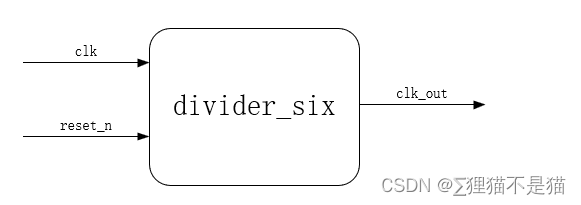

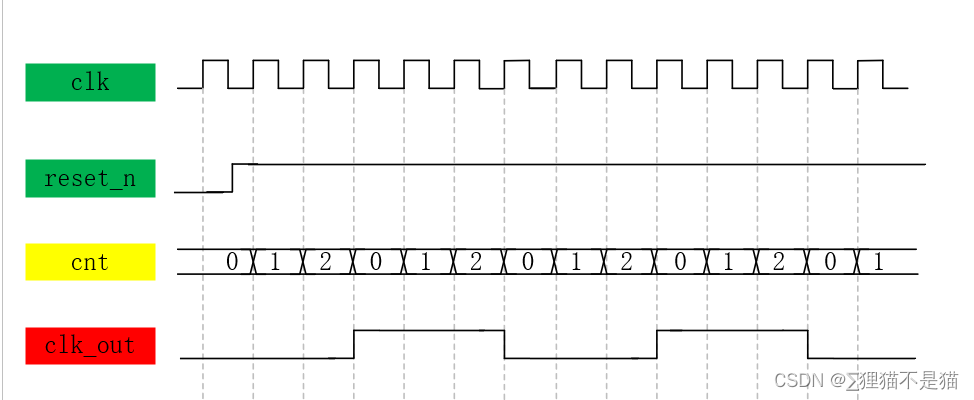

设计一个六分频时钟信号

(1)visio视图:

(2)Verilog代码:

module divider_six(clk,reset_n,clk_out);

input clk;

input reset_n;

output reg clk_out;

reg [1:0]cnt;

//计数器模块设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

cnt <= 2'd0;

else if (cnt == 2'd2)

cnt <= 2'd0;

else

cnt <= cnt + 2'd1;

//clk_out信号设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

clk_out <= 1'd0;

else if (cnt == 2'd2)

clk_out <= ~clk_out;

else

clk_out <= clk_out;

endmodule

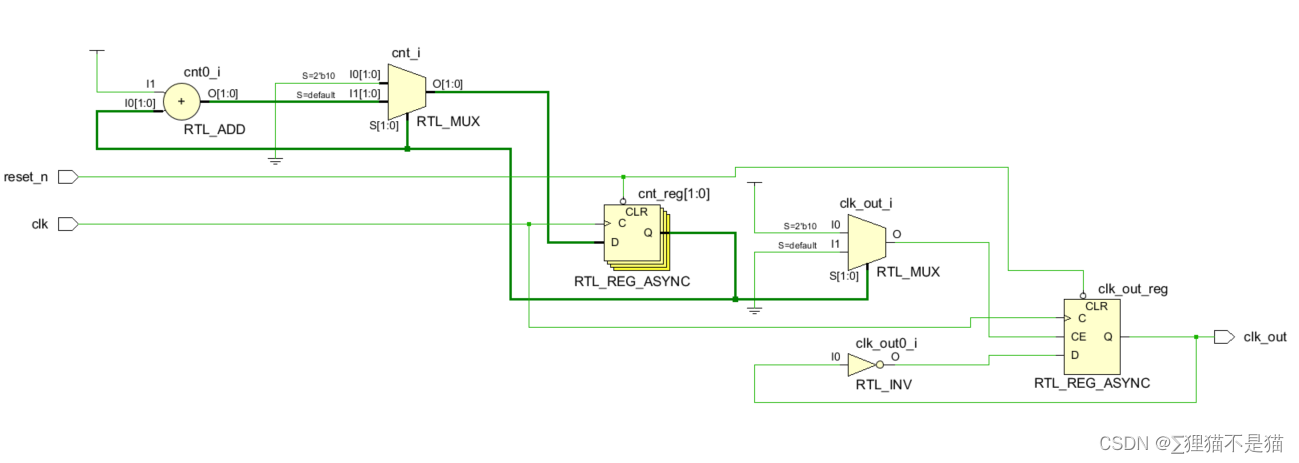

(3)RTL视图:

(4)仿真文件代码:

`timescale 1ns / 1ps

module divider_six_tb;

reg clk;

reg reset_n;

wire clk_out;

divider_six divider_six_inst(

.clk(clk),

.reset_n(reset_n),

.clk_out(clk_out)

);

initial clk = 1'd1;

always #10 clk = ~clk;

initial begin

reset_n = 1'd0;

#20;

reset_n = 1'd1;

#2000

$stop;

end

endmodule

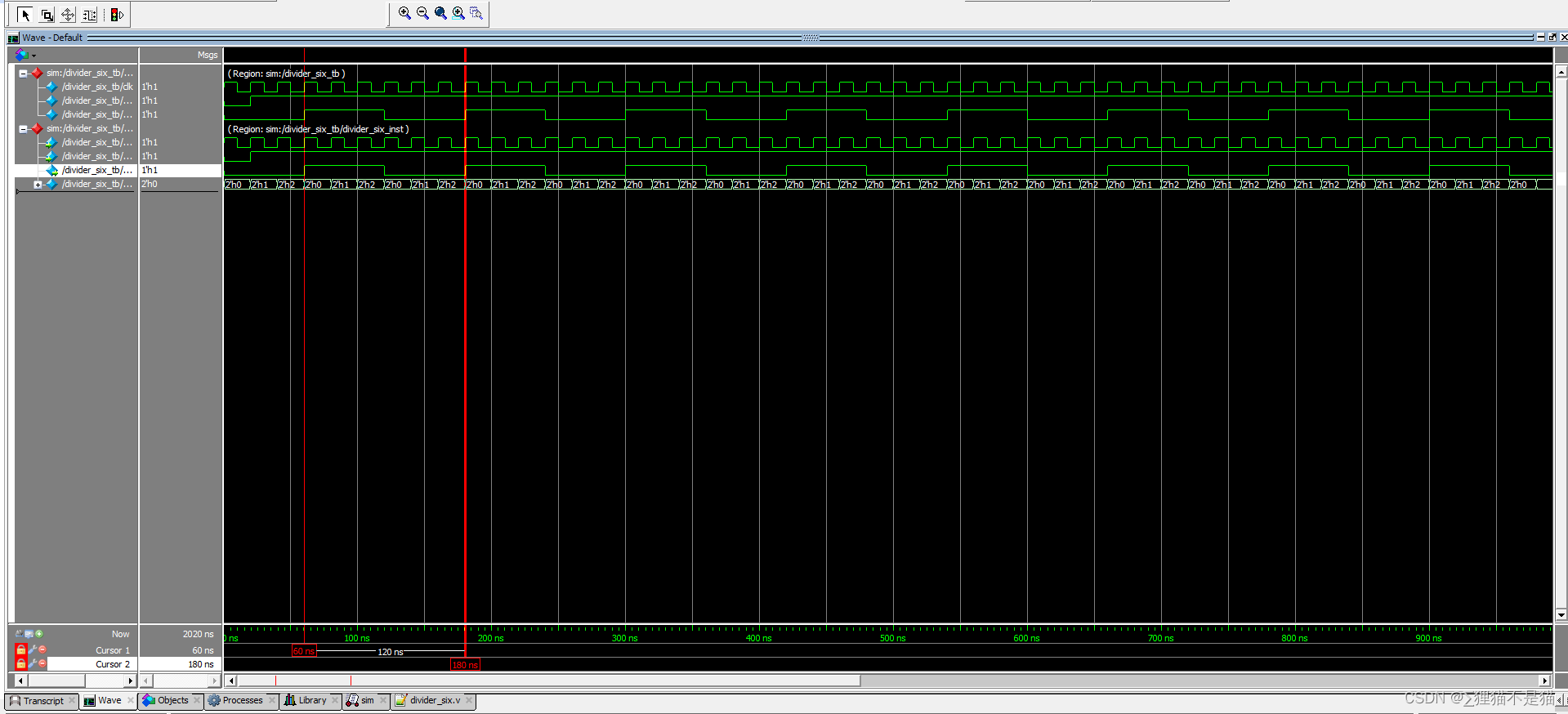

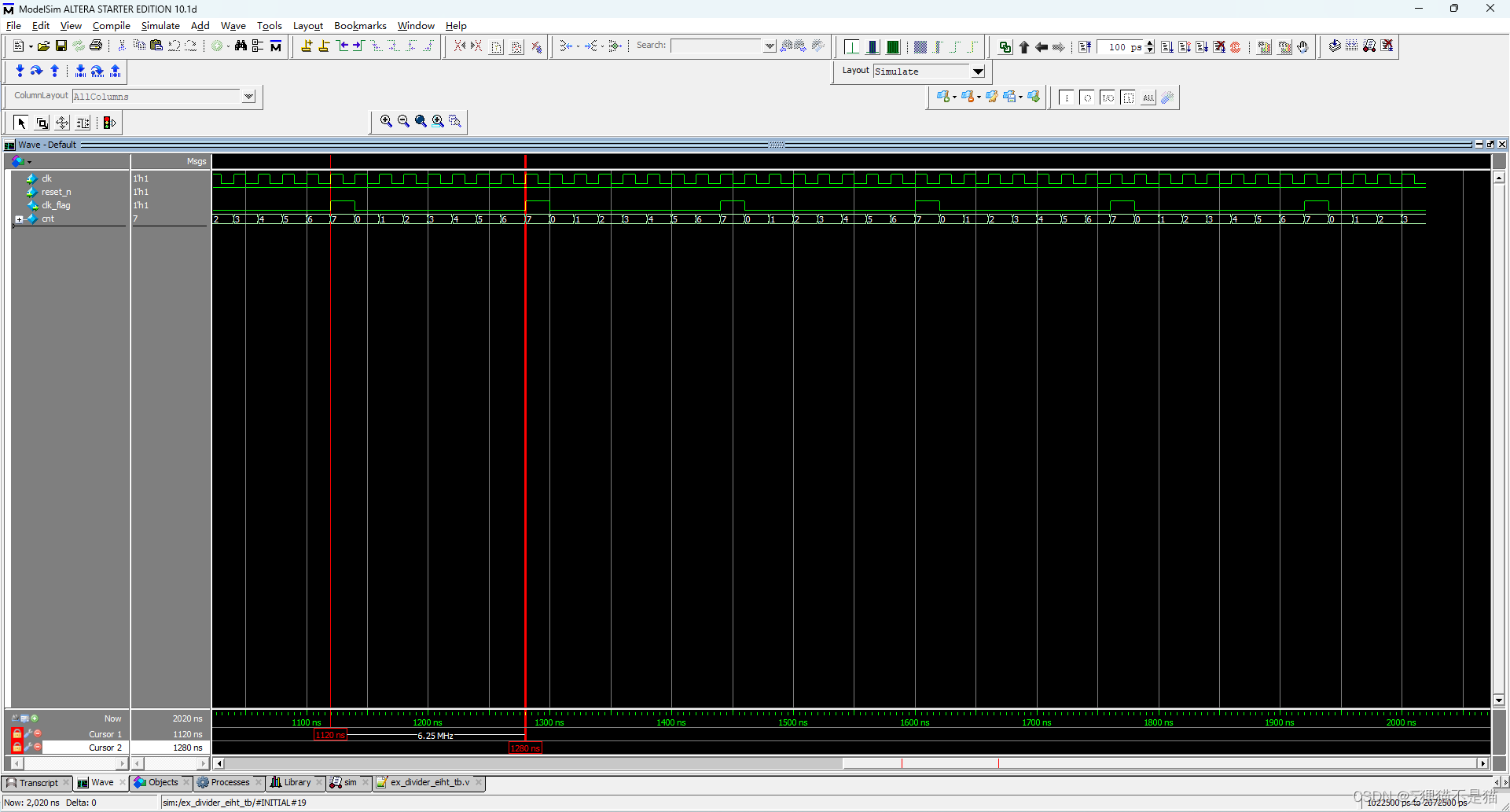

(5)仿真波形:

(6)引脚绑定:

set_property IOSTANDARD LVCMOS33 [get_ports clk_out]

set_property IOSTANDARD LVCMOS33 [get_ports reset_n]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN N15 [get_ports reset_n]

set_property PACKAGE_PIN W19 [get_ports clk]

set_property PACKAGE_PIN M13 [get_ports clk_out]

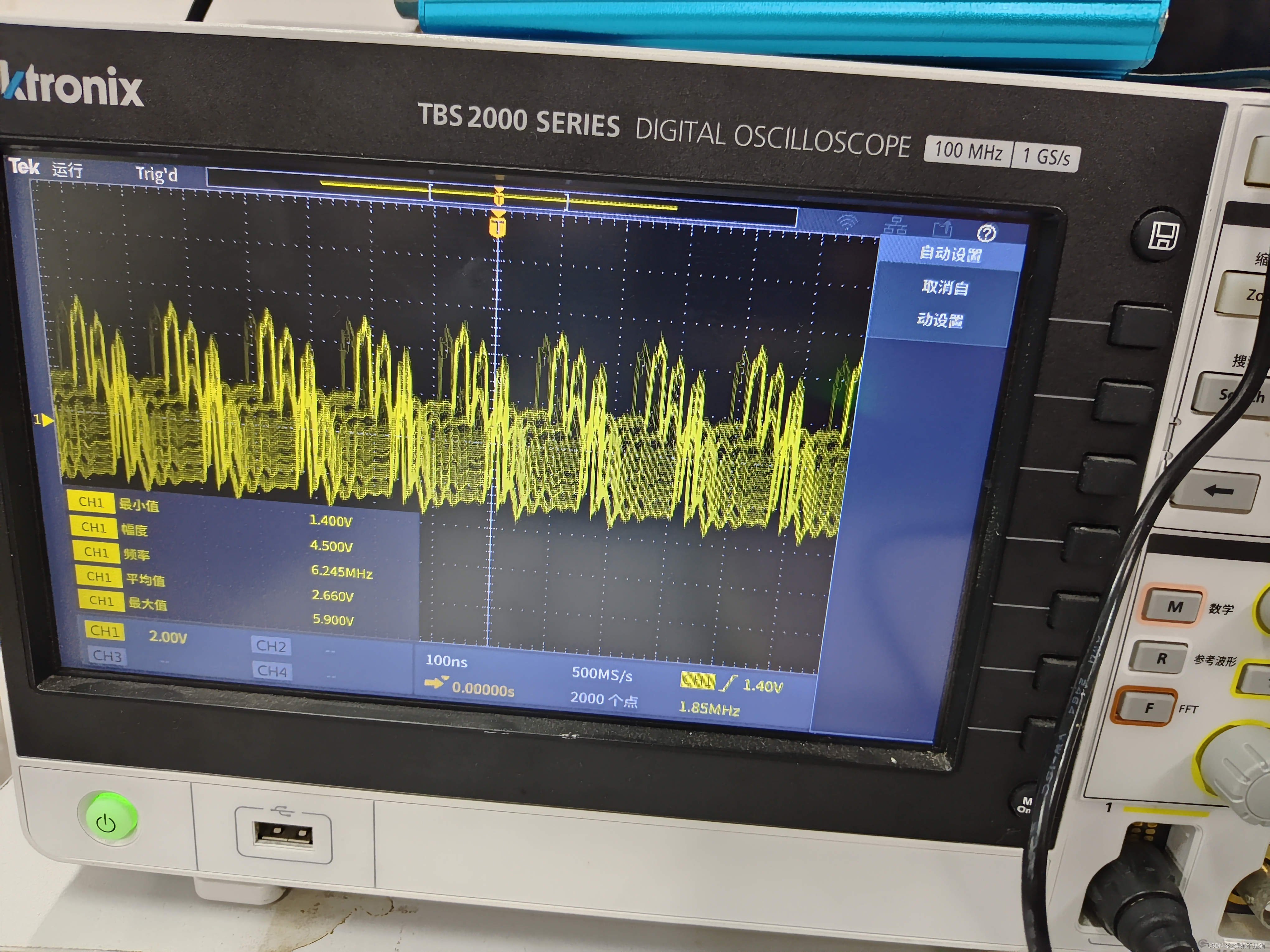

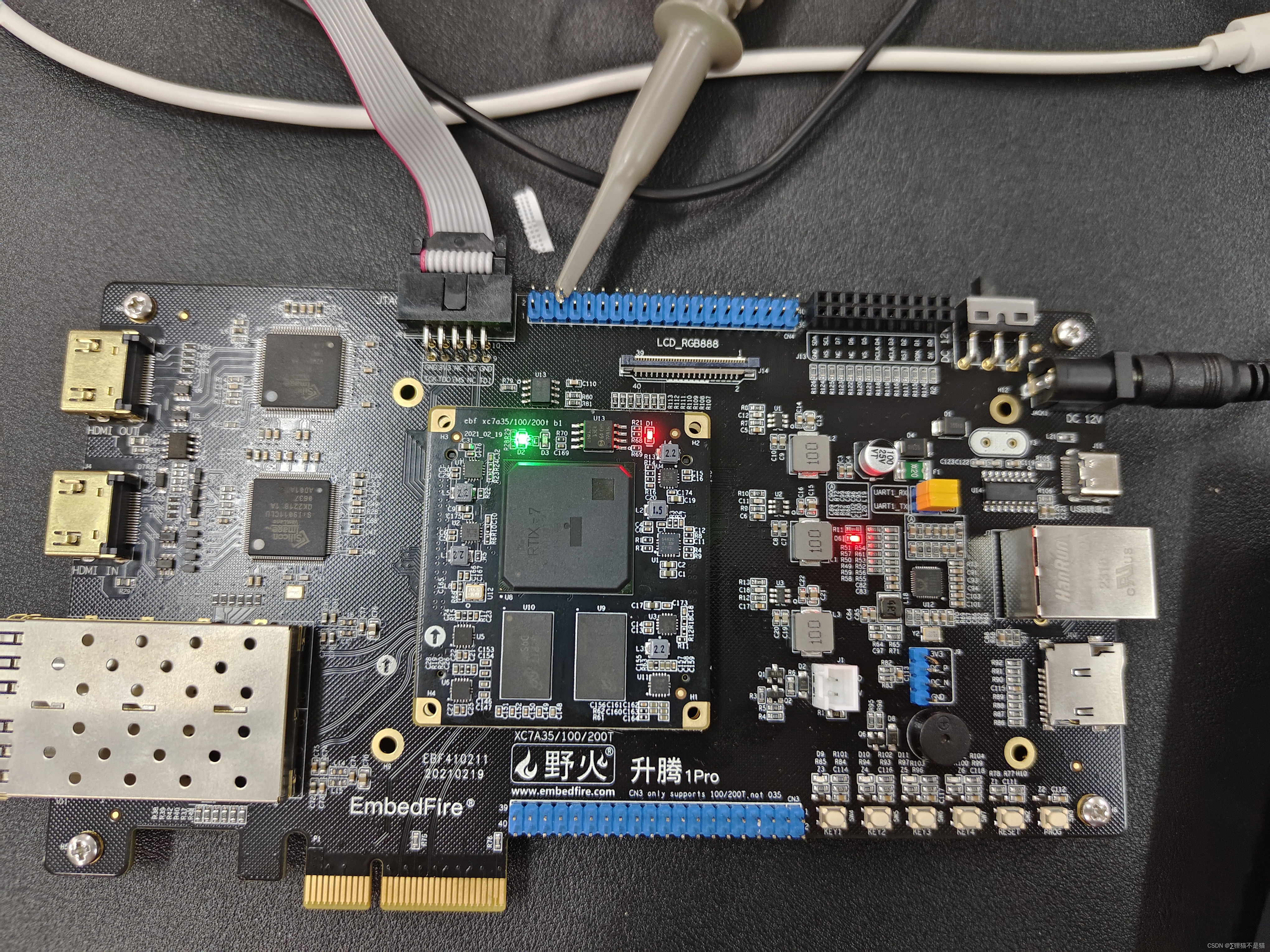

(7)实验现象:

(8)使用降频的方法实现八分频:

module ex_divider_eiht(clk,reset_n,clk_flag);

input clk;

input reset_n;

output reg clk_flag;

reg [2:0]cnt;

//计数器设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

cnt <= 3'd0;

else

cnt <= cnt + 3'd1;

//clk_flag信号设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

clk_flag <= 1'd0;

else if(cnt == 3'd6)

clk_flag <= 1'd1;

else

clk_flag <= 1'd0;

endmodule`timescale 1ns / 1ps

module ex_divider_eiht_tb;

reg clk;

reg reset_n;

wire clk_flag;

ex_divider_eiht ex_divider_eiht0(

.clk(clk),

.reset_n(reset_n),

.clk_flag(clk_flag)

);

initial clk = 1'd1;

always #10 clk = ~clk;

initial begin

reset_n <= 1'd0;

#20

reset_n <= 1'd1;

#2000

$stop;

end

endmodule

set_property IOSTANDARD LVCMOS33 [get_ports reset_n]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk_flag]

set_property PACKAGE_PIN N15 [get_ports reset_n]

set_property PACKAGE_PIN W19 [get_ports clk]

set_property PACKAGE_PIN M13 [get_ports clk_flag]