文章目录

- 硬件设计

- 引脚

- 功能框图

- 说明

- PHYADDR

- Page

- LED 模式

- 自动协商/速度/全半双工模式

- Soft Reset

- 上电顺序

- 原理图设计参考

- 软件控制(FPGA)

- 硬件调试

硬件设计

引脚

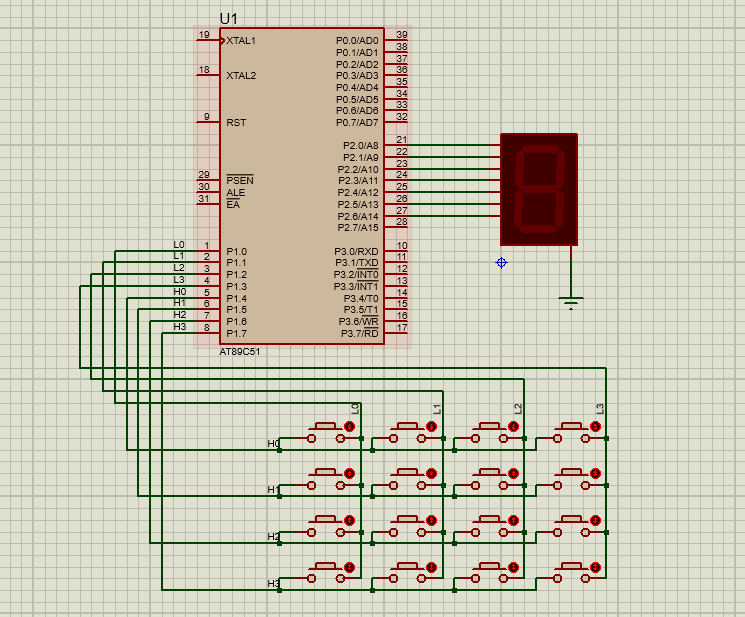

笔者前代数字采集板采用的 PHY 芯片是博通 Boardcom 的 B50610,其仅支持 0 ∼ 7 0 ∘ C 0\sim70^\circ C 0∼70∘C 的工作温度,不符合预期的工作环境温度范围,且没有可直接替换的低温版本。因此在新一版采集板设计中须更换 PHY 芯片,拟采用瑞昱 Realtek 的 RTL8211FS,其工业版本 FSI 版本的可支持 − 4 0 ∘ C -40^\circ C −40∘C 的低温工作环境。首先做一个小的测试板,验证其电路及功能是否可行,本文即对此进行一个工作记录。

RTL8211FSI 的接口如下图

-

RGMII 接口

- TX:TXC (I),TXD3:0 (I),TXCTL (I);

- RX:RXC (O),RXD3:0 (O),RXCTL (O);

- RXDLY,RX Delay,上拉(接 4.9 k Ω 4.9k\Omega 4.9kΩ 到 DVDD_RG)时,在 RXC 到 RXD 增加 2ns 的延迟;下拉时接 4.9 k Ω 4.9k\Omega 4.9kΩ 到 GND;

- TXDLY 没有引脚进行配置,但可以通过 Page 0xd08, Reg17, Bit[8] 进行设置。

-

SMI 接口

- MDC (I)

- MDIO (IO),引脚接 1.5 k Ω 1.5k\Omega 1.5kΩ 上拉

-

SerDes 接口 (不使用,设计中直接悬空即可)

- HSIP,HSIN,HSOP,HSON,HSOP_CLK,HSON_CLK

-

MDI 接口 (不多介绍,连接 RJ45 水晶头)

- MDIP/MDIN[3:0] (IO)

-

CLK

- XTAL_IN,I,25M 时钟输入,若有外部时钟驱动 XTAL_OUT/EXT_CLK 脚,则本引脚应接地;

- XTAL_OUT/EXT_CLK,O,25M 时钟输出;若使用外部时钟,本引脚接晶振输出端;

- CLKOUT,O,芯片内部 PLL 产生的时钟,若此时钟未被使用,应浮空;在 1000BASE 和 100BASE 时输出 125M/25M,用以支持同步以太网(作为主机,由内部 PLL 输出,作为从机,从 MDI 恢复出时钟),可通过 PHYCR2 (Page 0xa43, Addr 0x19)寄存器进行配置;

- PTP_CLK,对于 RTL8211FS(I)-VS 版本,33 脚为 PTP_CLK/PTP_GPIO0,PTP_CLK 为外部参考时钟,PTP 为精确时间协议 Precision Time Protocol,不使用应浮空;RTL8211FS(I) 版本下 33 脚则为 NC,浮空。

-

Hard Reset

PHYRSTB,即 Reset_n 引脚,硬复位,复位至少要保持 10ms 低电平。

-

PHYADDR

PHYAD[2:0],上电/硬复位后检测其引脚电平,决定 PHYADDR 的地址。

-

PWR

- AVDD33,模拟 3.3V 供电;

- AVDD10,模拟 1.0V 供电;

- DVDD10,数字核心 1.0V 供电;

- DVDD33,数字(非 RGMII IO)的 3.3V 供电;

- DVDD_RG,RGMII IO 电平,注意和 CFG_LDO[1:0] 的设置相匹配;注意,当 CFG_LDO[1:0]=00 时,IO Pad 由连接到 DVDD_RG 的 3.3V 供电,其他情况下则由内部 LDO 供电;

- VDD_REG,内部调节器的 3.3V 供电;

- REG_OUT,内部调节器的 1.0V 输出,由于实际是个 DCDC 开关电源,因此要串接 2.2 μ H 2.2\mu H 2.2μH 电感;应仅供应 AVDD10 和 DVDD10;

- RSET,接 2.49 k Ω ( 1 % ) 2.49k\Omega\ (1\%) 2.49kΩ (1%) 到 GND。

-

CFG 端口

- CFG_LDO[1:0],设置 RGMII IO 的电平,00: 3.3V,01: 2.5V,10: 1.8V,11: 1.5V;

- CFG_MODE[2:0],设置操作模式(网线类型 <-> 协议类型),000 对应 UTP <-> RGMII。

-

INTB/PMEB/GPIO1

该引脚的功能可以配置为中断 INTB 或电源管理 PMEB 功能,RTL8211FS(I)-VS 版本下,则还可作为 PTP_GPIO1;作为 PMEB 功能时,应接 4.7 k Ω 4.7k\Omega 4.7kΩ 到 3.3V;不使用时应浮空。

-

LED

LED[2:0] 默认分别表示 1000BASE、100BASE、10BASE,通过寄存器配置的介绍见后文

不过注意下 LED2、LED1 引脚的极性,LED2 应当采用共阴接法,LED1 则采用共阳接法。

功能框图

说明

PHYADDR

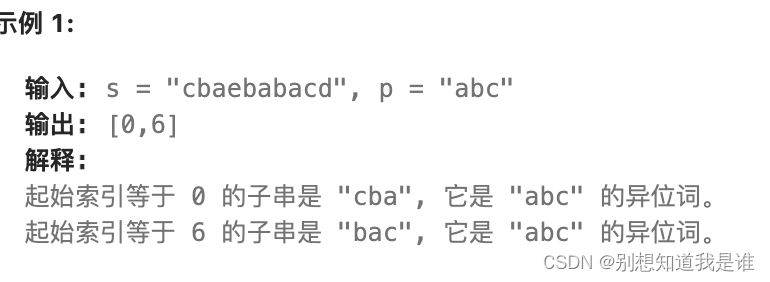

PHYADDR[4:3]='b00,PHYADDR[2:0]=PHYAD[2:0],由上电时 PHYAD[2:0] 引脚的上下拉状态决定,拥有 0x00 到 0x07 共 8 个可用地址。

注意,RTL8211FS 默认将地址 0x00 视为广播地址,所有 RTL8211FS 都会响应,可通过配置 PHYCR1 (Page 0xa43, Reg24 (0x18), Bit13 = 0) 来禁用广播功能。 如 PHYAD[2:0]='b000,RTL8211FS 默认会自动记住第一个非零地址,可以通过配置 PHYCR1, Bit6 = 1 来启用该功能。

因此,在设计中最好避开 0x00 这个地址,免去不必要的麻烦。

Page

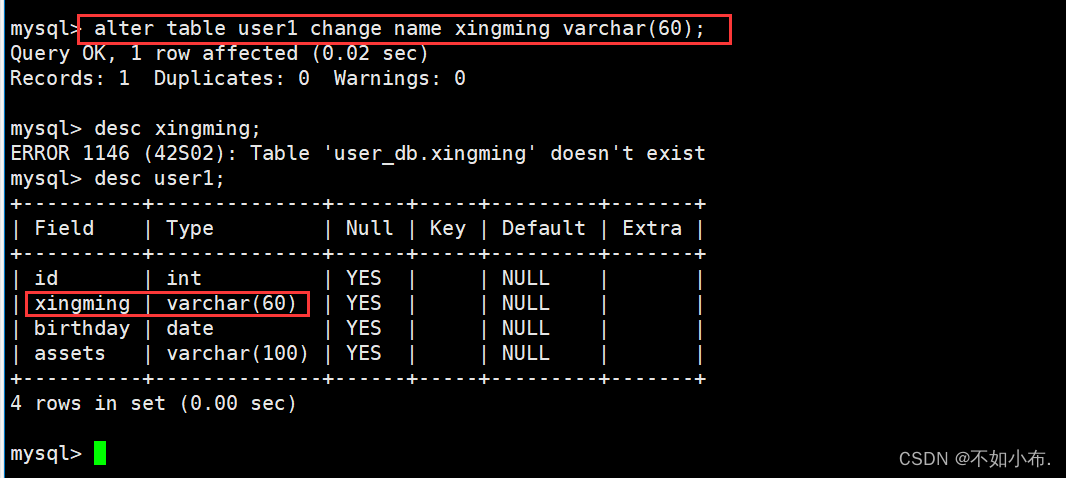

RTL8211FS 寄存器较多,因此除 RegAddr 外,还有不同的 Page。一个确切的寄存器声明如下:PAGE 0x0XXX, REG 0xXX, BIT[M:N]。

Page 可通过对 PAGSR(Page 0xa43, Reg 31 (0x1F), bit[11:0]) 寄存器进行配置。配置 Reg 31 值为 0x0000 或 0x0a42 将切换回 IEEE 标准寄存器。(略有疑问,PAGSR 寄存器应该是在 Page Any, Reg 31 都可以访问,而不仅在 Page 0xa43;后经过上板验证发现确实如此)

LED 模式

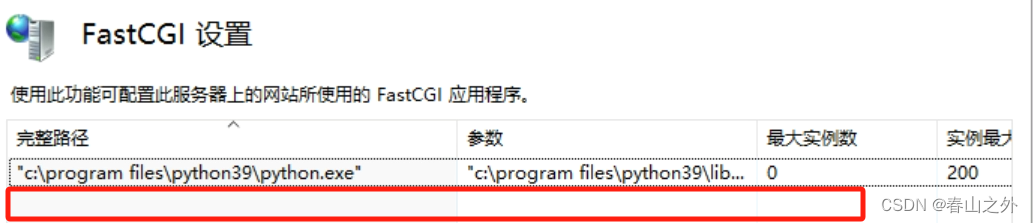

控制 LED 的官方参考设计如下(左,共阳接法;右,共阴接法)

RTL8211FS 的 LED 控制没有太花哨的功能,基本就是每个 LED 管脚对应一个速度。LCR (Page 0xD04, Reg 0x10) 寄存器用于配置 LED 的工作模式,以 LED2 管脚的默认值为例,LED2_ACT、LED2_LINK_1000 为 1,因此在连接 1000BASE 时,LED2 会亮起,当处于 1000BASE 活动状态时,则 LED2 闪烁。(这个默认配置就挺好用的,不需要再另行配置了,将 LED2/LED1 管脚接到 RJ45 的两个灯就可以了;注意极性)

自动协商/速度/全半双工模式

BMCR (Page 0x0, Reg 0), Bit 12 为自动协商使能,默认为 1 (on)。

当关闭自动协商时,BMCR Bit 6、Bit 13 决定本 PHY 芯片工作在何种速度,{Bit6, Bit13} = 10: 1000BASE,01: 100BASE,00: 10BASE。BMCR Bit 8 决定全双工/半双工模式,仅在关闭自动协商时起作用。

PHYSR (Page 0xa43, Reg 0x1A) 寄存器可以查看连接状态,Bit 2 指示是否连接,Bit5:4 指示速度,Bit 3 指示全半双工模式。

Soft Reset

Page 0x0, Reg 0, Bit 15 设为 1 将触发软复位,复位后自动清零。

上电顺序

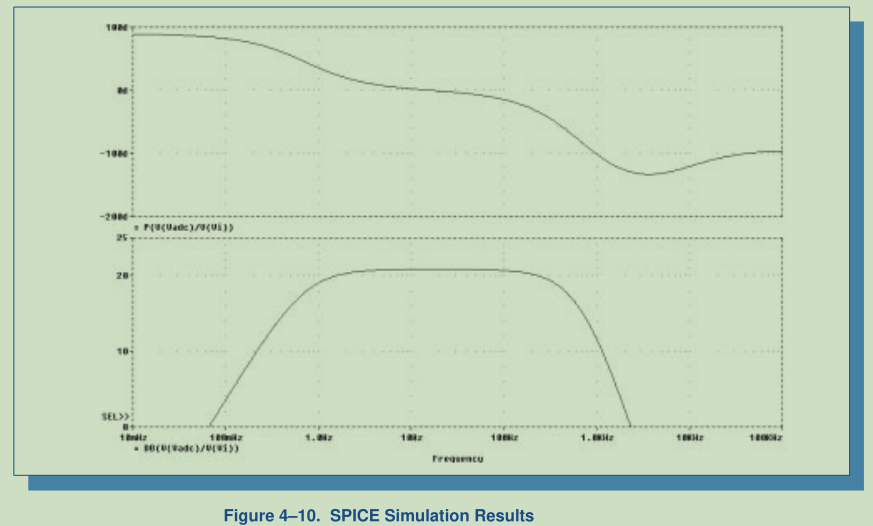

RTL8211FS 上电顺序如图

3.3V 供电的上升时间应大于 0.5ms,否则可能永久损坏内部电压调节器。

原理图设计参考

软件控制(FPGA)

(暂略)

硬件调试

打板回来后进行了测试,然而发现只能自动协商到 100BASE,进一步测试发现,十兆和百兆均可以正常建立连接,而千兆会协商失败,从而自动降速到了百兆。进一步通过 MDIO 关闭自协商,并强制规定到千兆,电脑就无法识别到这个设备了,读取 PHYSR (Page 0xa43,Reg 0x1A)寄存器,也发现 bit2=0 (Link not OK)。测量 3.3V 供电、 1.0V 核压以及 25M 晶振输出,均正常,其中 1.0V 输出有 70mV 纹波。

(咳,本菜鸟画的第一块 PCB,各种修正方案都尝试了一遍,但还是无法解决千兆连接的问题,是否有大佬可以指点一二,万分感激)