用Verilog实现4位计数器。(时序逻辑)

实验目的:

通过用Verilog实现4位计数器,进一步熟悉Verilog的语法和时序逻辑电路。

实验描述:

输入:

Clock:如果计数器enable信号为1,那么在时钟上升沿,count加1

Enable:如果enable为1,那么在时钟上升沿,count加1;如果enable为0,count保持不变

Reset:重置信号,如果reset为0,count重置为0

输出:

Count[3:0]:4位计数信号,范围:4‘b0000 – 4’b1111

实验分析:

从0-3计数,当脉冲到来时置零,进行四位计数

代码如下:

module count4(out,reset,clk);

output[3:0] out;

input reset,clk;

reg[3:0] out;

always @(posedge clk)

begin

if (reset)

out<=0; //同步复位

else

out<=out+1'b1; //计数

end

endmoduletestbench代码进行仿真测试:

`timescale 1ns/1ns

module test;

/*Make a reset that pulses once.*/

reg reset = 0;

initial

begin

#2 reset = 1; //reset

#3 reset = 0; //art count

#24 reset = 1; //reset

#2 reset = 0; //art count

#48 reset = 1; //reset

#3 reset = 0; //art count

#60 reset = 1; //reset

#3 reset = 0; //art count

#100 $stop;

end

/*Make a regular pulsing closk*/

parameter clk_period = 4;

reg clk;

initial

clk = 0;

always #(clk_period/2)

clk = ~clk;

wire[1:0] out;

count4 ctr(out,reset,clk);

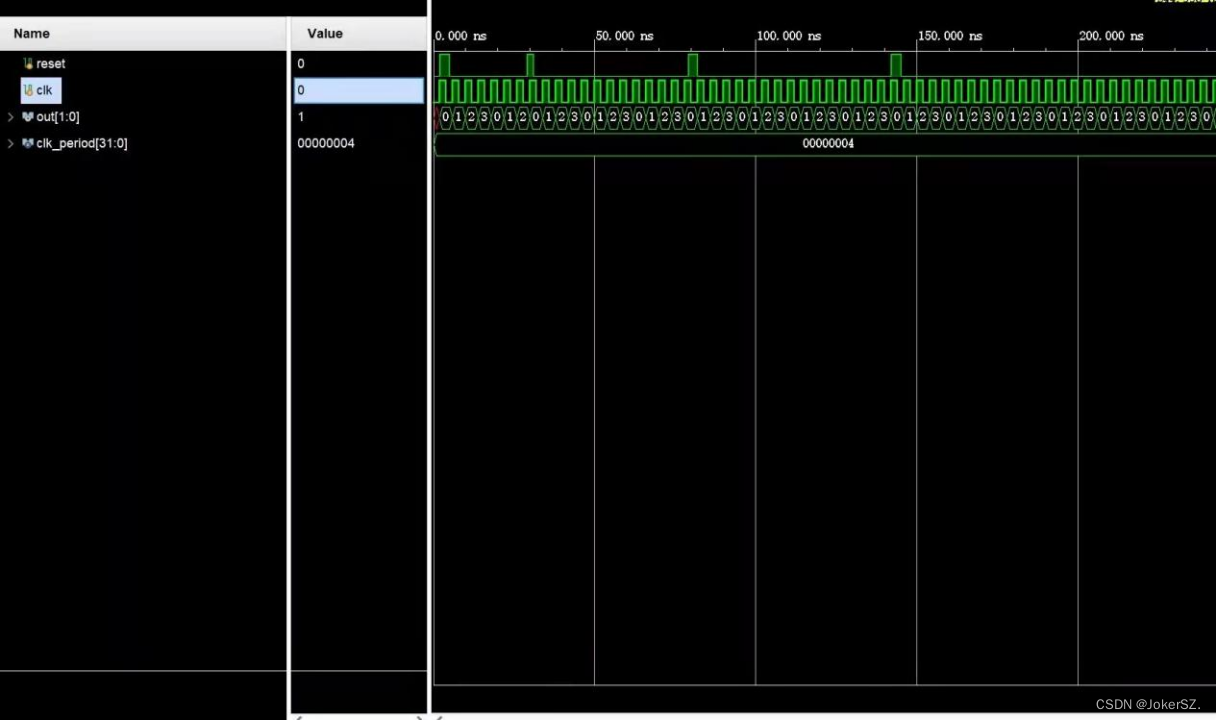

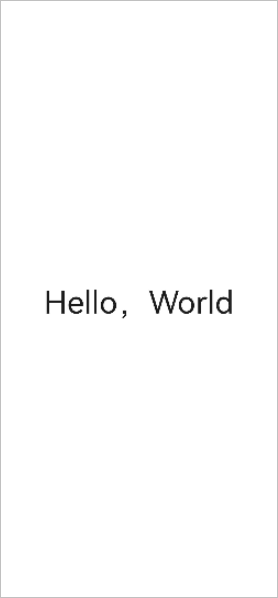

endmodule运行结果: