目录

- 1. Verilog采用的四值逻辑系统

- 2.主要数据类型

- 2.1 net(线网)

- 2.2 寄存器类 (register)

- 2.3 Verilog中net和register声明语法

- 2.3.1 net声明

- 2.3.2 寄存器声明

- 2.4 选择正确的数据类型

- 2.5 选择数据类型时常犯的错误

- 2.5.1 信号类型确定方法总结

- 2.5.2 常出的错误及相应的错误信息(error message)

- 2.5.3 选择数据类型时常犯的错误举例

微信公众号获取更多FPGA相关源码:

1. Verilog采用的四值逻辑系统

2.主要数据类型

Verilog主要有三类(class)数据类型:

- net (线网) : 表示器件之间的物理连接

- register (寄存器) :表示抽象存储元件

- parameters(参数) : 运行时的常数(run-time constants)

2.1 net(线网)

- net需要被持续的驱动,驱动它的可以是门和模块。

- 当net驱动器的值发生变化时, Verilog自动的将新值传送到net上。在例子中,线网out由or门驱动。

- 当or门的输入信号置位时将传输到线网net上。

有多种net类型用于设计(design-specific)建模和工艺(technology-specific)建模

**特别注意:**没有声明的net的缺省类型为 1 位(标量)wire类型。

- wire类型常用于组合电路描述。

- wire类型是最常用的类型,只有连接功能。

- wire和tri类型有相同的功能。用户可根据需要将线网定义为wire或tri以提高可读性。tri型的信号综合后具有三态的功能。

- wand、wor有线逻辑功能。

- trireg类型很象wire类型,但trireg类型在没有驱动时保持以前的值。这个值的强度随时间减弱。

- 修改net缺省类型的编译指导:

`default_nettype <nettype>

其中nettype不能是supply1和supply0。

2.2 寄存器类 (register)

- 寄存器类型在赋新值以前保持原值

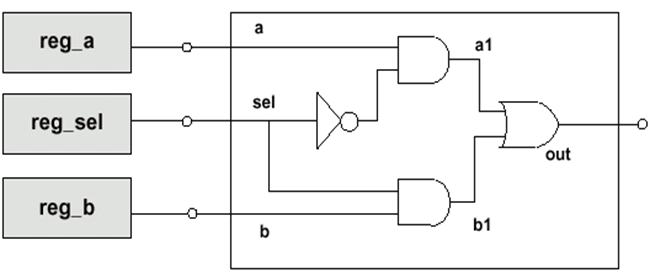

- 寄存器类型大量应用于行为模型描述及激励描述。在下面的例子中,reg_a、reg_b、reg_sel用于施加激励给2:1多路器。

- 用行为描述结构给寄存器类型赋值。给reg类型赋值是在过程块中。

下表给出了寄存器类有四种数据类型:

| 寄存器类型 | 功能 |

|---|---|

| reg | 可定义的无符号整数变量,可以是标量(1位)或矢量,是最常用的寄存器类型 |

| integer | 32位有符号整数变量,算术操作产生二进制补码形式的结果。通常用作不会由硬件实现的的数据处理。 |

| real | 双精度的带符号浮点变量,用法与integer相同。 |

| time | 64位无符号整数变量,用于仿真时间的保存与处理 |

| realtime | 与real内容一致,但可以用作实数仿真时间的保存与处理 |

2.3 Verilog中net和register声明语法

2.3.1 net声明

<net_type> [range] [delay] <net_name>[, net_name];

| 变量 | 含义 |

|---|---|

| net_type | net类型 |

| range | 矢量范围,以[MSB:LSB]格式 |

| delay | 定义与net相关的延时 |

| net_name | net名称,一次可定义多个net, 用逗号分开。 |

2.3.2 寄存器声明

<reg_type> [range] <reg_name>[, reg_name];

| 变量 | 含义 |

|---|---|

| reg_type | 寄存器类型 |

| range | 矢量范围,以[MSB:LSB]格式。只对reg类型有效 |

| reg_name | 寄存器名称,一次可定义多个寄存器,用逗号分开 |

举例:

reg a; //一个标量寄存器

wand w; // 一个标量wand类型net

reg [3: 0] v; // 从MSB到LSB的4位寄存器向量

reg [7: 0] m, n; // 两个8位寄存器

tri [15: 0] busa; // 16位三态总线

wire [0: 31] w1, w2; // 两个32位wire,MSB为bit0

2.4 选择正确的数据类型

2.5 选择数据类型时常犯的错误

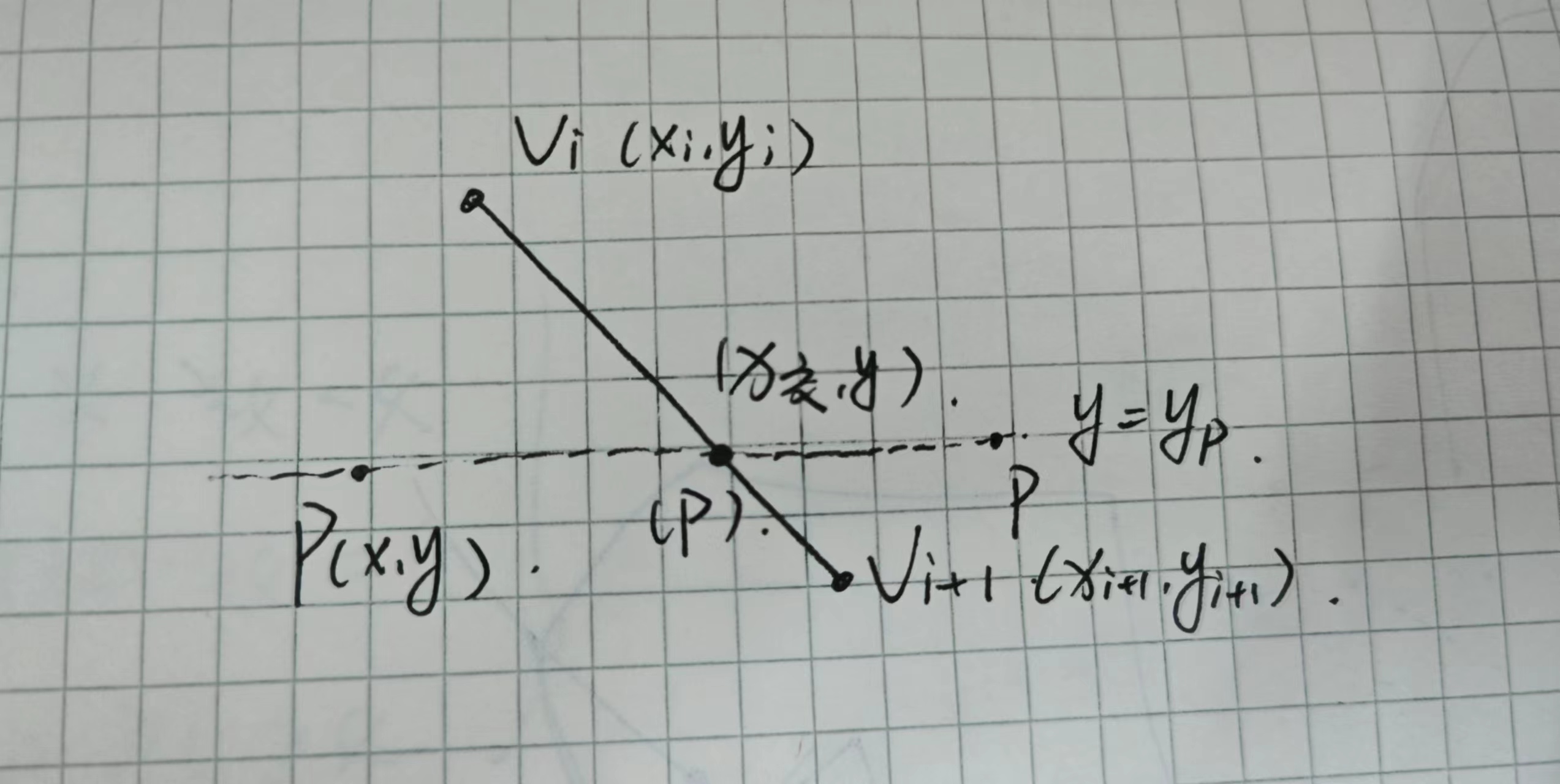

2.5.1 信号类型确定方法总结

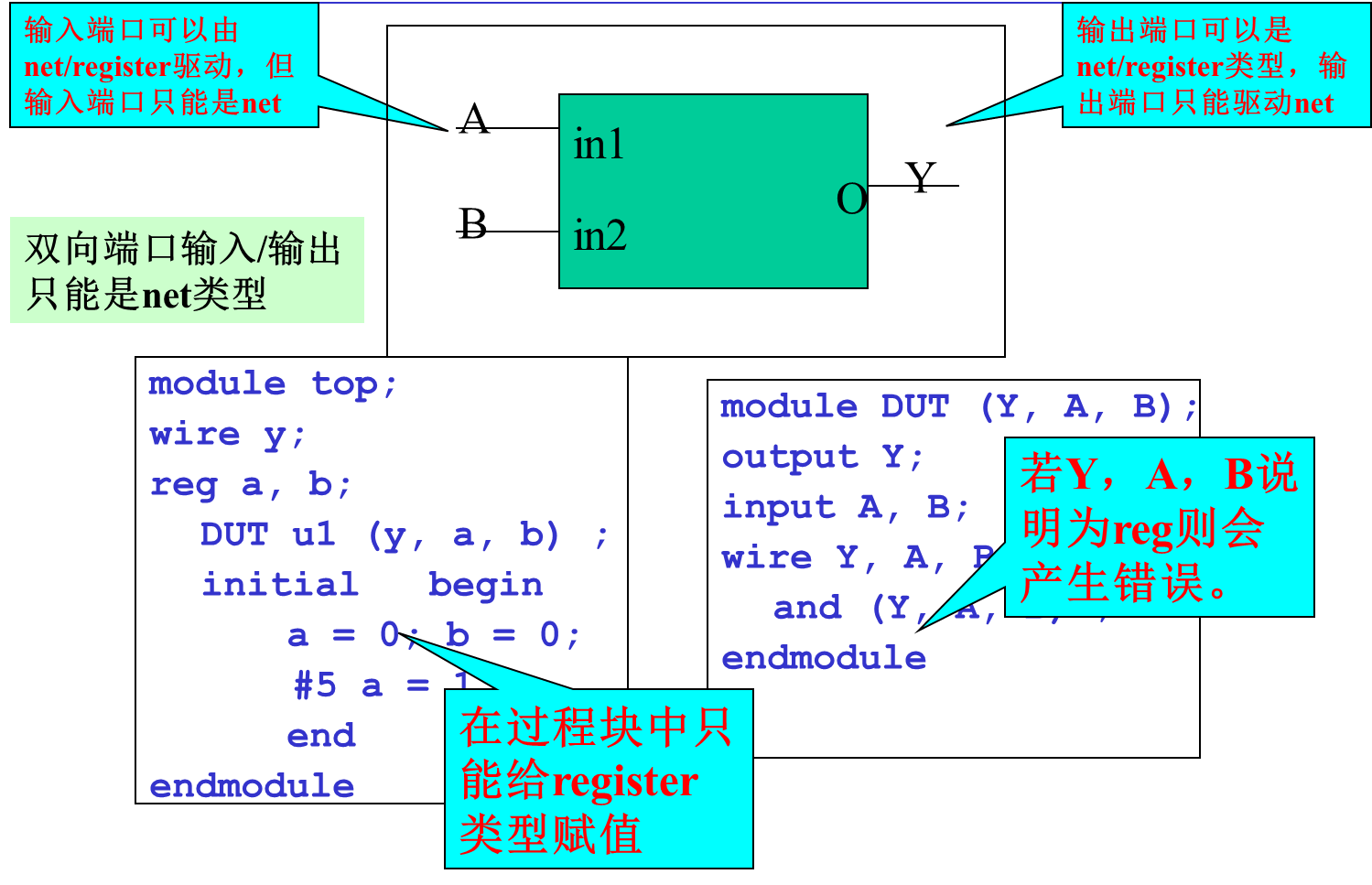

- 信号可以分为端口信号和内部信号。出现在端口列表中的信号是端口信号,其它的信号为内部信号。

- 对于端口信号,输入端口只能是net类型。输出端口可以是net类型,也可以是register类型。若输出端口在过程块中赋值则为register类型;若在过程块外赋值(包括实例化语句),则为net类型。

- 内部信号类型与输出端口相同,可以是net或register类型。判断方法也与输出端口相同。若在过程块中赋值,则为register类型;若在过程块外赋值,则为net类型。

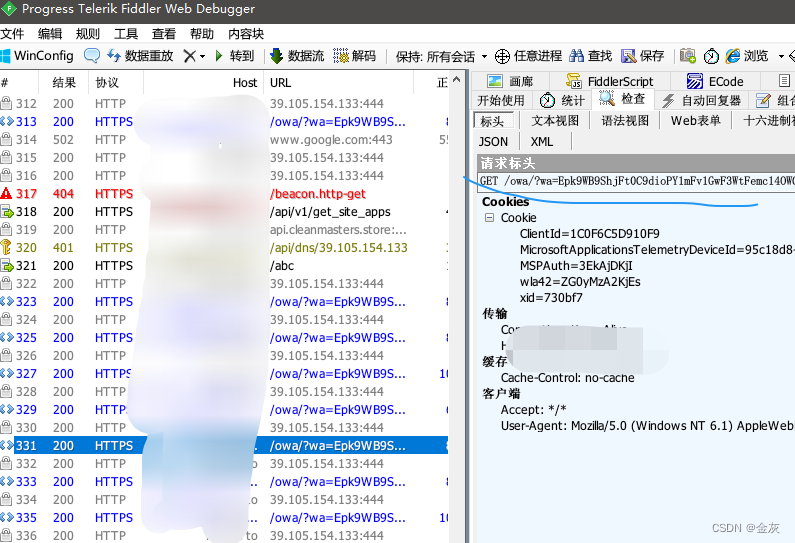

2.5.2 常出的错误及相应的错误信息(error message)

- 用过程语句给一个net类型的或忘记声明类型的信号赋值。

报错信息:illegal …… assignment. - 将实例的输出连接到声明为register类型的信号上。

报错信息:<name> has illegal output port specification. - 将模块的输入信号声明为register类型。

报错信息:incompatible declaration, <signal name> ……

2.5.3 选择数据类型时常犯的错误举例

修改前:

module example(o1, o2, a, b, c, d);

input a, b, c, d;

output o1, o2;

reg c, d;

reg o2

and u1(o2, c, d);

always @(a or b)

if (a) o1 = b; else o1 = 0;

endmodule

修改前编译信息:

Compiling source file "example.v"

Error! Incompatible declaration, (c) defined as input

at line 2 [Verilog-IDDIL]

"example.v", 5:

Error! Incompatible declaration, (d) defined as input

at line 2 [Verilog-IDDIL]

"example.v", 5:

Error! Gate (u1) has illegal output specification [Verilog-GHIOS]

"example.v", 8:

3 errors

修改后:

module example(o1, o2, a, b, c, d);

input a, b, c, d;

output o1, o2;

// reg c, d;

// reg o2

reg o1;

and u1(o2, c, d);

always @(a or b)

if (a) o1 = b; else o1 = 0;

endmodule

修改后编译信息:

Compiling source file "example.v"

Error! Illegal left-hand-side assignment [Verilog-ILHSA]

"example.v", 11: o1 = b;

Error! Illegal left-hand-side assignment [Verilog-ILHSA]

"example.v", 12: o1 = 0;

2 errors

微信公众号获取更多FPGA相关源码:

![[20] Opencv_CUDA应用之 关键点检测器和描述符](https://img-blog.csdnimg.cn/direct/374e3465fb48409d9bfcd459f633e143.png)