TDA4VH 高速链路设计指南阅读及考虑

0、说明

本人目前做相关域控制器相关内容,目前正在研究TDA4的开发,目前正在对高速电路的的相关设计进行考虑,下面对TI官方提供的高速电路的设计的开发文档进行学习和分享:

1、高速系统架构介绍及PCB阻抗连续性方法介绍

1.1 TDA的高速系统

TDA可以使用总计16路serdes信号,用于PCIE、USB、SGMII、DP等。在我的应用中,我主要使用了PCIE、SGMII,本文将主要介绍这两种总线的走线方式

1.2 高速接口设计指南

- 高速的协议决定了差分信号: 同时满足单端和差分布线的阻抗要求

- 紧耦合的差分布线不好。宽度限制将很大的影响阻抗的变化的,生产困难。 建议使用松散耦合

- 松散耦合 PCB 差分信号使阻抗控制变得更加容易。布线越宽, 间距越大, 避开障碍物就越容易( 因为每条布线相

对于另一条布线的位置不够固定), 并且布线宽度变化不会对阻抗产生太大影响, 因此更容易在信号长度上保持

精确的阻抗。对于较长的布线, 较宽的布线还会减轻趋肤效应, 通常能够实现更佳的信号完整性, 眼图张开度更

大

- 松散耦合 PCB 差分信号使阻抗控制变得更加容易。布线越宽, 间距越大, 避开障碍物就越容易( 因为每条布线相

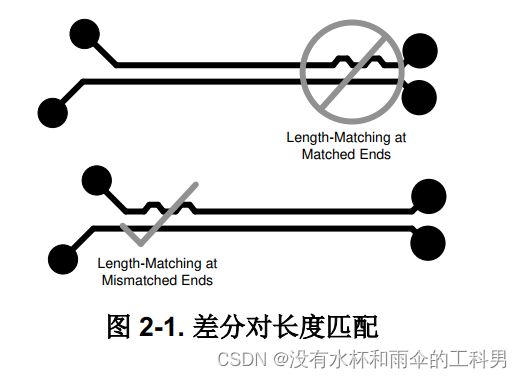

- 差分信号长度匹配,TX 和 RX 不需要等长,是不用做的。 内部需要做等长的话,需要在差不匹配的地方附近

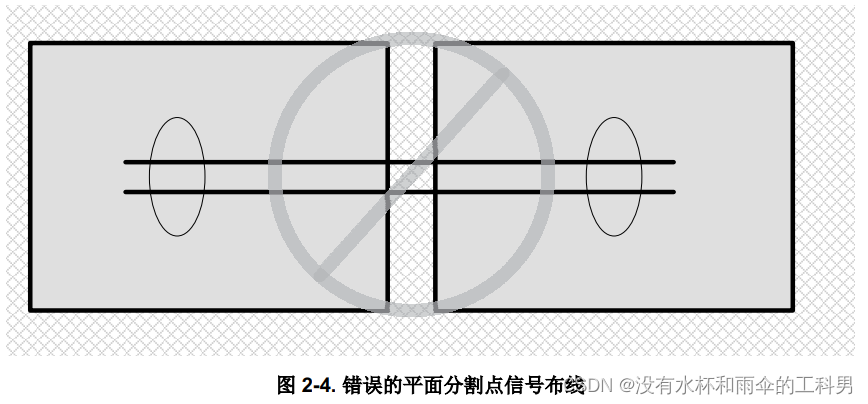

- 信号参考平面:建议信号层的上下完整实心的地参考平面上,不要经过分割点:

- • 不平衡的电流流动产生过多的辐射发射

• 由于串联电感增加, 信号传播出现延迟

• 干扰相邻信号

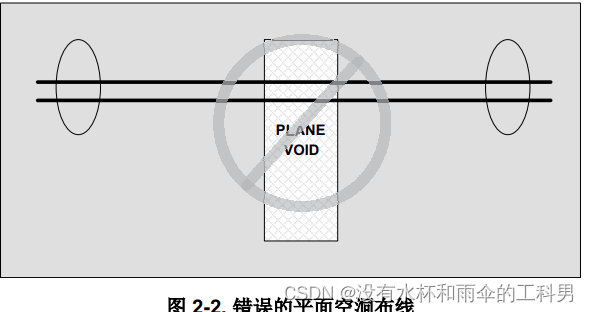

• 信号完整性降低( 即更多抖动和信号幅度降低) - 例子如下:

- 不穿过空心区

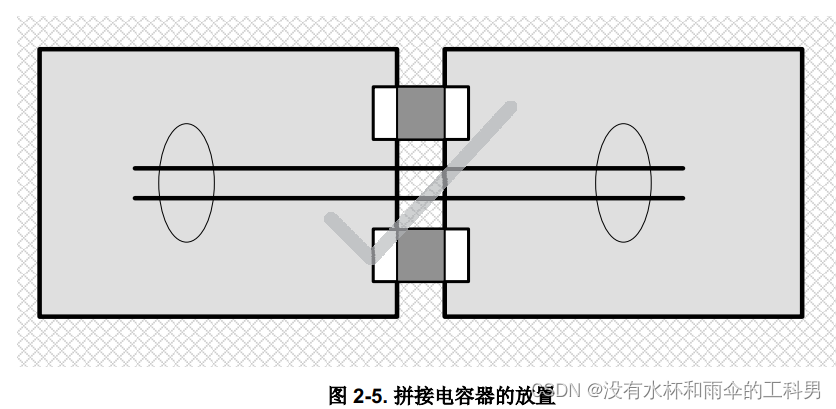

- 必须穿,经过1uF或者更低的电容作为耦合平面回路

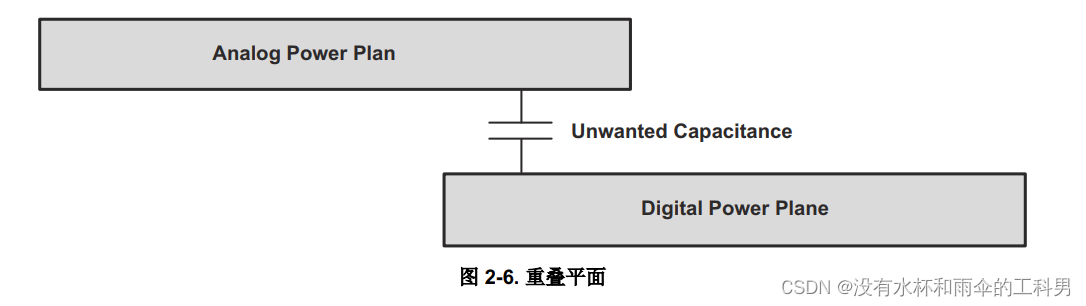

- PCB规划时,互不参考的平面应当不产生不要的寄生电容:

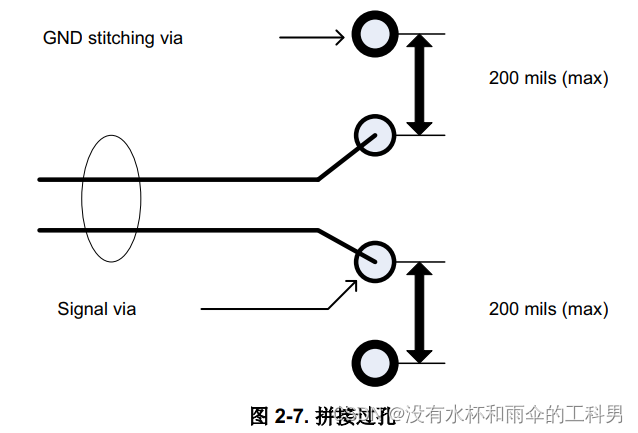

- 增加地过孔作为我不同地平面的参考中转:

- TI不建议:电源平面作为高速参考平面, 否则最好使用交流耦合电容和接地过孔实现返回路径。

- 不穿过空心区

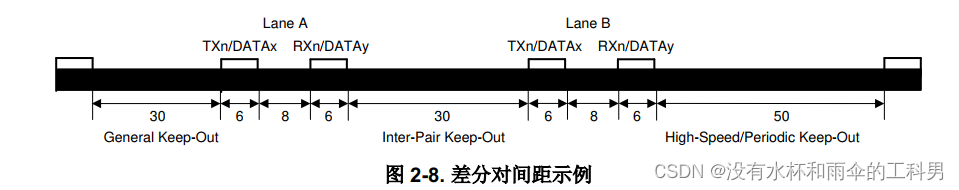

- 差分走线的距离建议:

- 5W原则,遇到时钟或者其他周期信号需要有至少50mil的隔离:

- 5W原则,遇到时钟或者其他周期信号需要有至少50mil的隔离:

- checklist

- • 请勿在任何高速差分信号上放置探头或测试点。

• 请勿在晶体、振荡器、时钟信号发生器、开关电源稳压器、安装孔、磁性器件或使用/复制时钟信号的 IC 下方

或附近布置高速布线。

• BGA 破孔后, 使高速差分信号远离 SoC, 其原因为内部状态变换时产生的高电流瞬变难以滤除。

• 如有可能, 在 PCB 的顶层或底层( 与接地层相邻) 布置高速差分对信号。 TI 不建议对高速差分信号进行带状

线布线。 ( 或建议在设计中对所有高速串行器/解串器信号进行带状线布线。这可以提供更好的受控阻抗。此

外, 通过在接地平面之间布置引线, 可以最大限度地缓解由于 EMI 导致的信号质量下降问题。 )

• 确保将高速差分信号布置在距离参考平面边缘 ≥ 90mil 的位置。

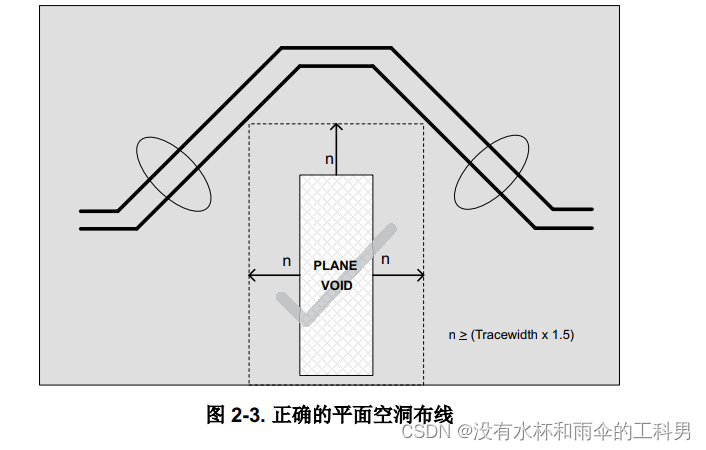

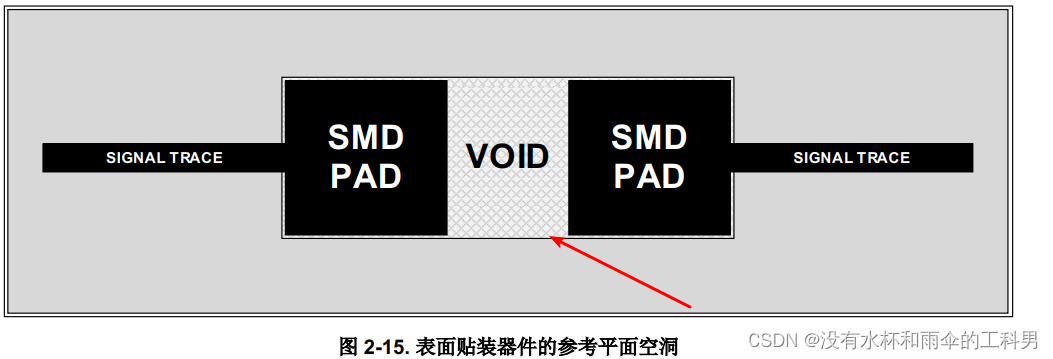

• 确保将高速差分信号布置在距离参考平面中的空洞至少 1.5W( 计算出的布线宽度 × 1.5) 的位置。当高速差分

信号上的 SMD 焊盘有空洞时, 此规则不适用。

• 在 SoC BGA 迂回布线之后维持一致的布线宽度, 以避免传输线路中存在阻抗失配现象。

• 最大限度地减小差分对之间的间距( 松散耦合

- • 请勿在任何高速差分信号上放置探头或测试点。

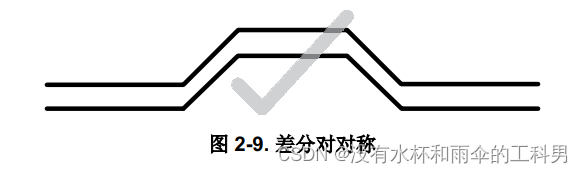

- 差分对称性:

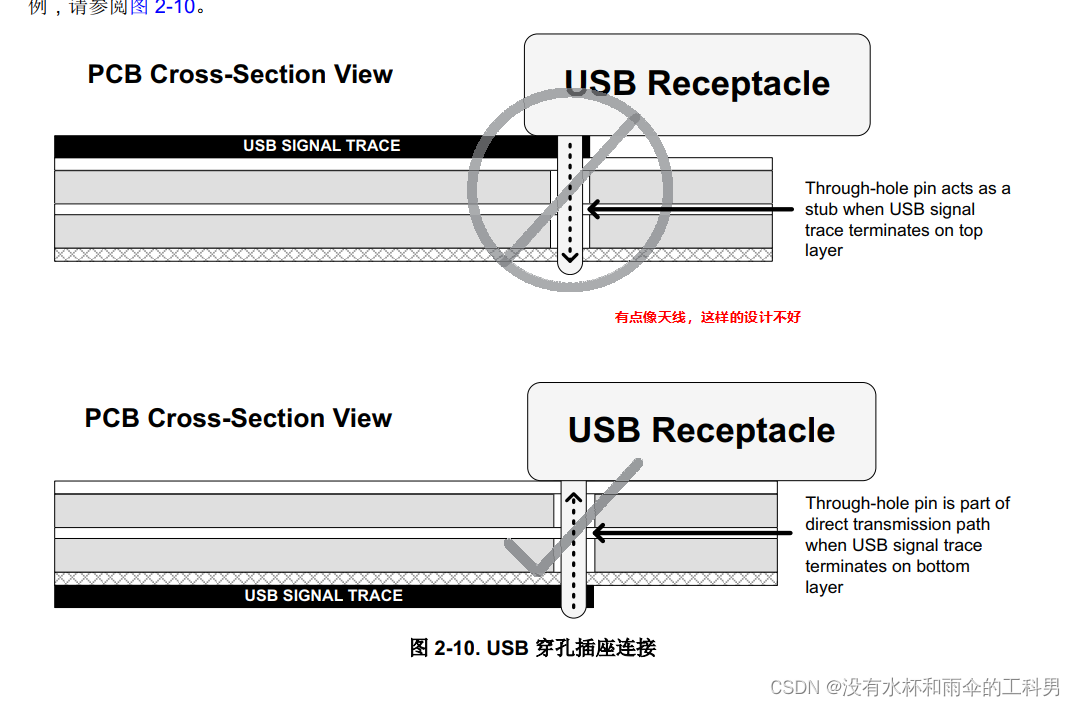

- 连接器和插座:

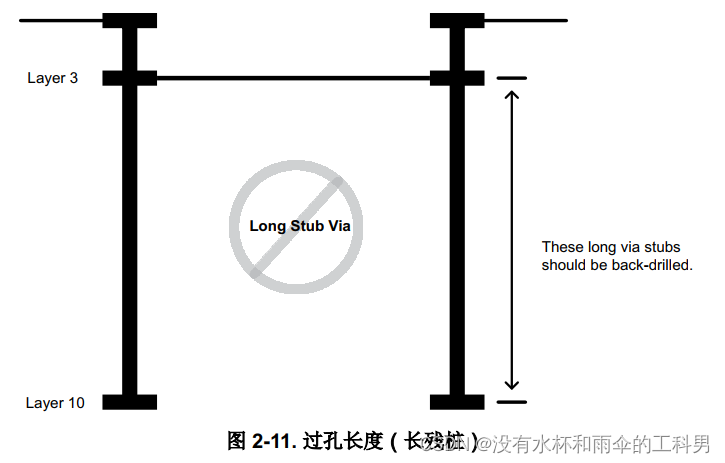

- 过孔不连续性:

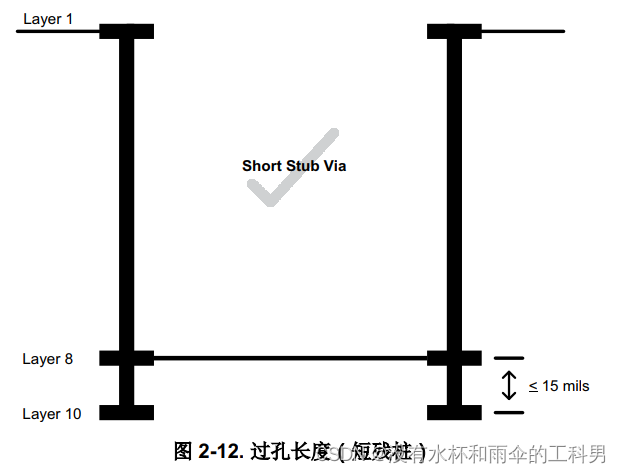

- 尽可能实现短残桩:

- 实现背钻:

- 背钻是一种 PCB 制造工艺, 即去除过孔残桩中不需要的导电镀层。若要进行背钻, 请使用直径比钻出原始过孔的

钻头稍大一些的钻头。这要求增加过孔的反焊盘直径以适合钻孔尺寸( 对于那些待移除的层), 以确保其他引线

或平面不会受到钻孔的影响。当过孔转换导致残桩长于 15mil 时, 对产生的残桩进行背钻可减少插入损耗并确保

它们之间不会共振。

- 背钻是一种 PCB 制造工艺, 即去除过孔残桩中不需要的导电镀层。若要进行背钻, 请使用直径比钻出原始过孔的

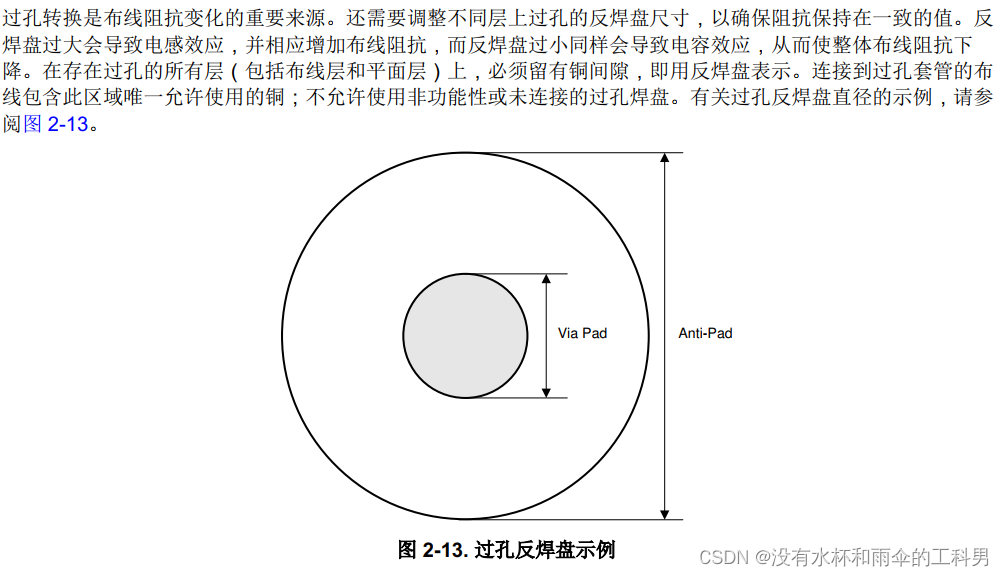

- 反焊盘:仿真确定合适的反焊盘大小,确保合适额阻抗匹配

- 差分对过孔相等

- 表贴器件连续性缓解

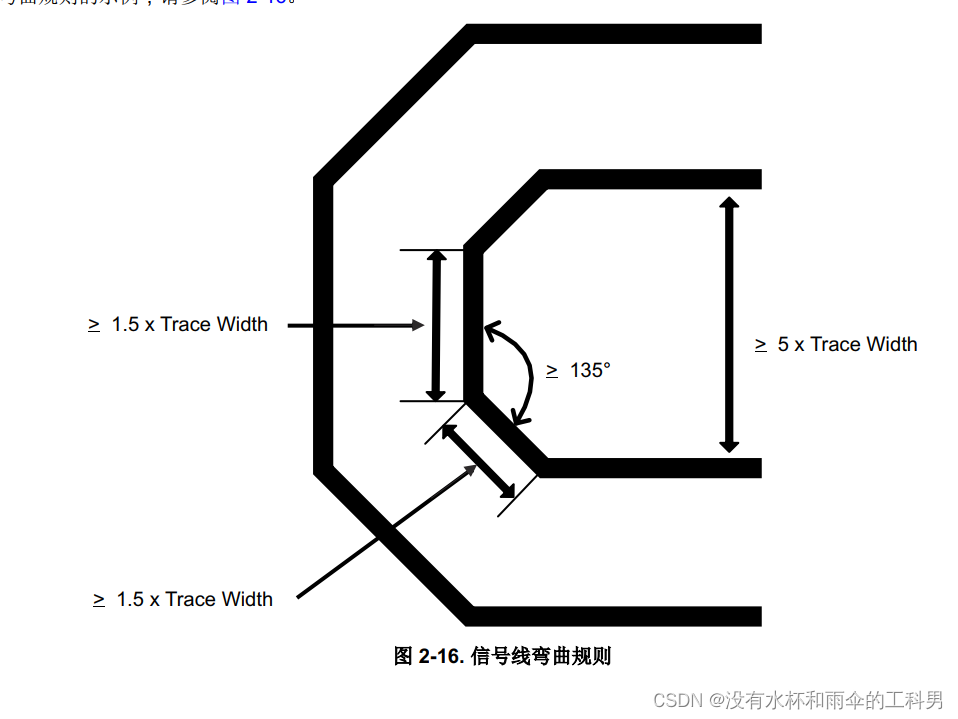

- 信号弯曲规范:

- 尽可能实现短残桩:

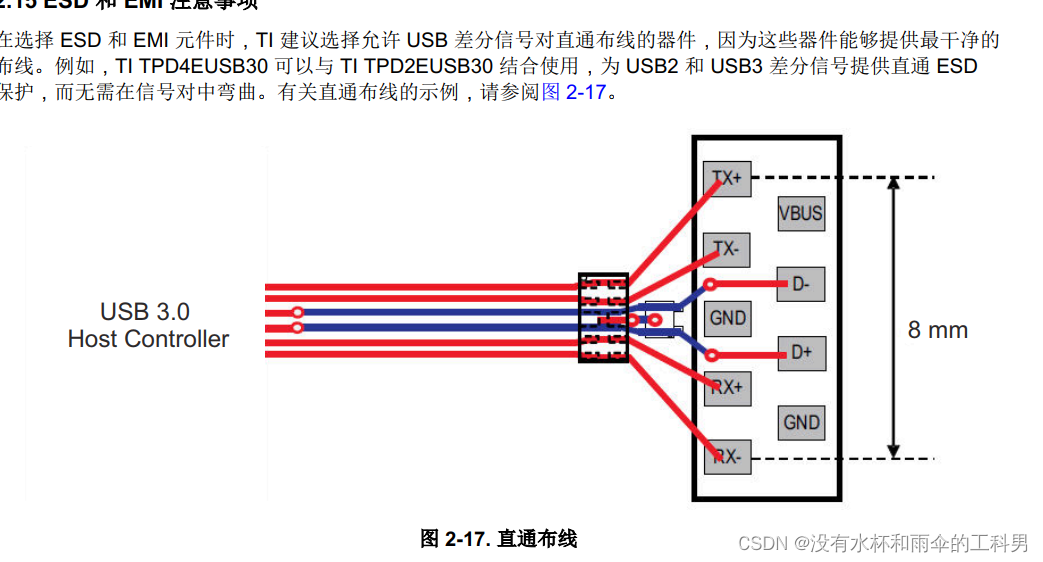

- ESD &EMI问题:

- • 将 ESD 和 EMI 保护器件放在尽可能靠近连接器的位置。

• 让任何未受保护的布线远离受保护的布线, 以尽量减少 EMI 耦合。

• 在 ESD 和 EMI 元件信号焊盘下方留出 60% 的空隙以减少损耗。 其他记地方接地之外

• 将 0402 0Ω 电阻器用于共模滤波器 (CMF) 无填充选项, 因为一般来说, 元件越大, 就会引入比 CMF 更多的

损耗。

• 将所有必要的信号对交流耦合电容器放置在 CMF 的受保护侧, 尽可能靠近 CMF。

• 如果需要过孔过渡到 CMF 层, 请确保过孔尽可能靠近 CMF。

• 确保交流耦合电容 + CMF + ESD 保护部分的整体布线尽可能短, 并尽可能靠近连接器

- • 不平衡的电流流动产生过多的辐射发射

2、PCIE总线

2.1系统架构

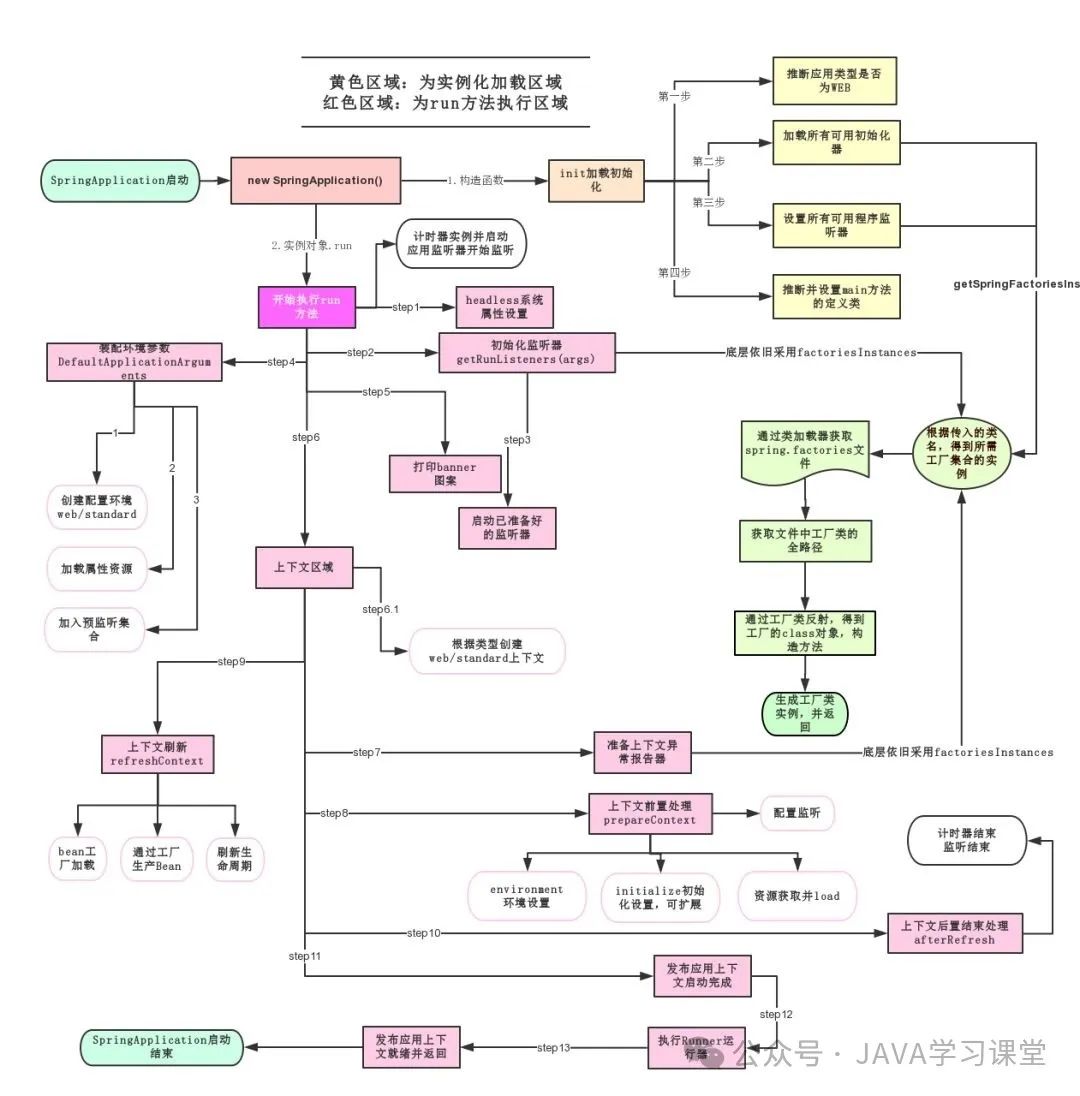

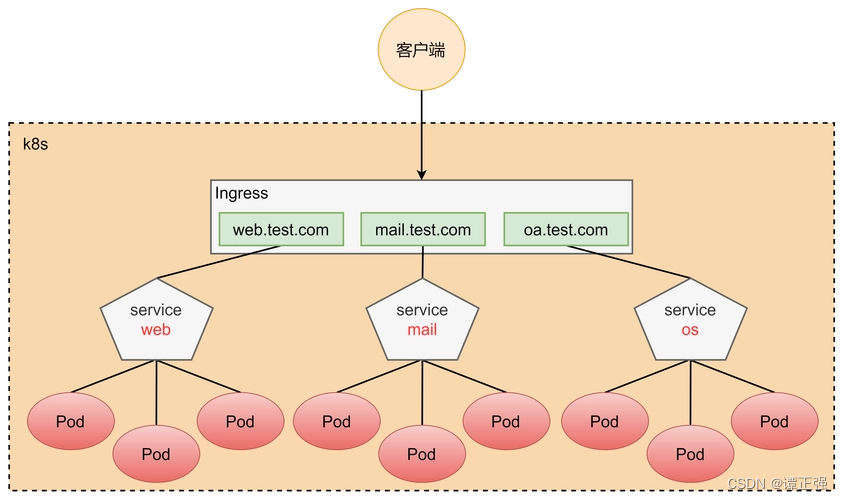

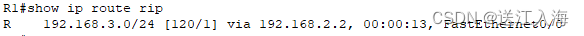

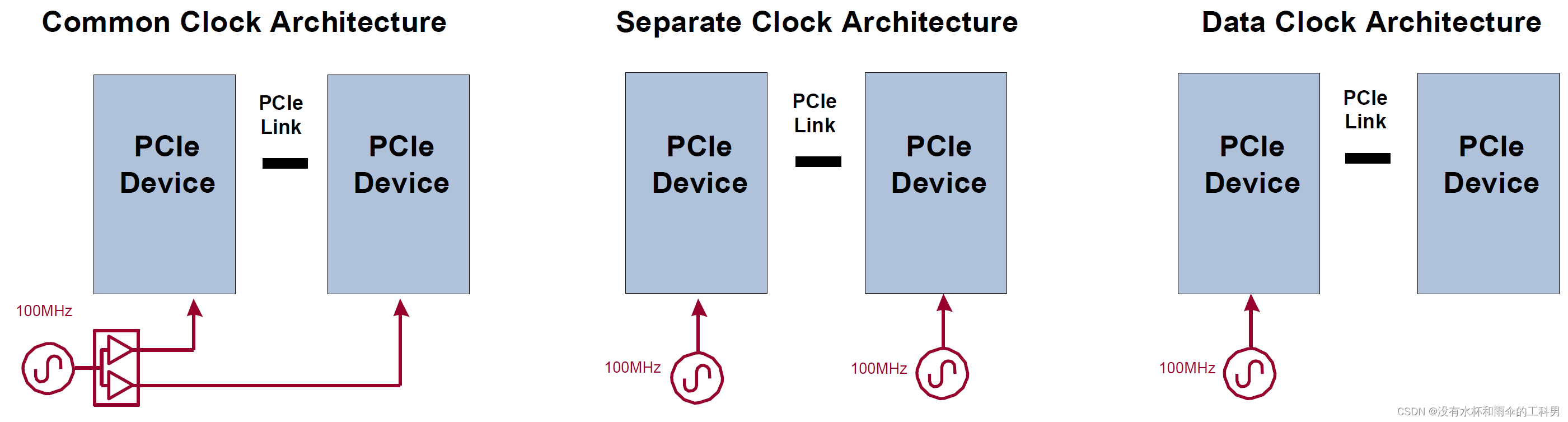

PCIE 总线是系统内部最常用的高速总分结构的网络,其时钟架构总共由如下三种:

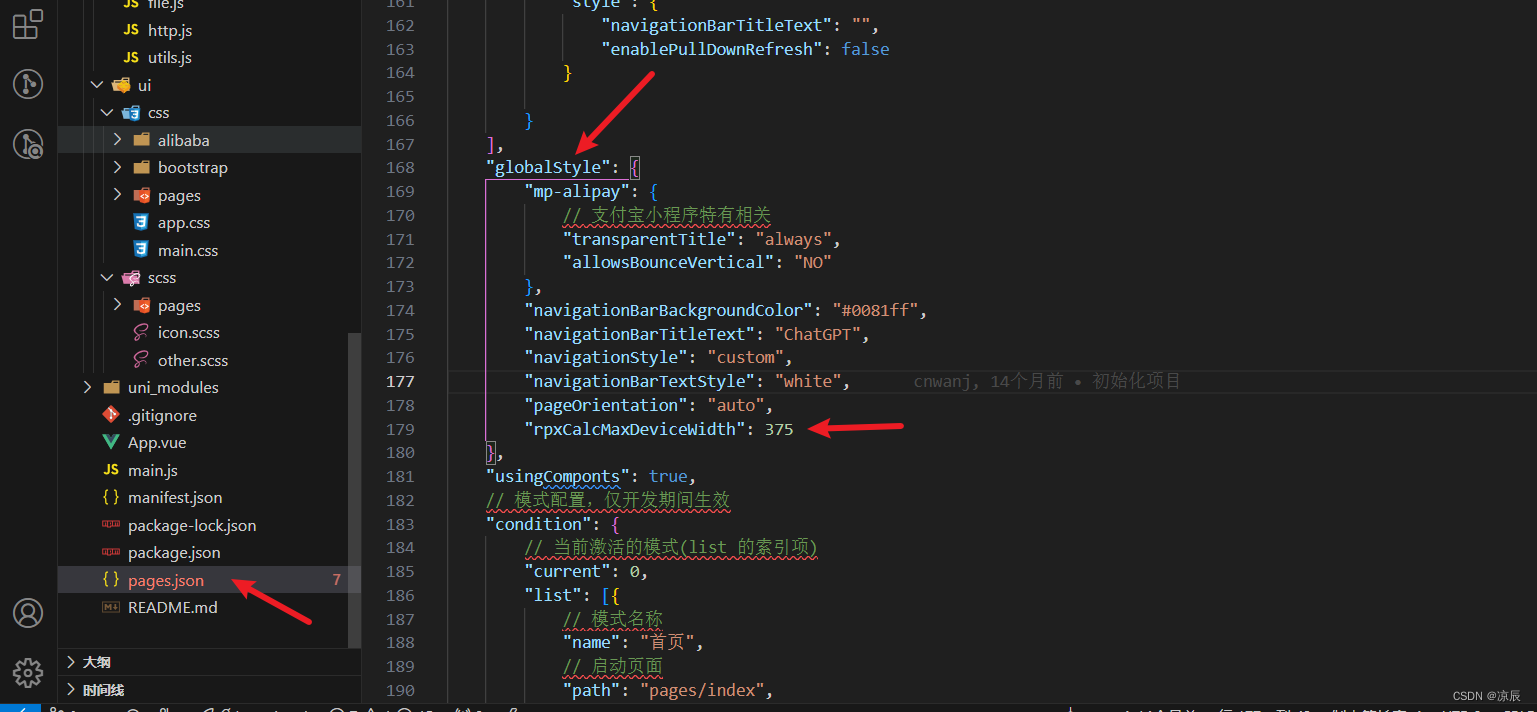

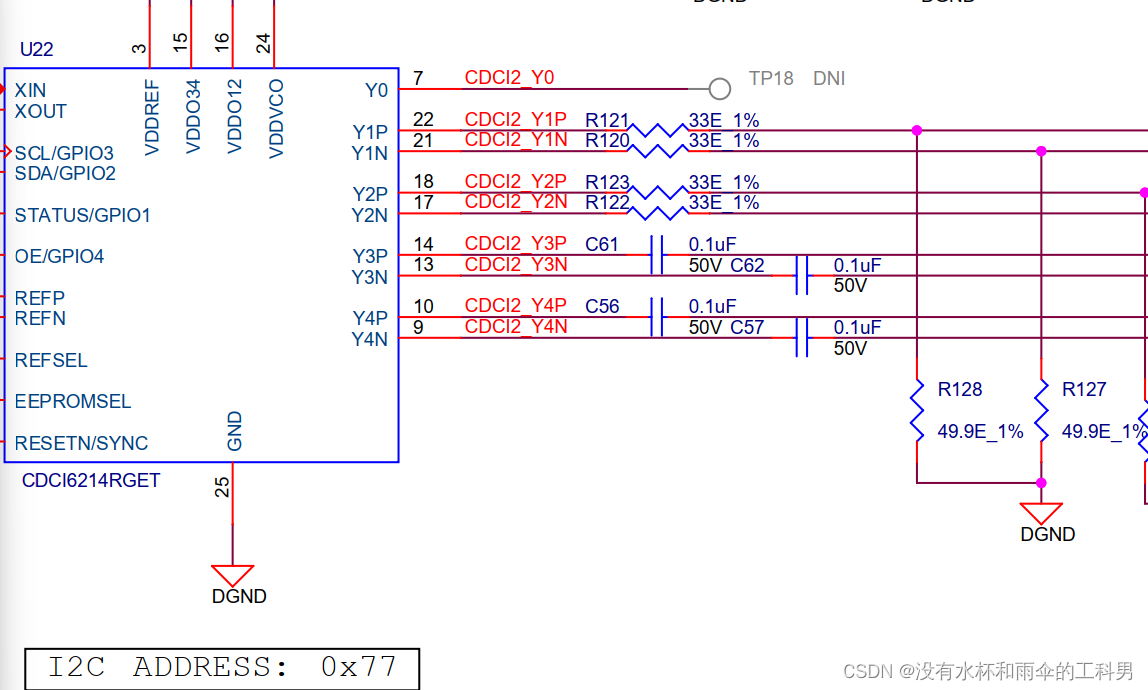

TDA4的开发板中介绍了一种CC架构的连接方式,其通过CDCI6214RGET IC clock generator,分别产生两路时钟信号,分别给从节点和TDA如上图1;

根据TDA4的官方手册,芯片的内部的PCIE_REFCLK是可以作为100MHz输出的。如下图:

因此,根据为了确认其时钟信号可否由Serdes接口设备进行产生,然后直接输出的从设备,根据 最新发布的文档,其可以按照如下结构进行连接,因此,其可以通过ref_clk进行时呼出。

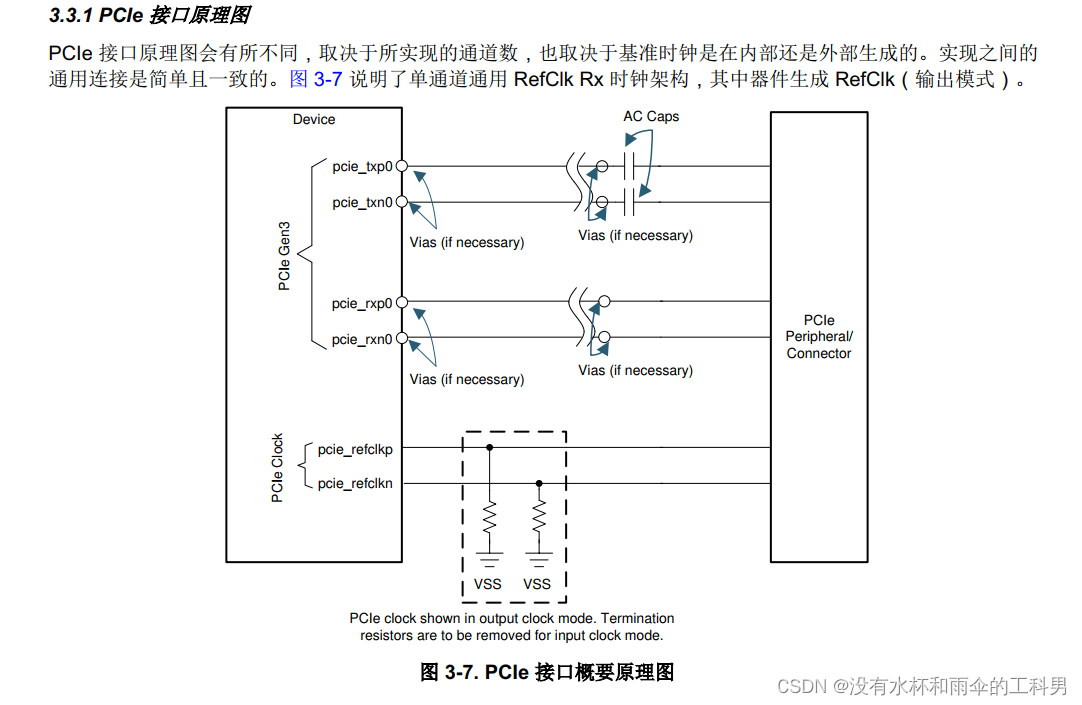

根据如下的架构图,需要说明如下几个问题:

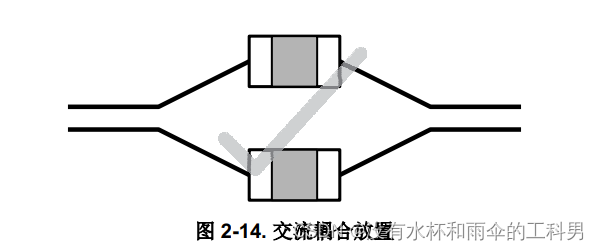

- PCIE的AC耦合电容通常位于发送端

- PCIE 的规范要求支持极性反转,因此极性无所谓

- PCIE 支持通道交换,因此通道无所谓

- REF 的CLK连接:外部CLK&输出REF CLK模式:

- 外部REFCLK: 通用外部100MHz的始终,分别给器件和外设

- 对外设时钟要求: 提供符合PCIe REFCLK规范的100M的 HCSL始终。

- 如果要用LVDS的时钟,则许满足如下要求:

- 时钟源的端接需要100 ohms 的差分。

- 输出REFCLK:100M HCSL的时钟,由IC 给外设----这也是此处我们使用的方式

- refp和refn上输出,HCSL,并0.1uF的电容放在输出端进行耦合-0402封装

- 输出模式下,REFCLKP和REFCLKN的近侧的差分阻抗是要求,50ohms的。

- 外部REFCLK: 通用外部100MHz的始终,分别给器件和外设

--- 遗留问题:

根据如上的说明,TI认为他的PCIE的CLK要按照100ohms 的差分阻抗走,但PCIE GEN3 通常的差分走线是85ohms 的差分,下来我会再次与TI进行更多的确认(目前得到的消息:TI认为PCIE 规范上说明了可以85是可以的,但是仍然建议使用TI的100ohms 的差分)

综合如上信息的我的设计如下:CLK 均按照100ohms 的差分走线,data lane 按照要求的85ohms 的差分走线。

2.2 走线说明

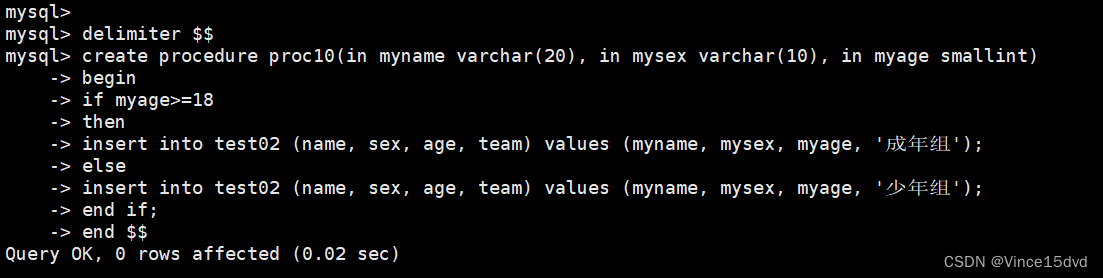

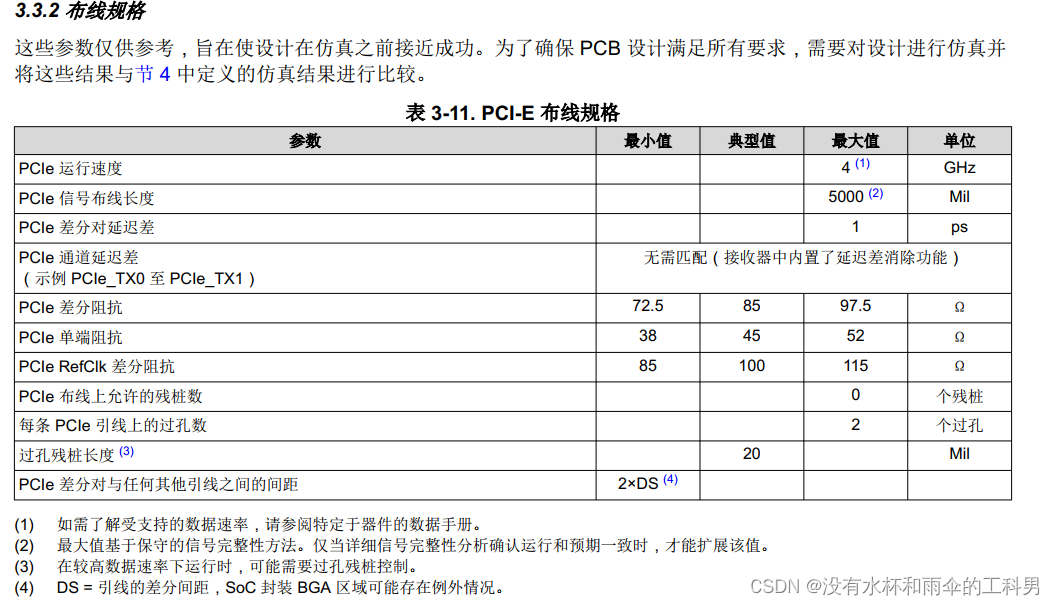

PCIE 信号布线长度,仅作为参考,需要加进行完成性方仿真,简单来说:5000mil= 12.7cm,

图中的关键规格说明:

- PCIE的引线上最多两个过孔: 芯片BGA封装,引出后到AC耦合电容后,再走线到内层,总计两个过孔,随后到达连接器,总计4个过孔才是。

- PCIE不能有任何残桩,因此back drill 是必要的。

- PCIE差分对于其他任何引线的距离,要大于2倍的的差分距离。 (尽可能远),PCIE的数据线之间的走线也应该可满足该情况。

3 CSI总线

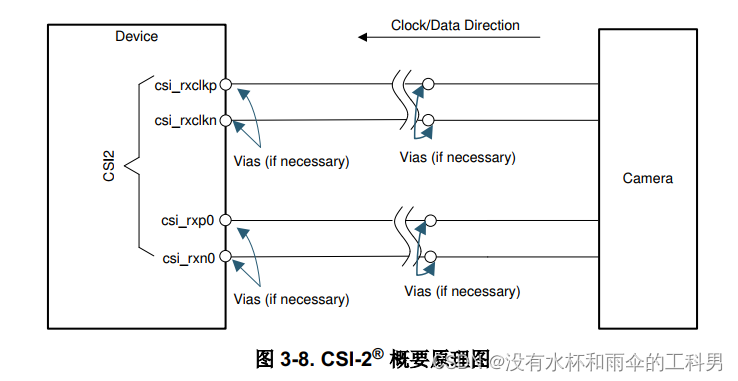

3.1 总线连接图:

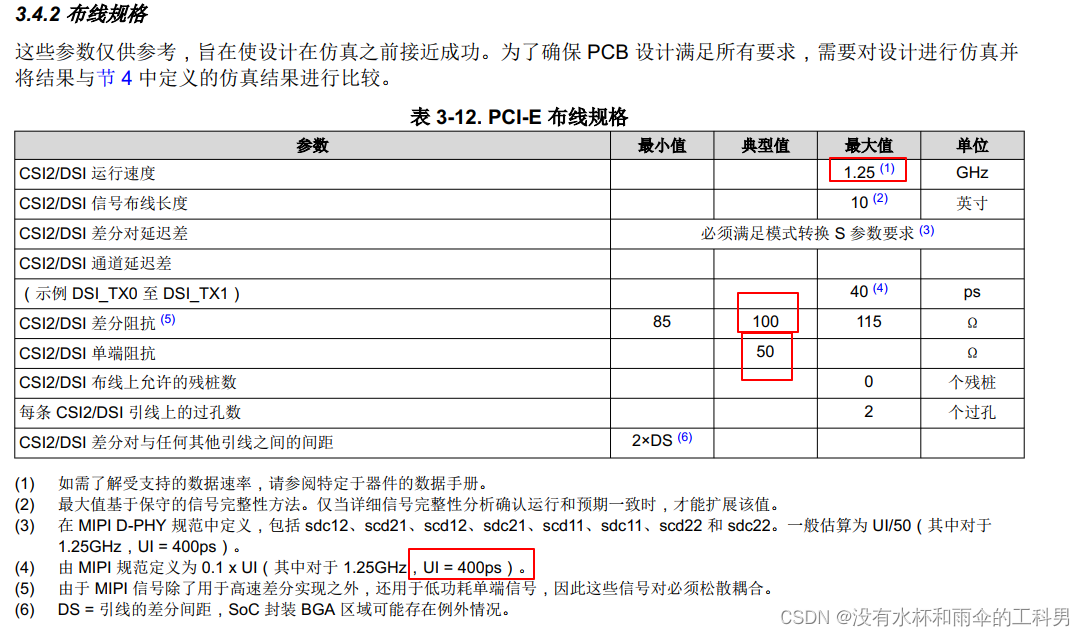

3.2 布线要求:

4

4

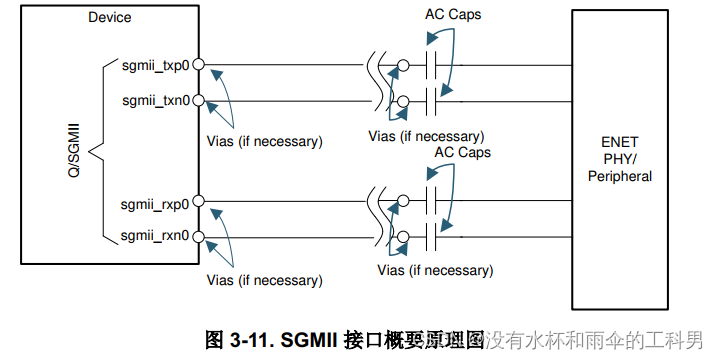

4 SGMII 接口设计

- 耦合电容按照100nF设计

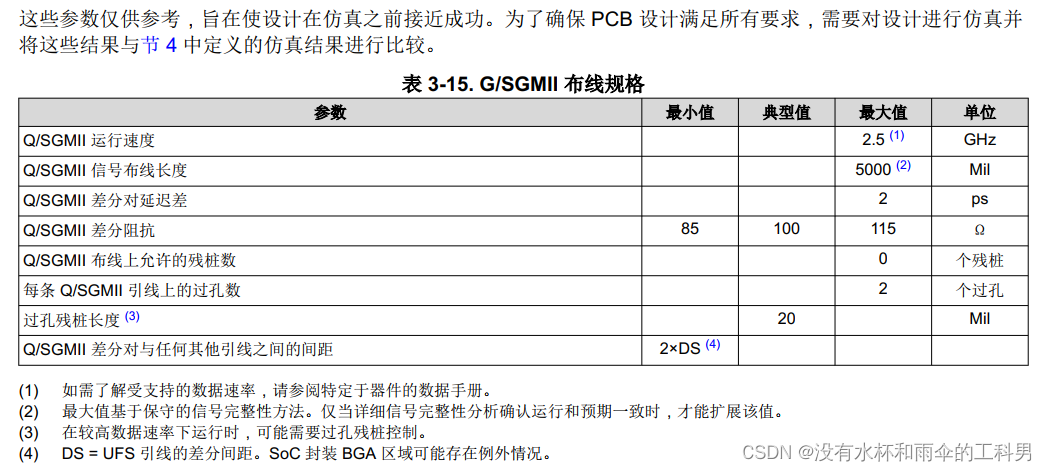

- 布线规格: