引言

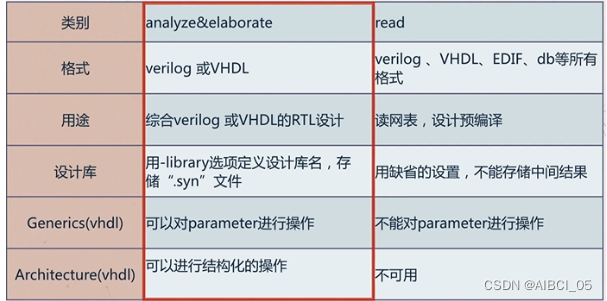

DC读入设计文件有两种方式,一是read指令,二是 analyze&elaborate 的组合。下文将介绍两者的异同。

read

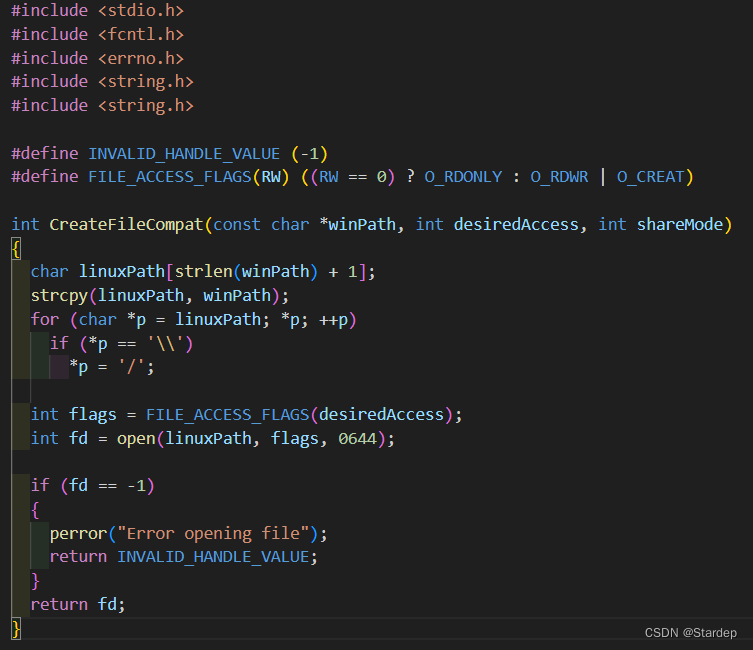

具体为

read -format verilog[db,vhdl...] file #dcsh model

read_db file.db #tcl model

read_verilog file.v #tcl model

read_vhdl file.vhd #tcl model

如果读入单个文件可以使用指令。

read_verilog alu.v

如果需要读入多个文件可以使用以下指令。

# 设置verilog文件所在的目录rtl

set design_path "rtl"

set verilog_files [glob -nocomplain -type f $design_path/*.v]

foreach file $verilog_files {

read_file -format verilog $file

}

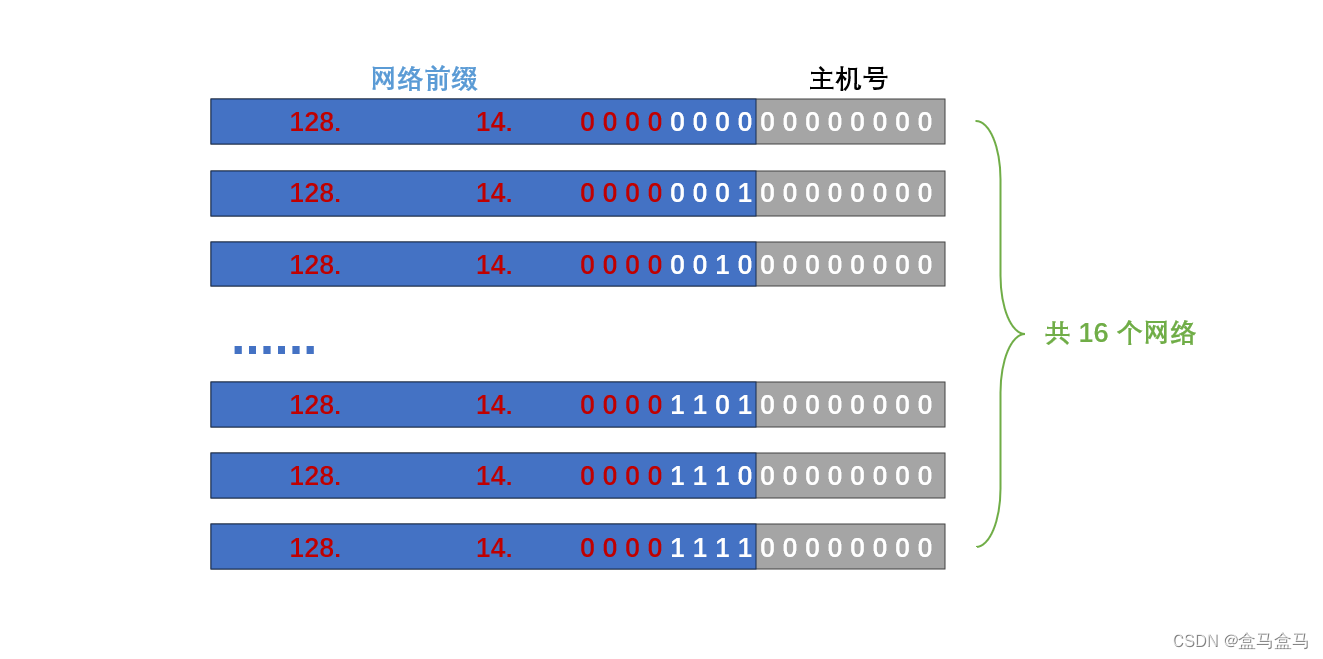

analyze & elaborate

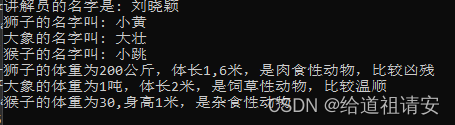

语法格式为:

analyze [-library library_name] [-format verilog | vhdl | sverilog] file_list

# library:指定中间结果存放的库,即 Linux 系统下的一个目录,默认为当前目录,也可以用 define_design_lib 命令指定

# format:HDL 源文件的类型,即 verilog 或 vhdl

# file_list:源代码文件名列表,文件名的指定可以通过TCL的链表命令 {}、“”、[list file_name] 等三种方法之一完成

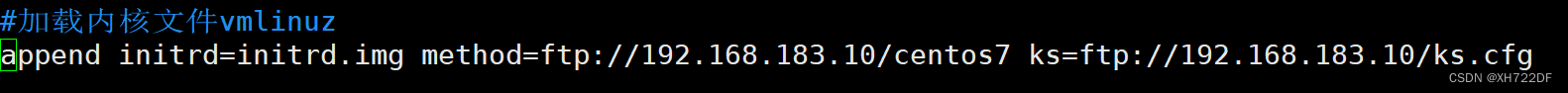

elaborate design_name [-library library_name] [-parameters param_list]

# deisgn_name:指需要进行描述的设计

# library:用于保存设计的结构级描述

# parameters:指定给设计传递的参数,若省略则参数使用缺省值;参数用“”括起来

如果需要读入多个文件可以使用以下指令。

set top_design top

set source_file [sh find ./rtl/*.v]

analyze -format verilog $source_file

elaborate $top_design

当然以上脚本是可以正确的,但是他会在默认目录下(dc运行的路径)生成一系列analyze生成的中间文件(.mr,.syn…),这会导致该目录很乱。

有两种解决方法,法一是新建一个work文件夹,在work文件夹下运行dc。法二是通过define_design_lib指定library,将中间结果存放在该lib种,指令如下。

set work_path work

define_design_lib work -path $work_path

set top_design top

set source_file [sh find ./rtl/*.v]

analyze -format verilog -lib work $source_file

elaborate $top_design

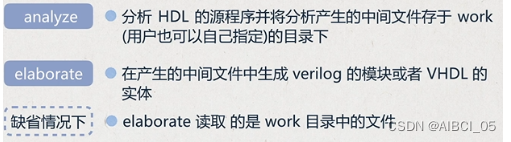

异同

其实read命令其实是一步完成analyze&elaborate的工作,而analyze&elaborate仅限用于VHDL和verilog。虽然两者都是读入设计文件,但是存在一些区别。

需要特别关注的是以下三点:

- 对于已经analyze过的工程只需要elaborate,不需要重新读入,可以减少综合时间;

- read可以读除了verilog和VHDL外,还可读db等文件;

- analyze&elaborate可以对parameter进行操作,read中parameter只能保持默认综合,不可改变。