Chisel是什么?

Chisel的全称为Constructing Hardware In a Scala Embedded Language,是一个基于Scala的DSL(Domain Specific Language,特定领域专用语言)。2012年,加州大学伯克利分校(UC Berkeley)的Jonathan Bachrach等人在计算机体系结构会议DAC(Design Automation Conference)上发表了文章Chisel: Constructing Hardware in a Scala Embedded Language,对Chisel语言进行了详细的描述,参考Chisel的官方网站(https://www.chisel-lang.org/)描述:

The Constructing Hardware in a Scala Embedded Language (Chisel) is an open-source hardware description language (HDL) used to describe digital electronics and circuits at the register-transfer level that facilitates advanced circuit generation and design reuse for both ASIC and FPGA digital logic designs.

Chisel adds hardware construction primitives to the Scala programming language, providing designers with the power of a modern programming language to write complex, parameterizable circuit generators that produce synthesizable Verilog. This generator methodology enables the creation of re-usable components and libraries, such as the FIFO queue and arbiters in the Chisel Standard Library, raising the level of abstraction in design while retaining fine-grained control.

大致翻译如下:Chisel是一种开源,在RTL级别描述数字电子电路的硬件描述语言,能方便ASIC和FPGA的高级电路生成和设计重用。

Chisel将硬件构造原语添加到Scala编程语言中,为设计者提供了现代编程语言的能力,可以编写复杂的、可参数化的电路生成器,从而生成可综合的Verilog。这种生成器方法能够创建可重用的组件和库,例如Chisel标准库中的FIFO队列和仲裁器,从而提高设计中的抽象级别,同时保持精细的控制。

2,Chisel有什么优点?

1)拥有强大而优雅的库,包含各种数据集合。

2)具有严格的类型系统,有助于在开发周期的早期(编译时)捕获大量错误。例如代码整合时模块端口连接只需要一行语句就可以自动完成;在verilog中常见的位宽连线问题,在Chisel中可以不用申明位宽,编译器在编译过程中会自动推断其位宽,避免人为错误。

3)具有面向对象和强大的函数式编程方式。

3,Chisel如何工作?

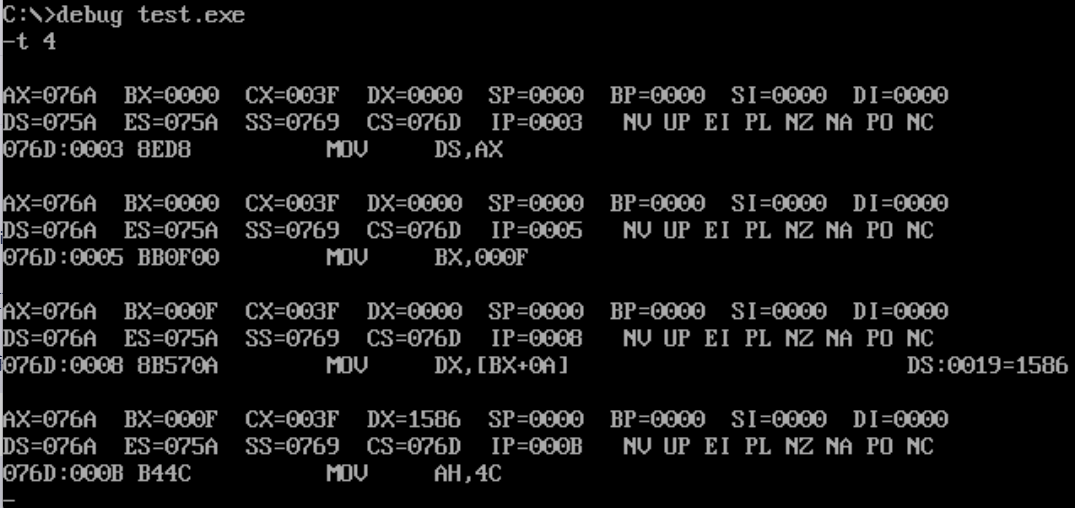

目前Chisel需要先转换成verilog,大致流程大致如下:

1)Chisel编译器,首先将Chisel代码转换成AST中间数据;

2)Firrtl编译器,再将AST数据转换成Firrtl代码;

3)Firrtl编译器,将Firrtl代码转换成最终的Verilog代码。

以下是官网提供的一个例子:

import chisel3._

import chisel3.util._

class Blinky(freq: Int, startOn: Boolean = false) extends Module {

val io = IO(new Bundle {

val led0 = Output(Bool())

})

// Blink LED every second using Chisel built-in util.Counter

val led = RegInit(startOn.B)

val (_, counterWrap) = Counter(true.B, freq / 2)

when(counterWrap) {

led := ~led

}

io.led0 := led

}

object Main extends App {

// These lines generate the Verilog output

println(

new (chisel3.stage.ChiselStage).emitVerilog(

new Blinky(1000),

Array(

"--emission-options=disableMemRandomization,disableRegisterRandomization"

)

)

)

}

编译后,生成的verilog代码是这样的:

module Blinky(

input clock,

input reset,

output io_led0

);

reg led; // @[main.scala 11:20]

reg [8:0] counterWrap_value; // @[Counter.scala 62:40]

wire counterWrap_wrap_wrap = counterWrap_value == 9'h1f3; // @[Counter.scala 74:24]

wire [8:0] _counterWrap_wrap_value_T_1 = counterWrap_value + 9'h1; // @[Counter.scala 78:24]

assign io_led0 = led; // @[main.scala 16:11]

always @(posedge clock) begin

if (reset) begin // @[main.scala 11:20]

led <= 1'h0; // @[main.scala 11:20]

end else if (counterWrap_wrap_wrap) begin // @[main.scala 13:21]

led <= ~led; // @[main.scala 14:9]

end

if (reset) begin // @[Counter.scala 62:40]

counterWrap_value <= 9'h0; // @[Counter.scala 62:40]

end else if (counterWrap_wrap_wrap) begin // @[Counter.scala 88:20]

counterWrap_value <= 9'h0; // @[Counter.scala 88:28]

end else begin

counterWrap_value <= _counterWrap_wrap_value_T_1; // @[Counter.scala 78:15]

end

end

endmodule

4,搅局者Chisel语言为何难以推广?

之所以将Chisel语言定位为硬件描述语言(HDL)的搅局者,是因为Chisel已经在RISC-V上有很多应用,例如国内的香山开源处理器就是用Chisel编写的。然而,Chisel在工业界却难觅踪影,了解者甚少,还没有被工业界接受,笔者认为有以下几点原因:

1)Chisel本质上还是Scala语言,因此要学习Chisel,需要具备Scala语言的基础,而scala是一门相对较难的语言。对广大前端电路设计者,如果没有面向对象编程基础和函数式编程经验,学起来会非常吃力,也很难在短期之内掌握;

2)Chisel需要先转换成verilog,而转换后的verilog信号名有大量的命名替换(Chisel源码修改后原来的名称可能发生变化),这会给问题定位和代码覆盖率收集带来很多障碍。这一缺点几乎是致命的。

3)主流的EDA工具对Chisel还不支持,例如常见的仿真工具VCS,Xcelium,综合工具DC,GENUS等都不支持。

4)还有一点是个人使用的感受:Chisel采用sbt工具构建,而sbt每次检查依赖库时速度较慢;对硬件要求高,可能需要专门的服务器,例如,开源的香山开源处理器,开发环境建议内存最低 32G,推荐 64G 及以上。

![path[1][0] path[1][1:-1] [path[1][-1] 分别怎么取的](https://img-blog.csdnimg.cn/direct/56f75a07770241a49d4c92c940efb33b.png)