Tri Mode Ethernet MAC IP

核结构

时钟网络

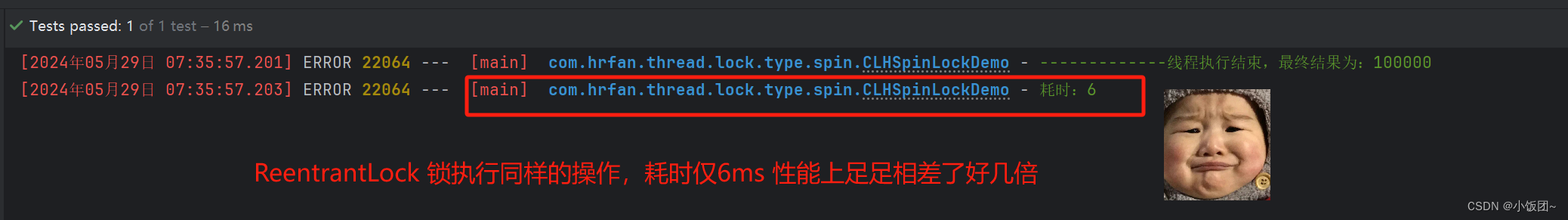

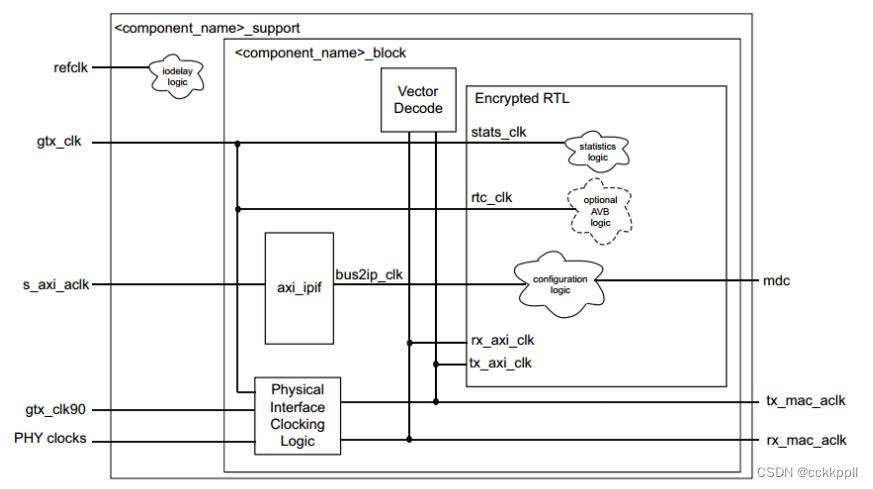

IP 核内部时钟网络结构如下图所示。其中,tx_mac_aclk 为 AXI-Stream 发送接口的同步时钟,

rx_mac_aclk 为 AXI-Stream 接收接口的同步时钟。由于在设计中没有使用 MDIO 接口,所以不存在时钟信号 mdc。 gtx_clk 为 IP 核工作的全局时钟源,频率 125MHz。s_axi_aclk 为 AXI-Lite 接口的同步时钟。 其余时钟 refclk、gtx_clk90 等均与 GMII、RGMII 接口与外部 PHY 芯片连接有关,由于设计中 IP 核与 1G/2.5G Ethernet PCS/PMA or SGMII 连接。因此,不需要使用这些时钟。

用户接口

这里对一些重要的用户接口进行说明,其他接口可参考 IP 核手册。

AXI-Stream

接收接口

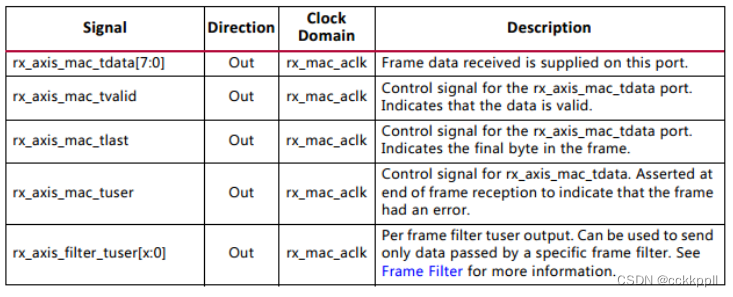

AXI-Stream 接收接口信号如下图所示。用户通过该接口接收从 IP 核输出的以太网数据包。需要

注意的是,接收接口没有使用 AXI-Stream 标准中的 tready 信号。这代表接收端需要具备持续接收数据的能力,防止出现数据来不及接收而产生溢出。

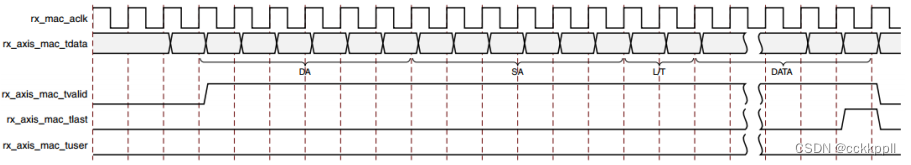

AXI-Stream 接收接口时序如下图所示。

AXI-Stream 发送接口

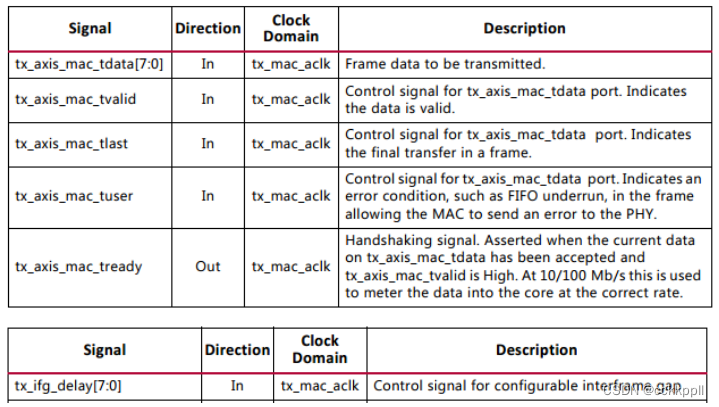

AXI-Stream 发送接口信号如下图所示。用户通过该接口,向 IP 核传输所需要发送的以太网数据

包。其中,tx_ifg_delay 用于设置发送间隔,一般都默认采用最小间隔,将 tx_ifg_delay 置为 0 即

可。

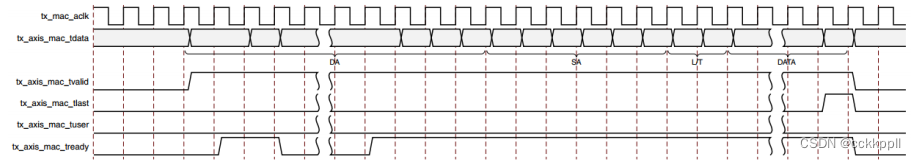

AXI-Stream 发送接口时序如下图所示。

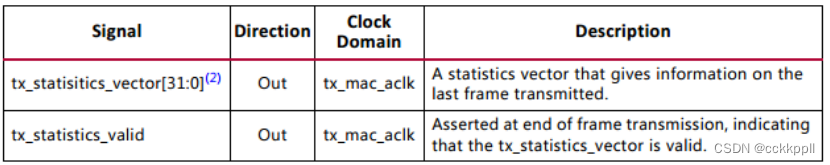

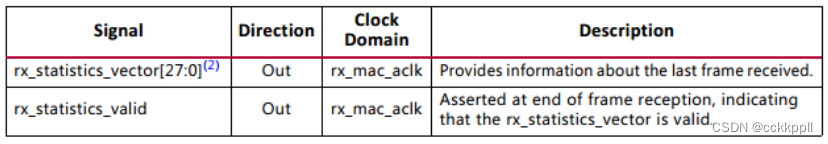

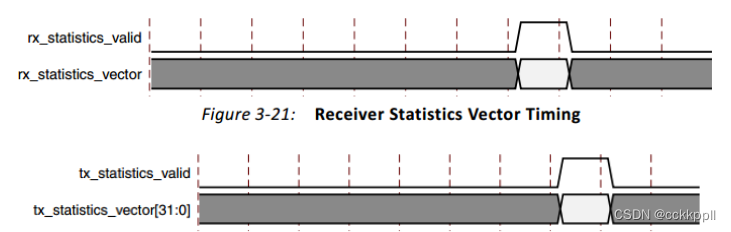

接收发送数据统计信号

下图中的信号,用于统计并输出当前发送完毕或者接收完毕的帧对应的各种类型的信息。除了调

试用之外,一般无需使用。

信号时序如下图所示。

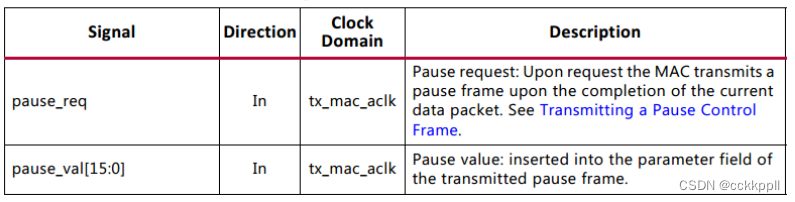

流量控制信号

非高带宽、大负荷传输情况下,一般不需要使用流量控制功能。因此,不需要发送暂停帧,将以

下两个信号均置为 0 即可。

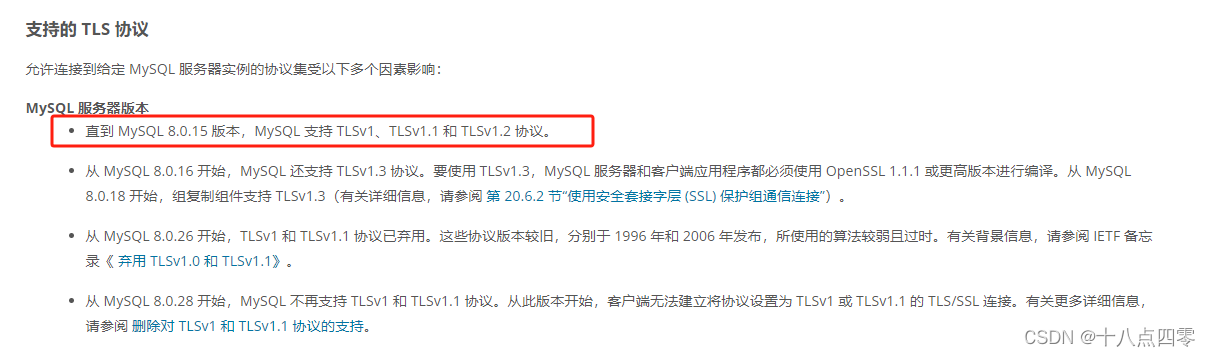

AXI-Lite 接口

AXI-Lite 接口主要用于配置和读取 IP 核内部的寄存器。除此之外,还可以直接通过 MDIO 接口

配置外部 PHY 芯片或者 1G/2.5G Ethernet PCS/PMA or SGMII IP 核的寄存器。由于 MDIO 没有使用。因此,AXI-Lite 接口主要用于 IP 核设置。

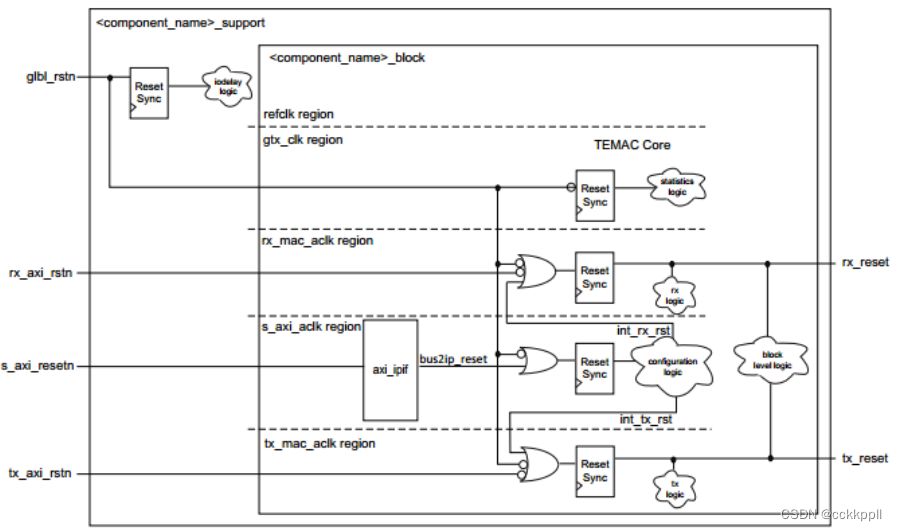

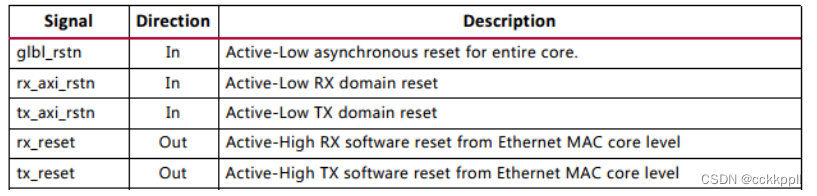

复位信号

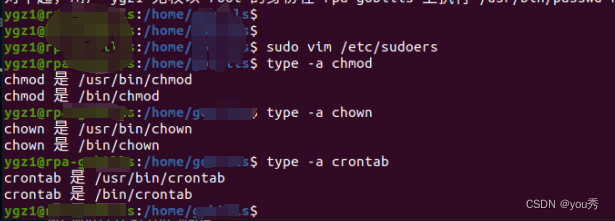

IP 核的复位信号网络如下图所示。

其中 glbl_rstn 为全局复位信号,用于复位整个 IP 核。rx_axi_rstn 和 tx_axi_rstn 分别用于

单独复位接收和发送部分的逻辑,一般无需使用。在例程中,将 rx_axi_rstn 和 tx_axi_rstn 都被恒

置为 1。 tx_reset 和 rx_reset 分别用于表示 IP 核的发送和接收部分逻辑的复位状态,根据这两个信号可以判断 IP 核是否处于复位状态。这两个信号需要配合 AXI-Stream 接收和发送接口的同步时钟信号 tx_mac_aclk 和 rx_mac_aclk 进行使用,这是因为可能当 tx_reset 和 rx_reset 由 1 变为 0 时,IP 核才会输出 tx_mac_aclk 和 rx_mac_aclk。对于使用 tx_mac_aclk 和 rx_mac_aclk 作为同步时钟的逻辑,复位信号必须以 tx_reset 和 rx_reset 作为基准,避免出现复位无效的情况。对此,在例程中给 出了参考设计。

G/2.5G Ethernet PCS/PMA or SGMII

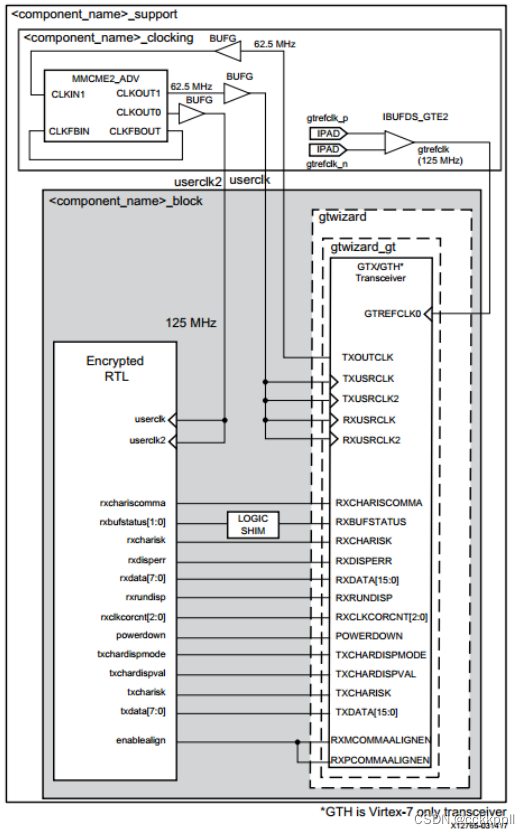

时钟网络

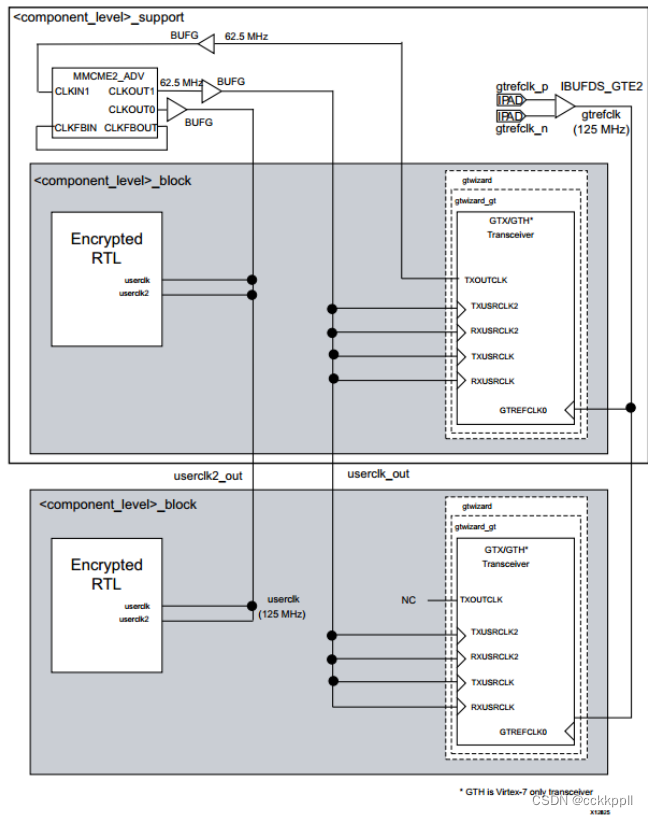

IP 核内部时钟网络结构如下图所示。

时钟网络

当需要使用多个 IP 时,且所使用的 GTP 位于同一个 GTP BANK 中时,不同 IP 核之间的时钟网络可以进行共享,如下图所示。多个 IP 核可共享同 1 个 GTP BANK 的参考时钟,以及同一个 MMCM 输出的时钟信号。

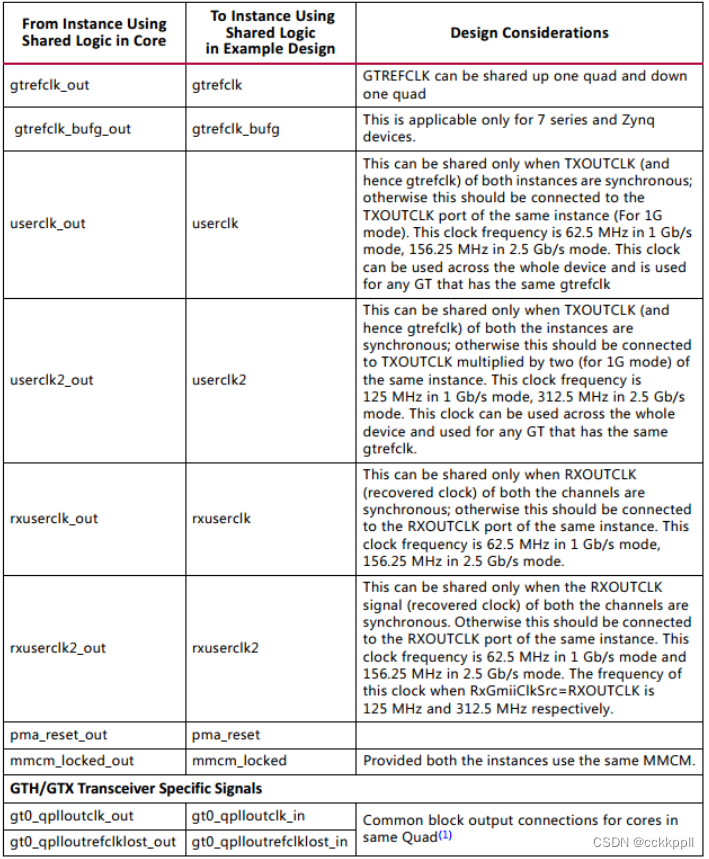

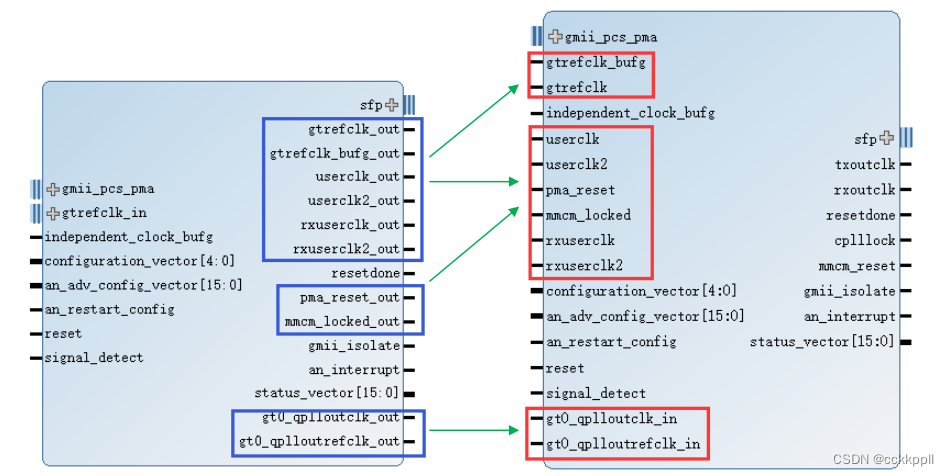

共享端口

多个 IP 核之间的共享信号连接方式如下图所示。

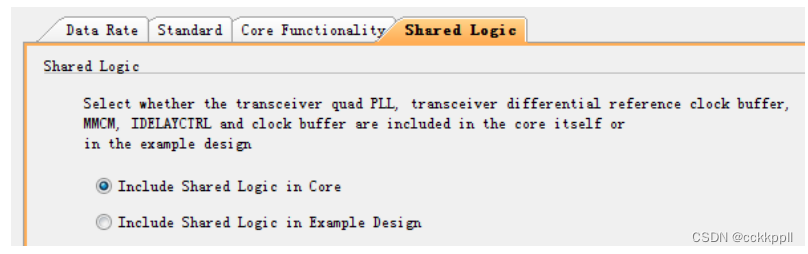

上图中,左侧的 IP 核选择了将共享资源包含在 IP 核内部,右侧的 IP 核则选择了将共享资源从

IP 核内部去除,移至 example desgin 中。在 udp_ip_1g_sfp_2ch 例程中,例化了 2 个 IP 核。其中, gig_ethernet_pcs_pma_i_1 对应上图左侧的 IP 核,pcs_pma_i_2 对应上图右侧的 IP 核。这取决于上面所提到的 1 个 IP 设置,其中 pcs_pma_ i_1 的设置如下图所示。

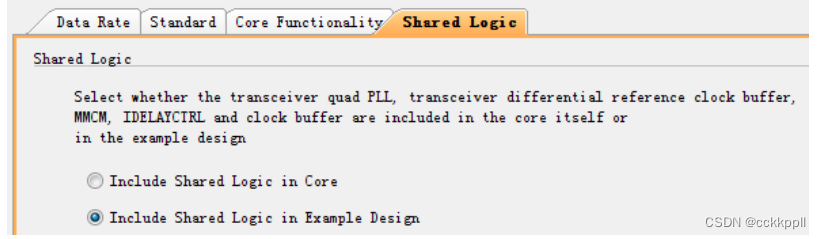

pcs_pma_ i_2 的设置如下图所示。

各共享信号定义与连接关系如下图所示。