本篇文章将介绍存内计算技术对于数据经济的提升,我们将从提出问题、解答问题与阐述应用三个方面进行展开介绍,并引入浮点存算、等新兴存算技术进行简要介绍。

一.数据经济&存内计算,结合是否可行?

数据经济与存内计算,结合是否可行?为了解答这个问题,首先我们来了解一些数据经济的基本概念。

(1)基本概念

数据经济是指以数据为核心资源,通过数据的收集、分析和应用,创造经济价值的一种经济形态。它强调数据在经济活动中的重要作用,将数据视为一种新的生产要素,与传统的土地、劳动力、资本和技术并列。数据经济不仅包括数据本身的生产和交易,还涵盖数据驱动的产品和服务的创新与市场推广。

(2)发展现状

数据经济在国内外均取得了显著发展,并受到了广泛关注。在中国,数据经济的规模和基础设施建设快速推进,互联网和移动互联网用户数量居世界前列,形成了庞大的数据资源库。云计算和大数据基础设施的不断完善,使得各行业加速数字化转型。制造业中,智能制造和工业互联网蓬勃发展;零售业中,电子商务和新零售模式不断创新;金融业中,金融科技应用广泛。技术创新方面,人工智能、大数据分析和区块链技术在国内发展迅速,涌现出一批具有国际竞争力的企业,如阿里巴巴、腾讯和百度等。为推动数据经济的发展,中国政府出台了一系列政策和法规,包括《数据安全法》《网络安全法》以及国家大数据战略,强调数据资源的整合、开放共享和安全保护。

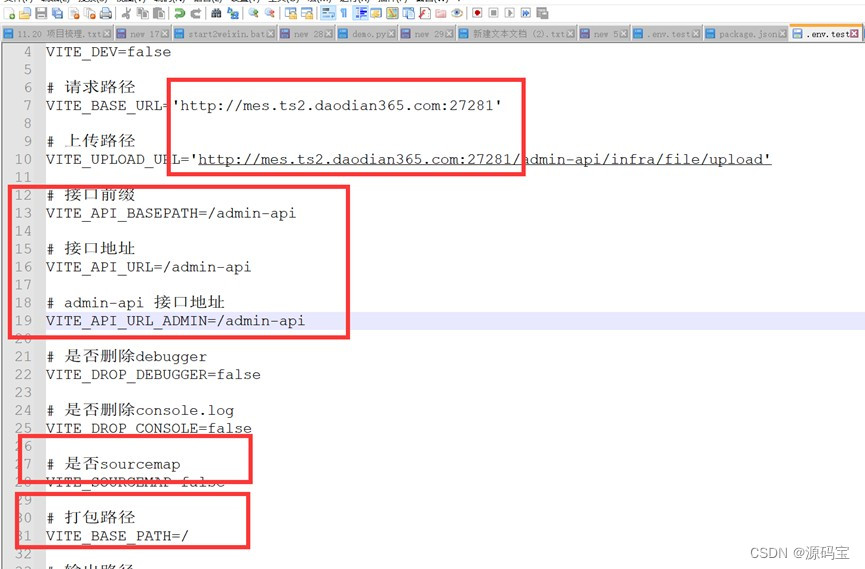

图1 国家《数据安全法》[1]

在国际上,美国、欧盟和日本等发达国家在数据经济领域也处于领先地位。美国拥有全球领先的互联网公司和云计算服务提供商,如谷歌、亚马逊和微软,推动了数据经济的快速发展。欧洲在数据隐私保护和法规方面走在前列,制定了《通用数据保护条例》,对全球数据经济的发展产生了重要影响。各国在智能制造、智慧城市、电子商务和金融科技等领域大力推进数据经济的应用,并通过数据分析和人工智能技术实现医疗健康领域的个性化医疗和公共卫生监测。美国政府推出了一系列支持数据经济发展的政策,如《联邦大数据研究和发展计划》,鼓励大数据技术的研究和应用;欧盟通过《欧洲数据战略》推动建立单一数据市场,促进数据的自由流动和利用。总体来看,各国政府通过政策支持和法规保障,推动数据经济的规范化和可持续发展。

(3)应用实例

1.智慧城市

数据经济在智慧城市建设中起到了关键作用。通过数据的收集和分析,城市管理者可以更好地规划和管理城市资源,提高交通、能源、水资源等方面的效率,提升市民的生活质量。

2.金融科技

在金融行业,数据经济通过大数据分析和人工智能技术,实现了风险控制、市场预测和个性化金融服务。数据驱动的金融科技公司,如蚂蚁金服和Stripe,正在改变传统金融行业的运营模式。

图2 Stripe网站平台[2]

3.零售电商

在零售和电商领域,数据经济通过消费者行为分析和大数据推荐系统,实现了精准营销和个性化推荐。亚马逊、阿里巴巴等电商平台利用数据分析技术,极大地提升了用户体验和销售额。

(4)未来展望

随着大数据和数据经济的不断发展,海量数据的收集、存储、分析都需要大量的人力物力,其对芯片算力的需求不断增长,而传统冯﹒诺依曼架构已无法支持当今大数据算力需求,因此新型存内计算架构作为一种解决方案被提出。该架构将存储与计算相结合,可以极大地提升芯片算力。接下来,我们将具体介绍存内计算对数据经济的提升,赋能数据经济,存内计算技术将大有可为

二.存算赋能数据经济,浮点存算大有可为

作为数据经济关键一步的数据的分析与处理往往依赖传统的服务器群。服务器群虽然通过“量变”汲取到了可观的算力,但随之而来的高功耗和散热问题难以忽视[3]。

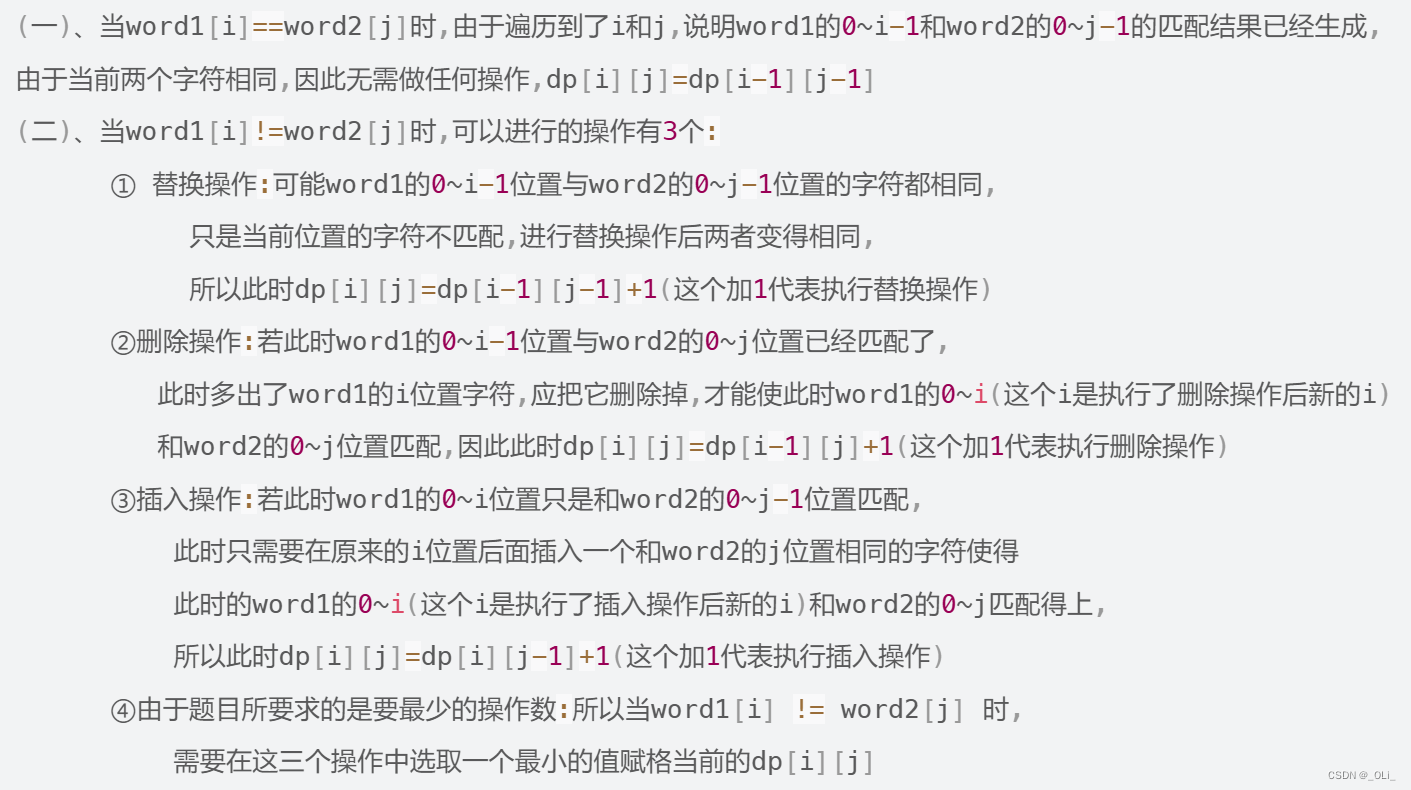

其中一个原因是因为服务器采用的传统冯·诺伊曼架构芯片,因为存储和计算分离,在计算过程中会消耗大量功耗于访存过程中。表1展示了在商用65nm工艺制程芯片的测试环境下,以实现一次乘累加计算的功耗为基准,访问各类存储器的功耗[4]。

表1 冯·诺伊曼芯片架构面临的“存储墙”和“功耗墙”挑战

| 功耗类型 | 访问片外DRAM存储器 | 访问全局缓存(>100 KB) | 处理单元间传数(1 ~ 2 mm) | 访问局部寄存器(2.5 KB) |

| 相对功耗 | 200倍 | 100倍 | 2倍 | 1倍 |

如上表所示,处理单元为了获取计算所需的数据,需要逐级向片上缓存、DRAM、存储器获取数据,访问的存储器越“远”,所需付出的访存功耗越大,这违背了处理器主要用于处理数据的初衷。

存内计算,将存储器和计算单元集成在一起,旨在使芯片计算单元兼具存储数据、处理数据的能力,计算单元可以通过极低的开销获取数据,理论上拥有无限的数据带宽,具有高计算能效、高带宽、低计算延时的特点,能够与数据经济的需求形成耦合。

当前最先进的浮点存算工作已经证明了其在能效上的优越性,[5]在BF16的输入和权重精度、FP32输出精度下实现了91.2Tops/W的峰值能效和最高45.4的平均能效,能够高能效地执行神经网络计算。不过,受限于高校的研究经费和存内计算企业的规模,当前的存内计算芯片更注重能效而非峰值算力。

即便如此情况下,存算芯片仍在数据经济中大有可为。当前存算芯片的能效和规模更适合部署在端侧设备中,可以辅助完成数据采集的工作。传统数据经济中,数据需要集中上传至服务器中处理,传输原始数据的过程中,数据隐私难以保证,数据量对网络的要求更高。利用存算芯片,完成网络前几层处理,上传前处理后的特征图至云端完成核心部分的处理再将结果回传本地,这种云端协同的处理方式既保证了数据安全又降低了网络带宽。利用本地设备前处理,还可以更好地结合多模态数据,例如[6]实现了将事件相机和RGB相机的数据结合到一起。

除了浮点存内计算以外,存内计算还可以从多方面提高计算效率,比如有以下几个方面:

(1)新型存储器的应用:基于新型存储器的非易失存内计算技术,如MRAM、Flash等。MRAM存内计算芯片是一种基于隧穿磁阻效应的非易失性存储技术,具有高读写速度、强微缩能力、低功耗、抗辐射等优势,可凭借高速高容量、低功耗低成本等特点大幅提升计算效率。Flash存内计算芯片已在小算力低功耗端侧场景实现规模化应用,并正在向中算力演进,逐步提升其计算效率;

(2)3D集成电路的应用:3D集成电路是一种高级芯片设计方法,可通过垂直堆叠和连接多个处理层来增加集成度并提高计算效率。通过将3D集成电路与存算一体技术相结合,可以进一步缩短互联线长度,改善互联结构,减少信号传播延迟并降低功耗;同时,在单位空间内容纳更多的处理层,也能显著提高芯片的计算效率。但目前,该技术还面临一些如芯片对准、互联可靠性和热管理等方面的技术挑战;

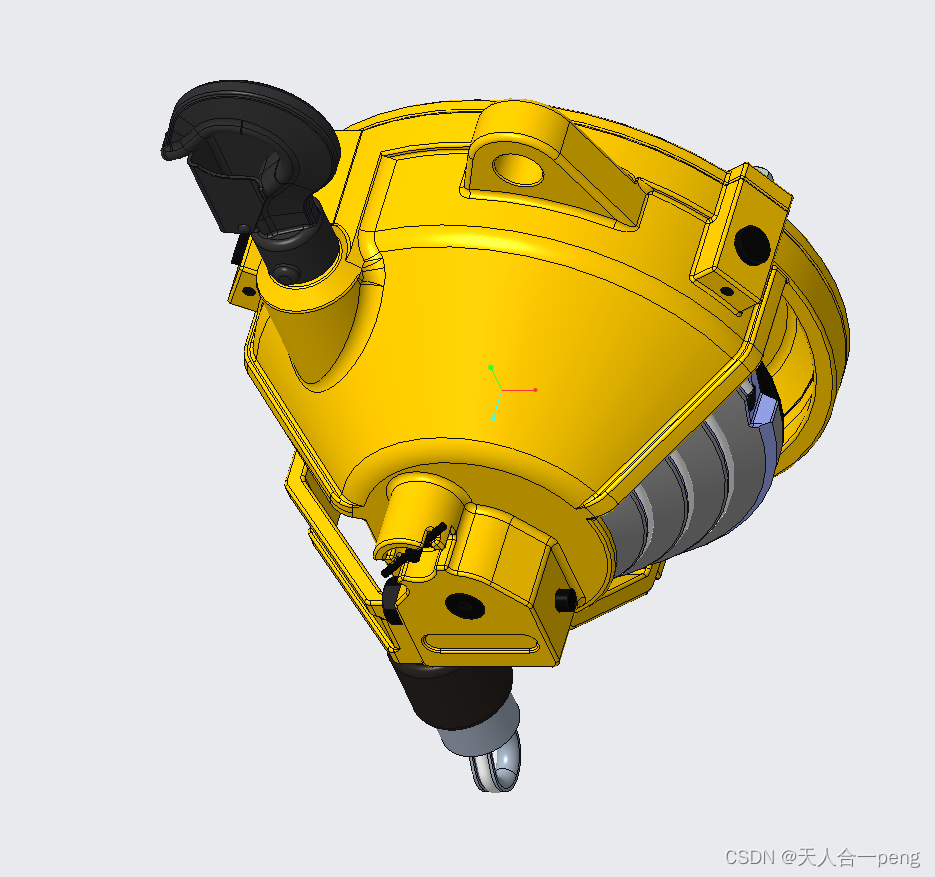

图3 采用硅通孔技术(TSV)的3D集成电路

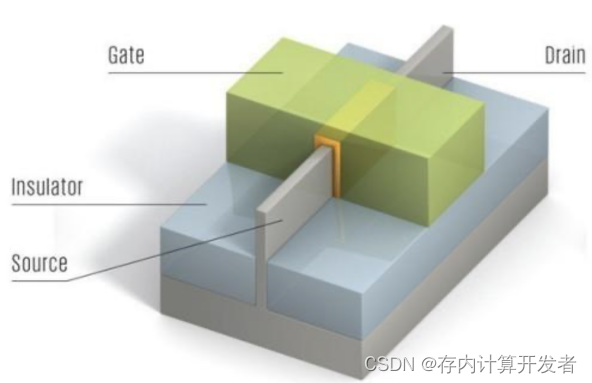

(3)新型工艺与材料的应用:新型工艺不仅体现在工艺节点的进步,还包括FinFET、GAAFET等新型晶体管工艺,相比于传统的平面晶体管,FinFET、GAAFET等三维晶体管可以提供更好的电性能与更低的功耗;除此之外,还包括高介电常数(High-k)材料、二维材料等新型材料,他们均可以从多个方面的优势提升芯片的计算效率。

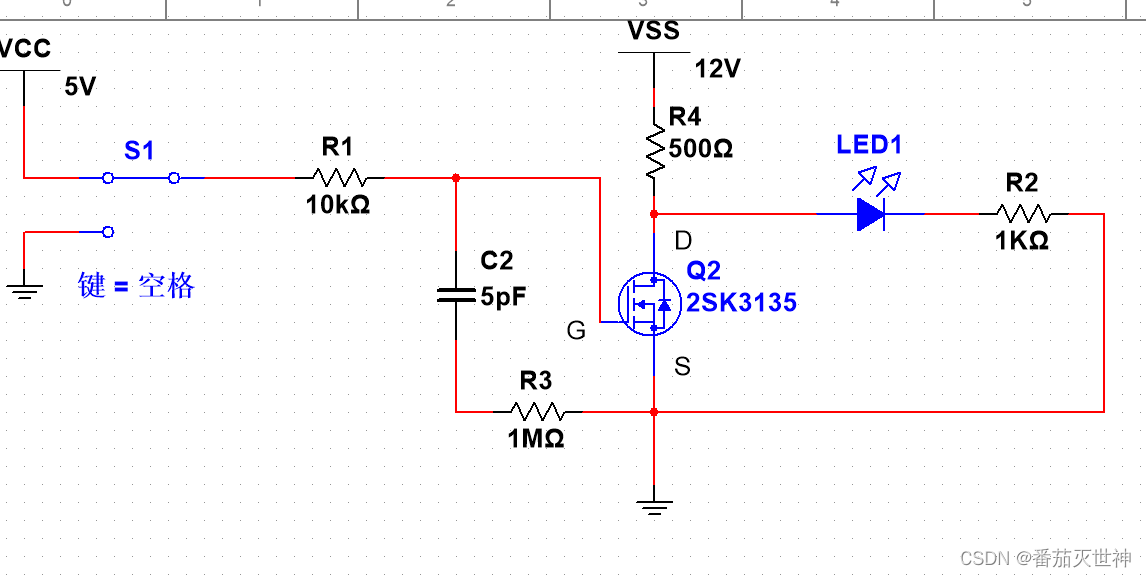

图4 FinFET示意图

三.存算结合数据经济,推动产业转型升级

在数据经济中,存内计算已通过其独特的优势显著推动数字化转型与产业升级。例如:

(1)知存科技:其研发的全球首颗量产商用存内计算SoC芯片WTM2101,已在高能效AI应用场景中显示出巨大潜力。该芯片利用存储与计算的物理融合,大幅减少数据搬运,从而大幅提升计算效率。此外,WTM8系列芯片面向6-48Tops算力产品,应用于4K-8K视频的实时处理。未来,公司将继续专注存内计算芯片领域,引领存内计算产业化。

图5 知存科技WTM2101芯片

(2)九天睿芯:该公司基于类脑计算,以模数混和形式,实现感存算一体芯片的研发落地和量产销售,该公司目前已完成亿元级A轮融资。 九天睿芯已经推出包括ADA100和ADA200在内的多款芯片。ADA200是低功耗中低算力视觉协处理器,算力1-2Tops,应用于低功耗无线摄像头/ARVR/手机平板,将于2022年底量产,ADA200是基于最新感存算一体技术架构实现的模数混合AI视觉芯片,相比传统数字芯片,具备更低功耗,以及超高的能效比。

(3)千芯科技:该公司的核心产品包括高算力低功耗的存算一体AI芯片/IP核,基于SRAM/RRAM/MARM存储单元,目前已通过互联网大厂原型内测。千芯科技主要推进面向云端推理和边缘计算的AI芯片研发,产品可应用于云计算、自动驾驶、智能安防等领域,在云计算方面,技术团队正在优化产品原型,将AI芯片技术与工业客户的需求相结合,目前产品已完成样机验证,产品算力达到1000TOPS以上。

由此可见,存内计算在数据经济领域将大有可为。存内计算凭借其高算力、低功耗等优势,十分契合于数据经济时代的大数据收集、处理等计算过程,浮点存算、新型存储器存算等技术,将进一步赋能数据经济,推动产业转型与升级。

参考资料

[1]中华人民共和国数据安全法_中国人大网 (npc.gov.cn).

[2] Stripe | 互联网金融基础设施.

[3] Li, Pengfei, et al. "Making ai less" thirsty": Uncovering and addressing the secret water footprint of ai models." arxiv preprint arxiv:2304.03271 (2023).

[4] Chen Y H, Krishna T, Emer J S, et al. Eyeriss: An energy-efficient reconfigurable accelerator for deep convolutional neural networks[J]. IEEE journal of solid-state circuits, 2016, 52(1): 127-138.

[5] Khwa W S, Wu P C, Wu J J, et al. 34.2 A 16nm 96Kb Integer/Floating-Point Dual-Mode-Gain-Cell-Computing-in-Memory Macro Achieving 73.3-163.3 TOPS/W and 33.2-91.2 TFLOPS/W for AI-Edge Devices[C]//2024 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2024, 67: 568-570.

[6] Ichikawa Y, Yamada A, Misawa N, et al. REM-CiM: Attentional RGB-Event Fusion Multi-modal Analog CiM for Area/Energy-efficient Edge Object Detection during both Day and Night[J]. IEICE Transactions on Electronics, 2024: 2023CTP0001.