一. HLS是什么?与VHDL/Verilog编程技术有什么关系?

高层次综合 (HLS)

- 抽象级别更高:HLS允许设计者在更高的抽象级别上工作,使用高级编程语言来描述硬件的功能。这种方法减少了设计者需要处理的底层细节,使得设计过程更加高效。

- 自动生成HDL代码:HLS工具可以将高级语言编写的算法自动转换为HDL代码,从而生成可综合的硬件描述。这种自动化过程可以减少手工编码的错误,并加快设计周期。

- 设计优化:HLS工具通常具有许多优化选项,可以自动进行循环展开、流水线化等优化,以生成更高效的硬件实现。

- 加快设计验证:由于使用高级语言进行设计,设计者可以利用软件调试工具进行早期验证,从而加快整个设计验证过程。

VHDL/Verilog编程技术

- 低级硬件描述:VHDL和Verilog是传统的硬件描述语言,设计者需要在较低的抽象级别上编写代码,详细描述硬件的行为和结构。这需要设计者具备深厚的硬件知识。

- 手工编码:使用VHDL或Verilog进行设计时,所有的代码都是手工编写的。这种方法尽管灵活,但也容易出现人为错误,并且开发周期较长。

- 详细控制:设计者可以完全控制硬件的每一个细节,因此在需要精确控制和优化硬件时,VHDL和Verilog是不可替代的。

- 广泛应用:尽管HLS越来越受欢迎,但VHDL和Verilog仍然是硬件设计中的主流语言,尤其在FPGA和ASIC设计中。

关系和区别

- 抽象级别:HLS使用高级语言进行设计,抽象级别较高;而VHDL和Verilog是低级的硬件描述语言,需要详细描述每个硬件组件。

- 设计流程:HLS的设计流程包括高级语言编写、自动综合、优化和验证;而VHDL/Verilog的设计流程主要是手工编写和验证。

- 应用场景:HLS适用于快速原型设计和算法验证,尤其在设计周期较短的项目中表现出色;而VHDL和Verilog适用于需要详细控制和优化的复杂硬件设计。

总的来说,HLS与传统的VHDL/Verilog编程技术是互补的。HLS提高了设计效率,减少了设计复杂度,而VHDL和Verilog则提供了更高的控制和优化能力。在现代硬件设计流程中,设计者往往会结合使用这两种技术,以充分发挥各自的优势。

二. HLS有哪些关键技术问题?目前存在什么技术局限性?

高层次综合 (HLS) 虽然提供了显著的设计效率提升和抽象级别的提高,但在实际应用中仍然面临一些关键技术问题和局限性:

关键技术问题

-

精确的硬件映射:如何将高级语言中的抽象描述精确地映射到硬件结构上是HLS的核心挑战之一。高级语言的抽象程度较高,而硬件设计需要精确的细节控制,这两者之间的映射是一个复杂的过程。

-

性能优化:尽管HLS工具可以进行自动化的性能优化,但如何高效地利用硬件资源(如寄存器、逻辑单元、内存等)仍是一个挑战。自动化优化可能无法达到手工优化的精细程度。

-

并行性和流水线化:高级语言中的并行性和流水线化在硬件中实现时,需要处理数据相关性、控制依赖性等问题。HLS工具需要智能地分析和处理这些依赖关系,以生成高效的并行和流水线化硬件。

-

代码风格和结构:高级语言代码的风格和结构对生成的硬件有很大影响。设计者需要熟悉如何编写适合HLS工具处理的代码,以便生成高效的硬件。

-

调试和验证:从高级语言到硬件描述语言的转换过程中,调试和验证是一个复杂的问题。如何在高级语言级别进行有效的调试,并在硬件级别验证功能正确性,是HLS面临的重要问题。

技术局限性

-

性能与手工设计的差距:HLS生成的硬件在性能上可能与手工优化的设计存在一定差距。手工设计可以进行更细粒度的优化,而HLS工具的自动化优化难以达到相同的精度。

-

对复杂控制逻辑的支持不足:HLS在处理复杂的控制逻辑时可能表现出局限性。这是因为高级语言通常更适合描述算法,而硬件设计需要详细的状态机和控制逻辑。

-

工具的成熟度和兼容性:目前市场上的HLS工具在成熟度和兼容性上存在差异。不同工具对高级语言的支持程度不同,生成的硬件描述语言代码质量也有所不同。这可能导致在不同工具之间进行移植时遇到问题。

-

学习曲线:尽管HLS提高了抽象级别,但设计者仍然需要学习如何有效使用HLS工具,以及如何编写适合硬件实现的高级语言代码。这对传统的软件工程师和硬件设计师都是一个新的挑战。

-

资源开销:HLS工具和方法可能引入额外的资源开销,如增加硬件面积、功耗等。虽然HLS可以显著提高设计效率,但在资源受限的应用中,这些开销需要仔细权衡。

未来发展方向

尽管存在这些问题和局限性,HLS技术仍在不断发展。未来的研究和改进可能包括:

- 提高工具智能化:利用人工智能和机器学习技术,提高HLS工具的智能化水平,自动识别和优化复杂的硬件结构。

- 改进调试和验证工具:开发更强大的调试和验证工具,支持从高级语言级别到硬件级别的全流程验证。

- 优化算法:研究和开发更高效的算法,用于自动优化生成的硬件描述,缩小与手工优化的性能差距。

- 标准化和互操作性:推动HLS工具的标准化,增强不同工具之间的兼容性和互操作性,使得设计者可以更灵活地选择和切换工具。

总体来说,HLS作为一种前沿的设计技术,正在不断进步,并有望在未来的硬件设计中发挥越来越重要的作用。

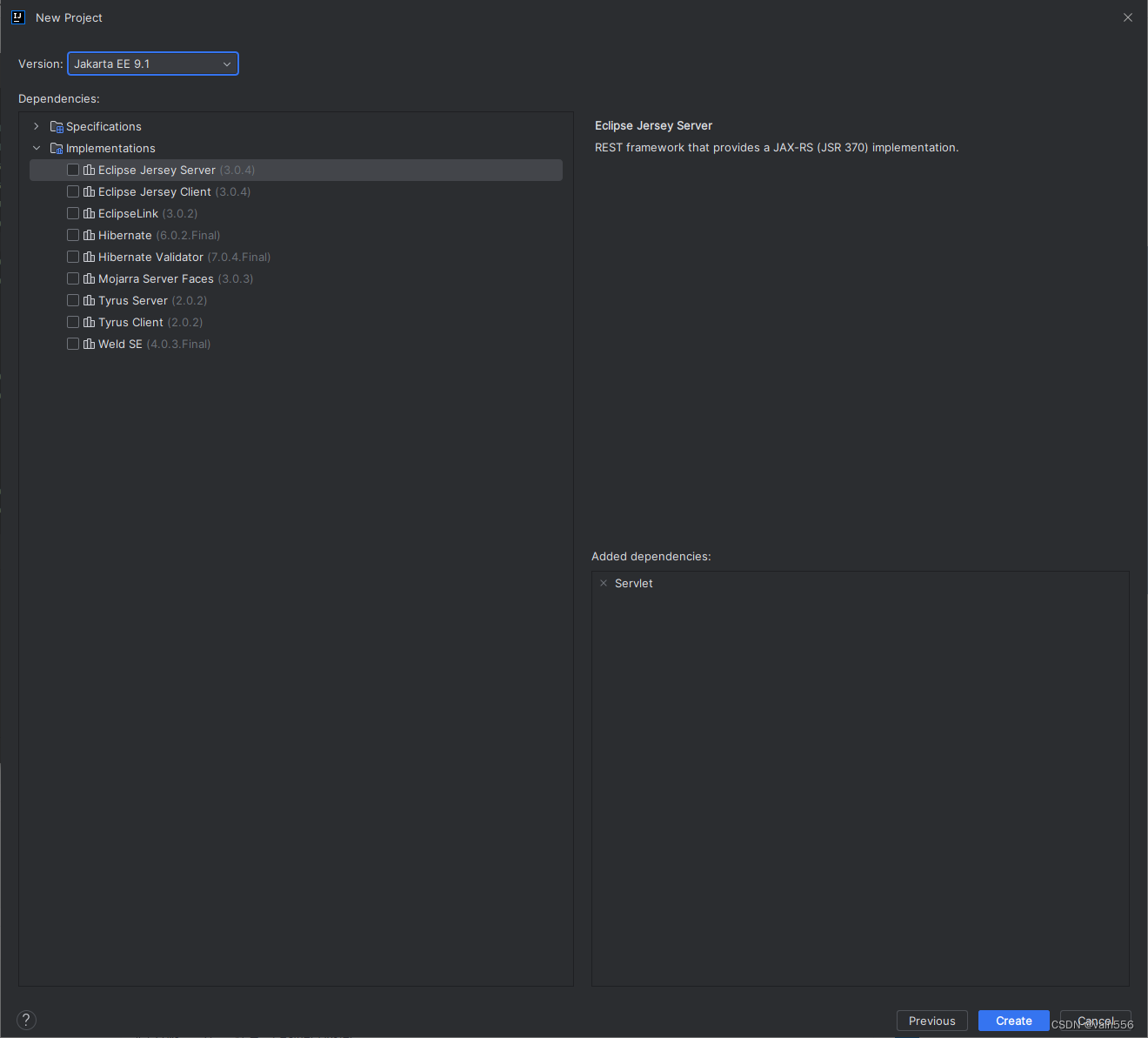

三. 在win10(或者Ubuntu系统下)安装 Intel 或者 Xilinx 的支持HLS的FPGA编程开发软件(Quartus18或者Vivado18),设置好环境,完成一个入门级的HLS程序,并进行仿真或者实际开发板运行。

创建项目

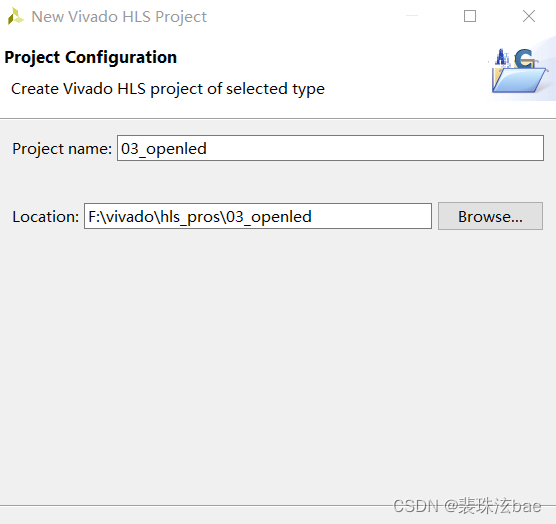

1、点击Vivado HLS 中的Create New Project

2、设置项目名

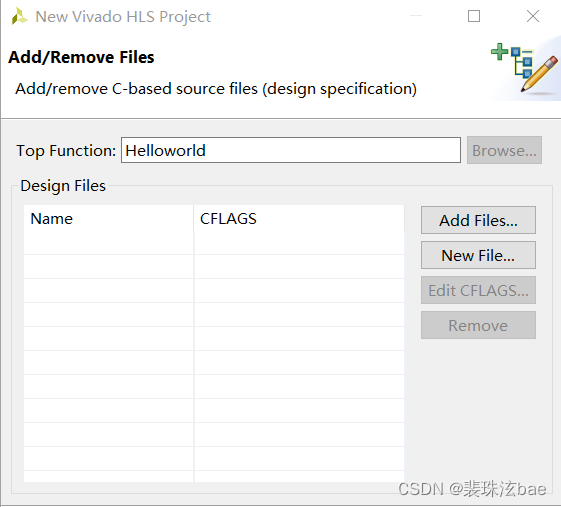

3、加入文件

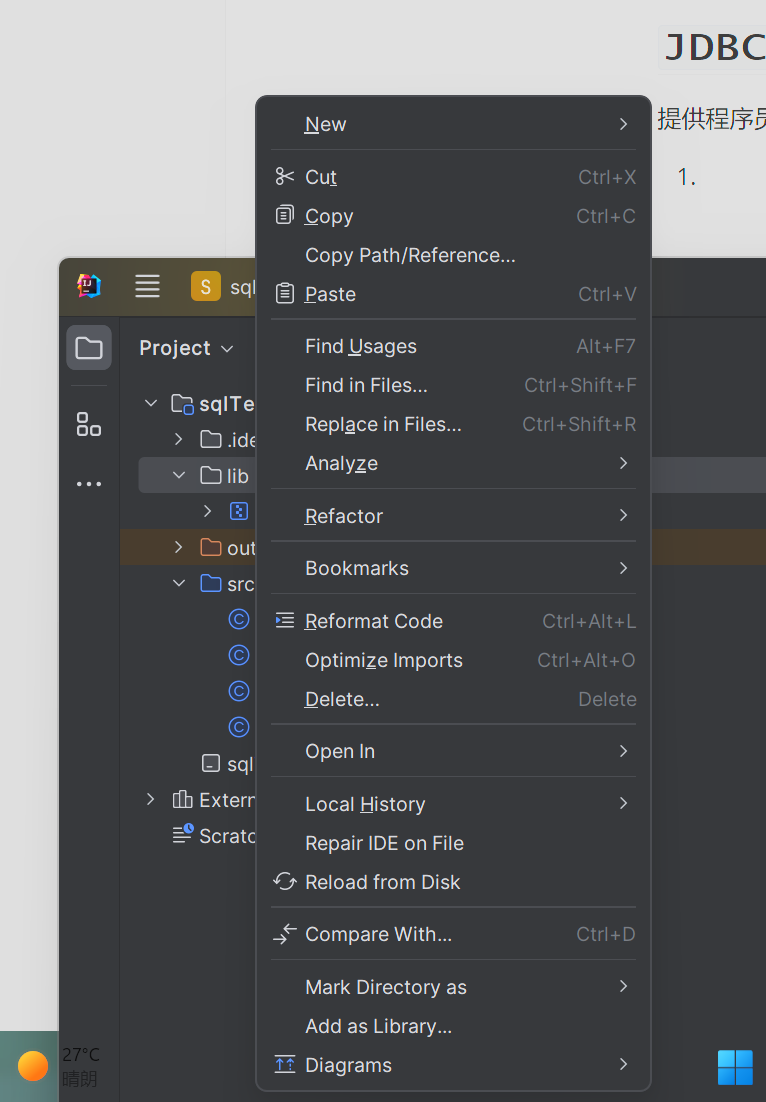

右键Source与Test Bench,分别新建文件Helloworld.cpp,Helloworld.h与tb_Helloworld.h。

C仿真

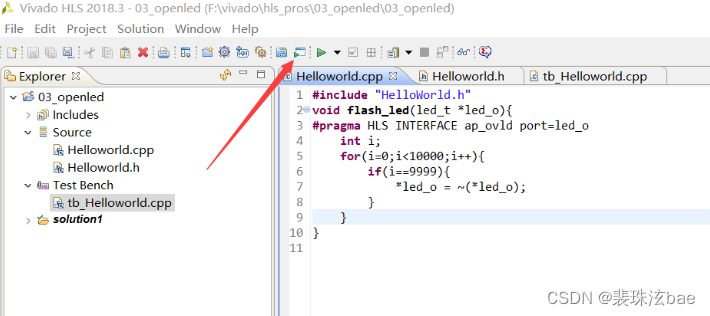

1、编写代码

在三个文件中分别编写以下代码:

Helloworld.h

//helloworld.h

#ifndef _HELLOWORLD_H_

#define _HELLOWORLD_H_

#include "ap_int.h"

typedef ap_int<1> led_t;

void flash_led(led_t *led_o);

#endif

Helloworld.cpp

//Helloworld.cpp

#include "HelloWorld.h"

void flash_led(led_t *led_o){

#pragma HLS INTERFACE ap_ovld port=led_o

int i;

for(i=0;i<10000;i++){

if(i==9999){

*led_o = ~(*led_o);

}

}

}

tb_Helloworld.cpp

#include "HelloWorld.h"

#include <stdio.h>

int main(){

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o);

printf("result : %d \n",(int)(led_o&0x01));

}

}

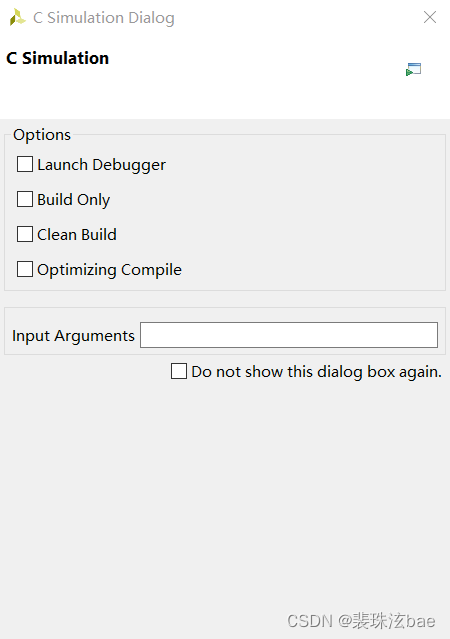

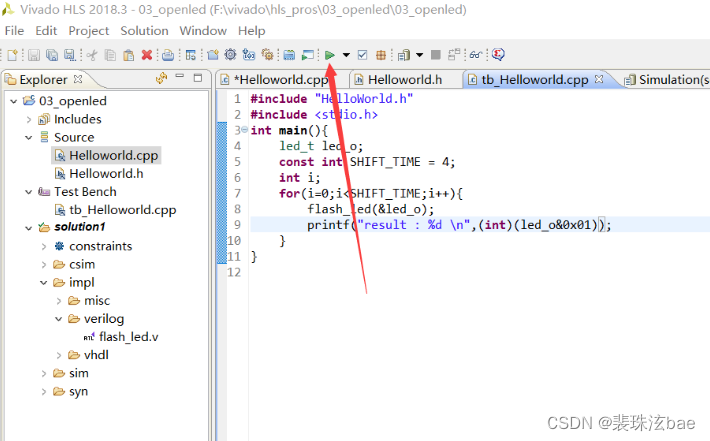

2、仿真

在保存好代码之后,点击图中的这个按钮进行C仿真:

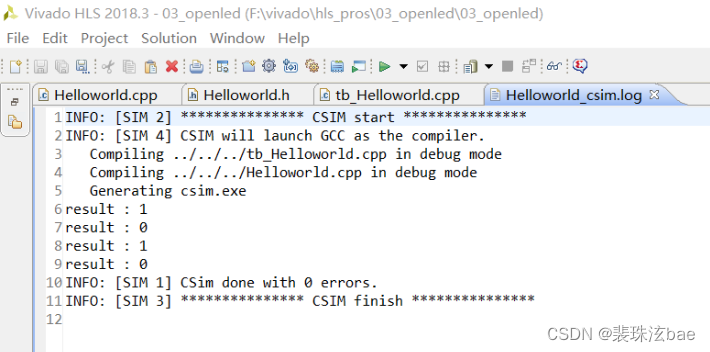

运行仿真后,出现下面这个界面就说明仿真成功了:

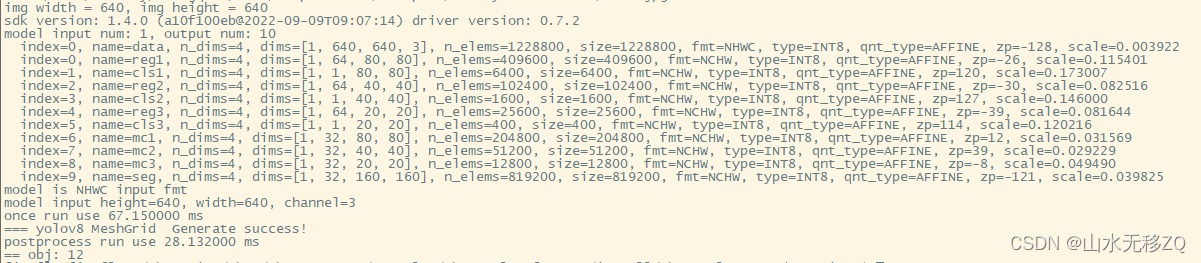

3、综合

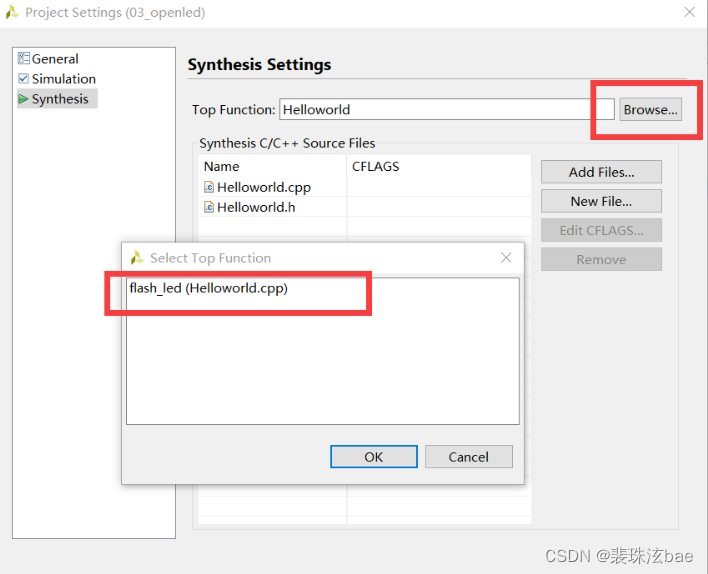

进行综合之前,先选择Top Function。

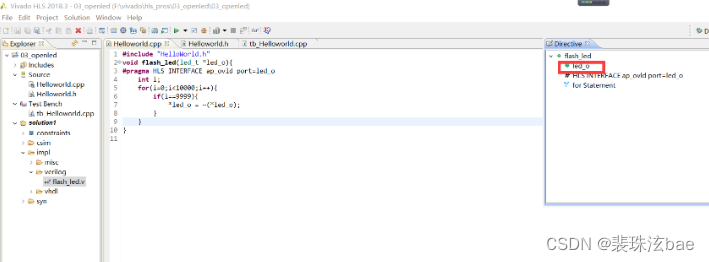

点击Project -> Project Setting -> Synthesis ,点击Helloworld.cpp,并点击Browse选择函数flash_led。

然后点击C运行:

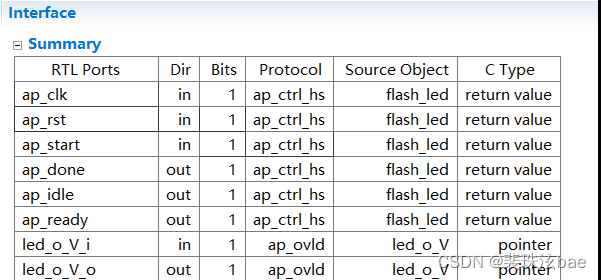

C 综合结束后,会有一个总结文件在这个文件的最后,有关于端口的表格:

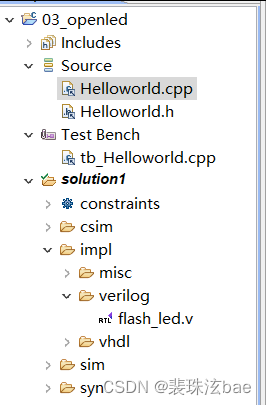

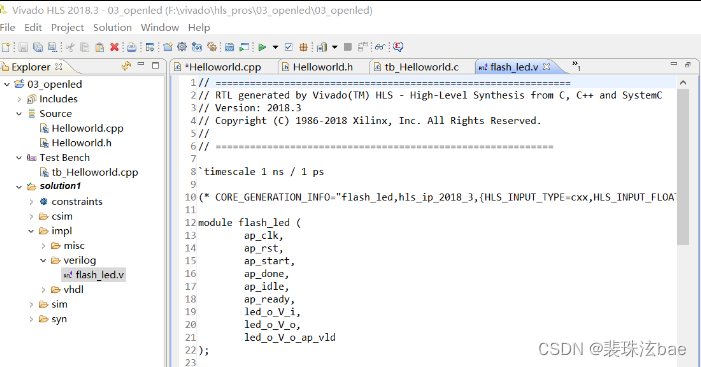

solution1\impl\verilog中,有已经生成好的.v文件:

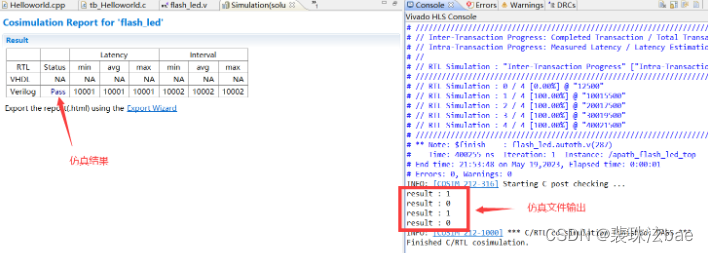

4、联合仿真

仿真结束后,出现下面界面,说明联合仿真成功: