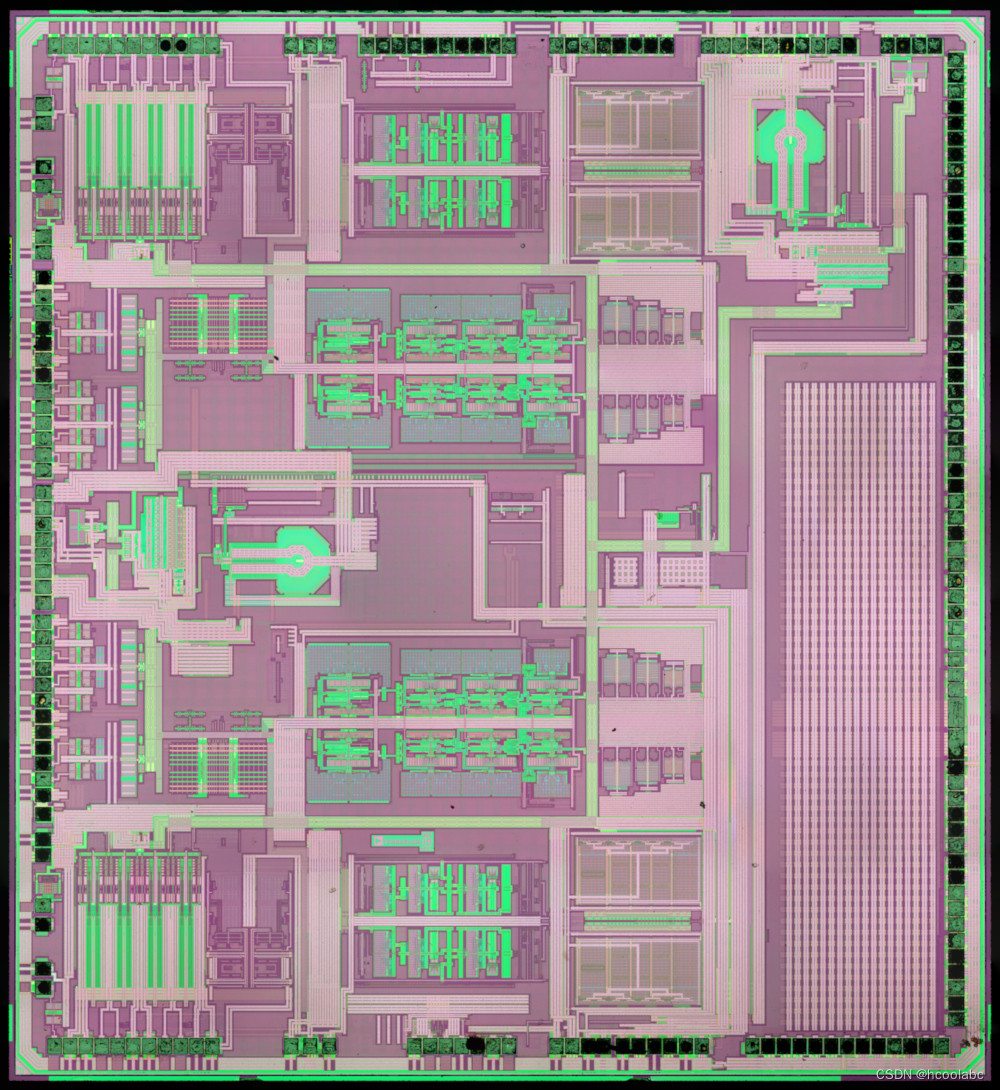

DIE : 4336x4730 um 的 65 nm 芯片

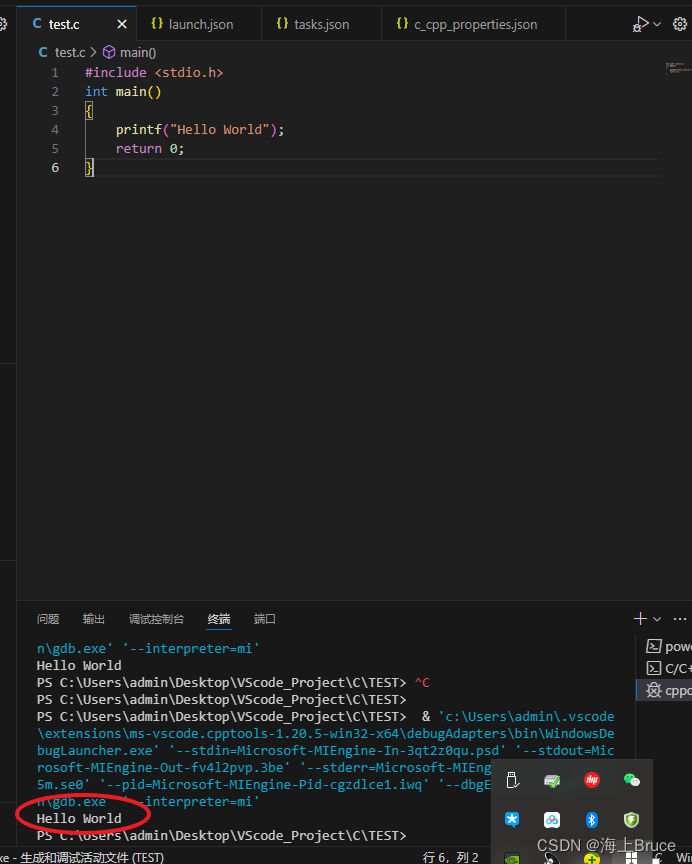

在顶部金属上,您可以看到 PLL 的电感器和日期代码 - 芯片在推出前两年就已准备就绪:

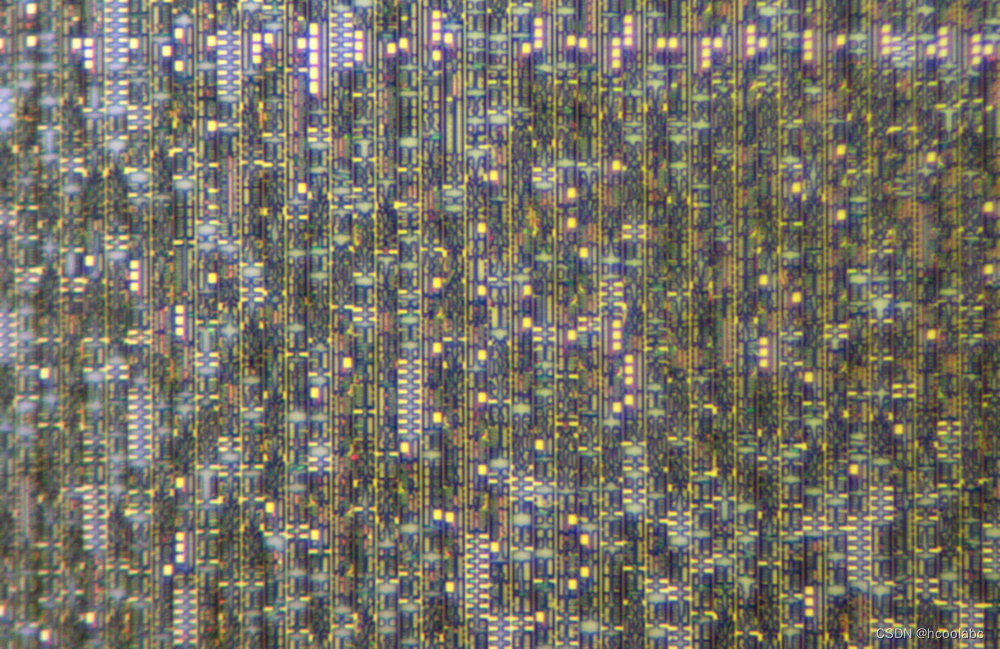

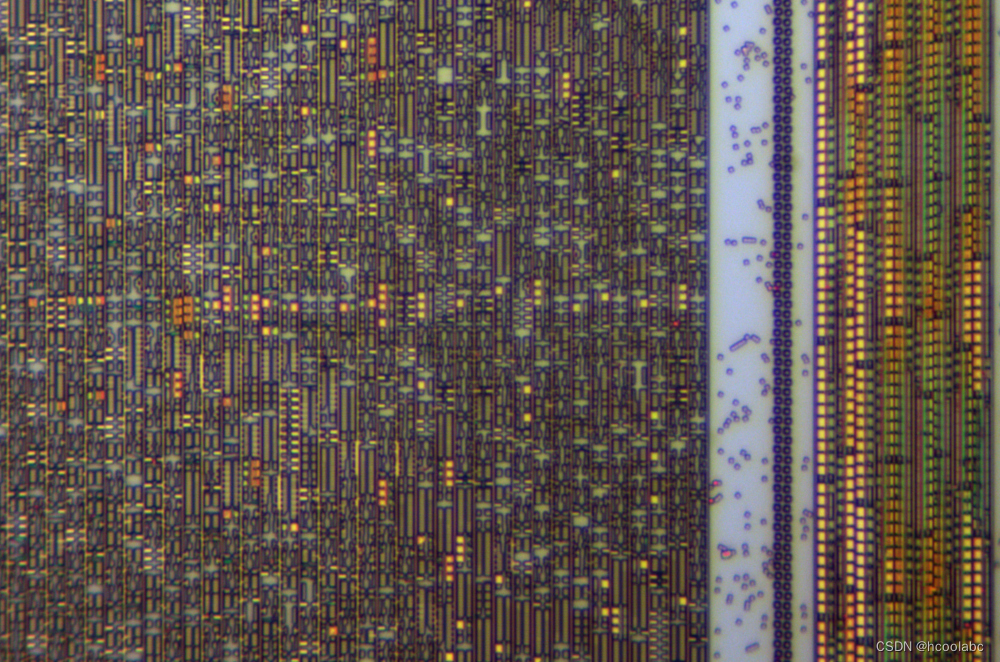

右下角是主数字块,应该是 128 抽头 FIR 滤波器。在最大放大倍率下,我们可以看到一排排标准单元。它们的放置方式与往常一样–背靠背 [PFET NFET] [NFET PFET],因此重复使用 VCC и GND 的垂直线(电源肯定是从整个顶部金属馈入的)。可以看出 PFET 晶体管更宽。标准单元宽度为 1.83 微米,与 65 纳米制造工艺一致。在全分辨率范围内,每个像素为 24.5 纳米。

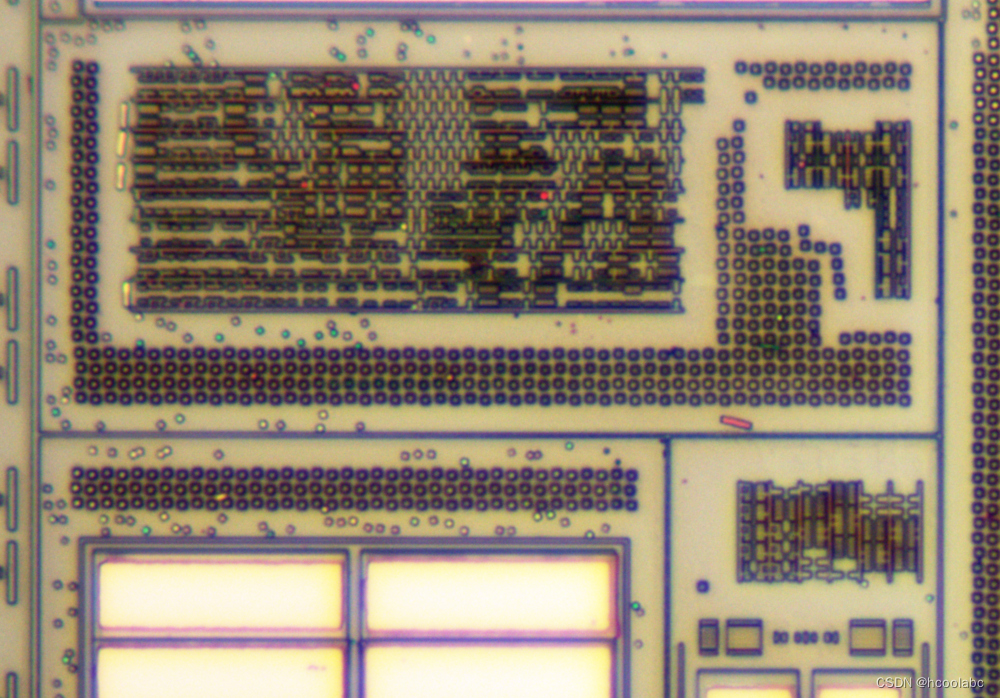

最后是部分蚀刻的 PLL 电感基座。PLL 相位噪声是数字无线电性能的极限,因此这是最关键的部件之一: