感觉教材和网络上对于计算机系统的结构描述都比较模糊,我自己对其进行了总结,并且画出图,不过因为学习的还是不够深入和全面,有的地方肯定是有问题的,烦请大家批评指正,我会进行修改~

文章目录

- 零、结构图总览

- 一、中央处理器(CPU)

- (一)运算器

- (二)控制器

- 二、存储器(Memory)

- (一)内存(主存)(MM)

- (二)高速缓冲存储器(Cache)

- (二)外存(辅存)

- 三、输入输出设备(I/O设备)

- 四、总线

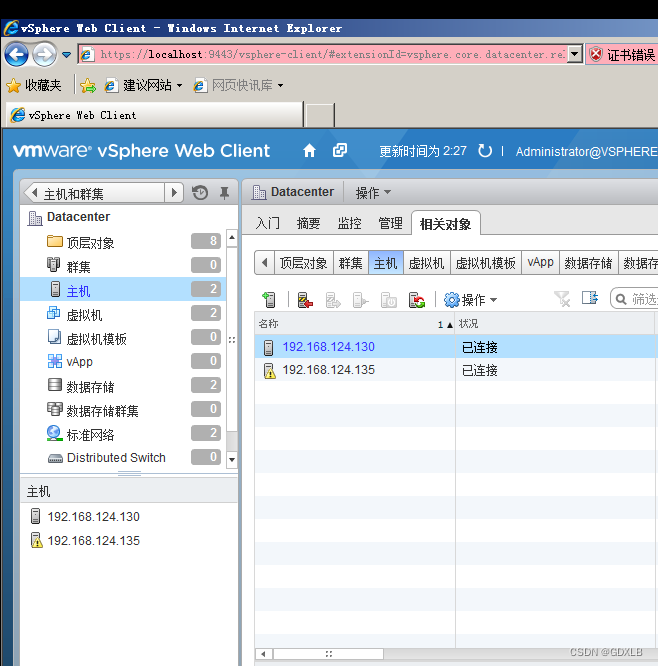

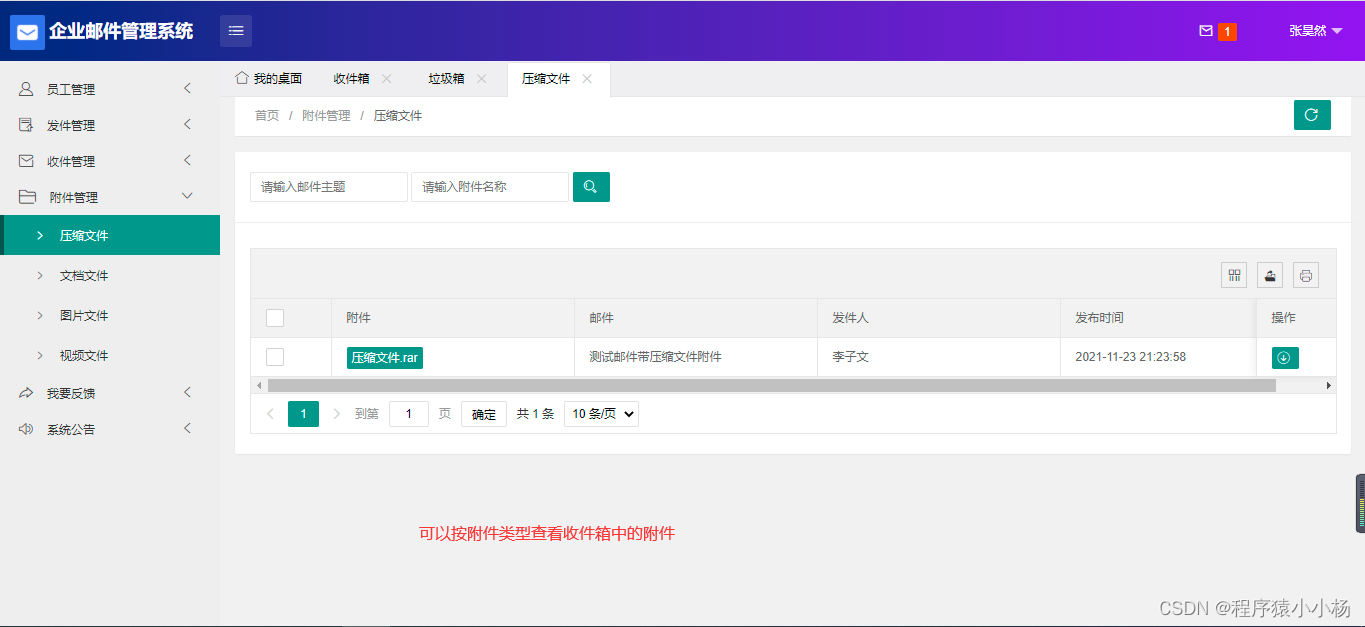

零、结构图总览

一、中央处理器(CPU)

(一)运算器

作用:运算器接收从控制器送来的命令并执行相应的动作,对数据进行加工和处理,执行算数运算和逻辑运算;。

1.算术逻辑单元(ALU):进行算术、逻辑运算 ;

2.通用寄存器(GPRs):用于存放操作数 (包括源操作数、目的操作数及中间结果)和各种地址信息等;

(1)累加寄存器 (ACC):是一个通用寄存器,用于暂时存放 ALU 运算的结果信息,可以作为加法运算的一个输入端;

(2)乘商寄存器(MQ):加法减法不使用,存乘数及乘积低位、商;

(3)操作数寄存器(X):存加数、减数、被乘数、除数;

(4)变址寄存器(IX):存储应用程序的长度;

(5)基址寄存器 (BR):存储数据内存的起始位置;

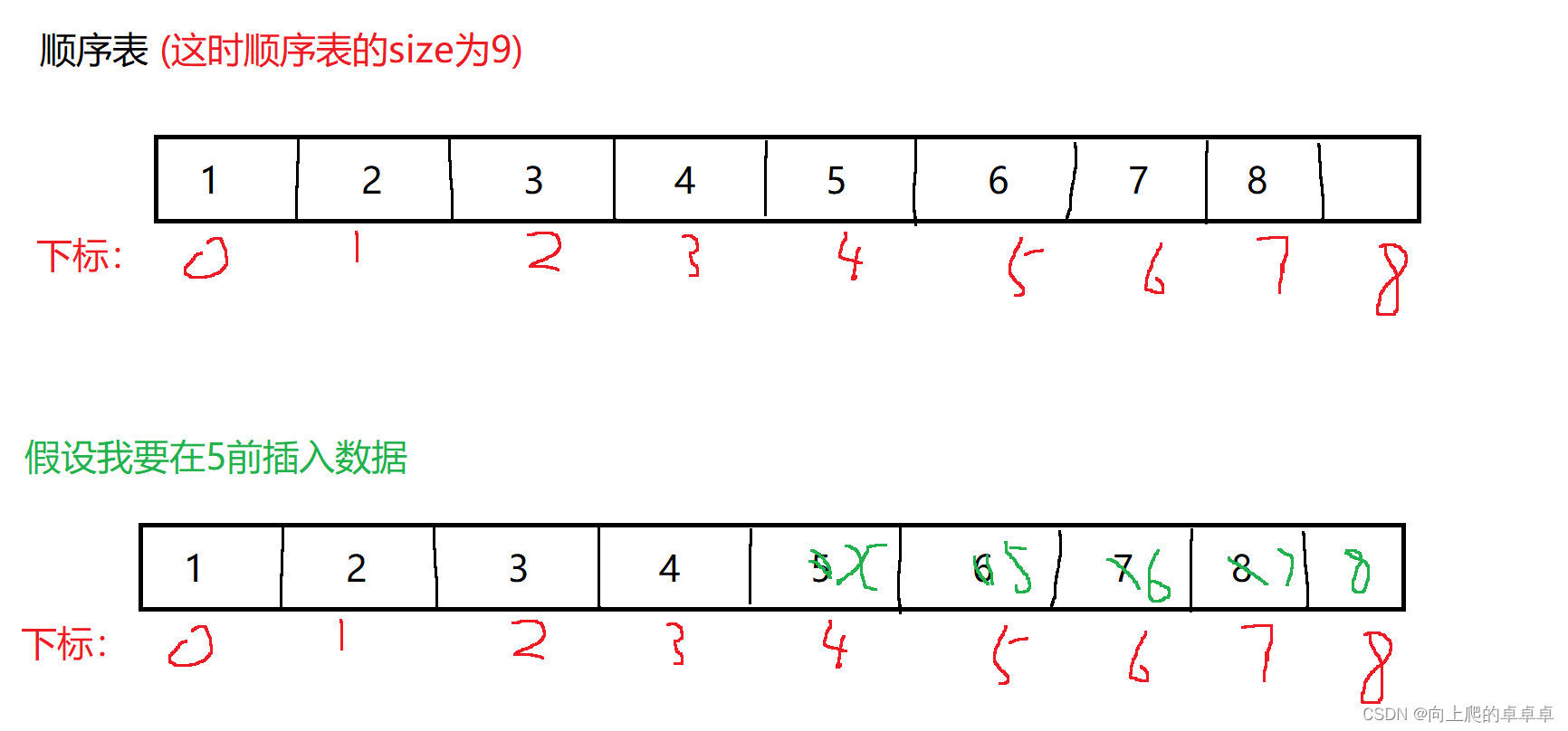

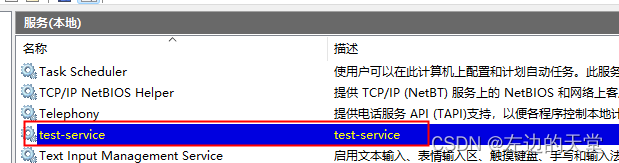

对于通用寄存器组的一些说明:上面总结的是考试时常用的通用寄存器,不同系统的通用寄存器组各有不同,比如X86架构下的通用寄存器组如下图:

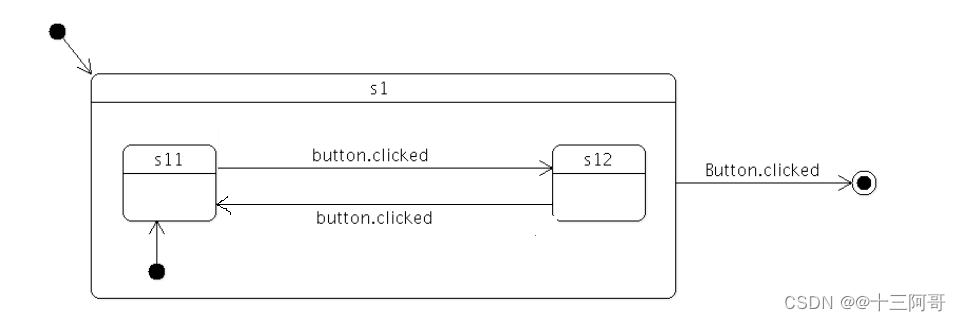

而ARM架构下的通用寄存器组如下图:

3.程序状态字寄存器(标志寄存器)(PSW):存放ALU运算得到的标志信息和处理机的状态信息,保留由算术逻辑运算指令或测试指令的结果而建立的各种状态信息如溢出标志(OF)、符号标志 (SF)、零标志 (ZF)、进位标志 (CF)等。PSW 中的这些位参与并决定微操作的形成;

4.暂存寄存器(Z、Y):用于暂存读来的数据,该数据不能存放在通用寄存器中,否则会破坏其原有内容,暂存寄存器对应用程序员是透明的;其中Z可以改造为移位器(T):对操作数或运算结果进行移位运算;

5.计数器(CT):控制乘除运算的操作步数;

(二)控制器

作用:指挥各部件协调进行工作,控制器的工作原理是,根据指令操作码、指令的执行步骤(微命令序列)和条件信号来形成当前计算机各部件要用到的控制信号。计算机整机各硬件系统在这些控制信号的控制下协同运行,产生预期的执行结果。

1.控制单元(CU):分析指令并发出各种微操作命令序列

(1)指令译码器(ID):对指令的操作码进行译码;

(2)时序系统(节拍发生器):信号来自机器主频(CLK);

(3)微操作信号发生器:将操作码转换为微操作;

(4)Reset(R):重置信号;

2.程序计数器(PC):存放下一条执行的指令地址;

3.指令寄存器(IR):存放当前执行的指令;

4.存储器地址寄存器(MAR):存放访存地址;

5.存储器数据寄存器(MDR):暂存要从存储器读或者写的信息;

注:步骤标记(标志)来自PSW

二、存储器(Memory)

作用:存放程序和数据;

(一)内存(主存)(MM)

作用:记忆信息。

1.存储体

2.读写电路

1)控制电路:其中时序系统产生存储器操作所需的各种时序信号,由统一时钟(Clock)分频得到,输入信号线为片选线、读写控制线;

2)读写信号线等;

3.译码驱动

1)地址译码器

2)驱动器

4.数据缓冲器

(二)高速缓冲存储器(Cache)

作用:介于CPU和内存之间,是CPU和RAM之间的桥梁,用于解决它们之间的速度冲突问题。

(二)外存(辅存)

作用:帮助主存记忆更多信息。

三、输入输出设备(I/O设备)

1.输入设备:将程序和数据以机器所能识别和接受的信息形式输入计算机;

2.输出设备:将计算机处理的结果以人们所能接受的形式或其他系统所要求的信息形式输出;

四、总线

1.地址总线:传送的是从CPU等主设备发往从设备的地址信号。

2.控制总线:传送的是一个部件对另一个部件的控制或状态信息,如CPU对存储器的读、写控制信号等。

3.数据总线:传送的是各部件之间交换的数据信息,数据总线通常是双向的。

写在后面

这个专栏主要是我在学习408真题的过程中总结的一些笔记,因为我学的也很一般,如果有错误和不足之处,还望大家在评论区指出。希望能给大家的学习带来一点帮助,共同进步!!!

参考资料

[1]王道408教材(2025版)

[2]王道课程资料