CPU指令集架构(ISA, Instruction Set Architecture)

CPU指令集架构是处理器硬件与软件之间的接口规范,它定义了一组基本指令,以及这些指令的操作格式、编码方式、寻址模式、寄存器组织、中断机制、异常处理等各个方面。ISA是计算机硬件设计的基础,决定了处理器能够理解和执行的指令类型及操作方式,是编写操作系统、编译器以及应用程序的基石。不同的ISA构成了不同类型的处理器,如x86、ARM、RISC-V、MIPS等。

LoongArch指令架构

LoongArch是龙芯中科(Loongson Technology)自主研发的一种指令集架构,专为中国的信息技术产业设计。它是龙芯团队在充分考虑兼容性、自主性、先进性、生态建设等因素的基础上,结合多年处理器研发经验和技术积累创建的全新架构。

LoongArch相比MIPS和RISC-V指令集架构,具有以下优势:

- 自主知识产权:

LoongArch是完全自主研发的指令集,不受外部专利约束,确保了中国在信息技术领域的自主可控性,这对于国家信息安全战略具有重要意义。相比之下,MIPS虽然也是开放架构,但其背后存在专利权属问题,而RISC-V虽然是开源指令集,但其生态中的相关实现可能受到第三方专利影响。

- 二进制翻译兼容性:

LoongArch设计时考虑了对多种主流指令集(如X86、ARM等)的二进制翻译支持,这使得已有的软件生态能够较为便捷地迁移到LoongArch平台上,降低了生态建设的门槛。MIPS和RISC-V虽然也有多平台移植工具,但LoongArch在设计层面的兼容性考量可能更为全面。

- 指令集扩展与优化:

LoongArch在基础指令集之外,提供了丰富的扩展指令集以支持特定应用领域的高效处理,如向量运算、并行计算、安全增强等,这些扩展可能在针对性和丰富程度上超越了MIPS和RISC-V的标准实现。尤其是对于高性能计算、安全应用等场景,LoongArch可能提供了更契合需求的定制化指令。

- 性能优化:

信息表明,LoongArch在指令格式、立即数大小、分支跳转范围等方面进行了优化设计,这些改进有利于减少编译结果的指令数量、减少访存次数,从而提高处理器效能。相比之下,尽管MIPS和RISC-V也强调性能效率,但LoongArch在某些具体设计上可能具有后发优势,能够更好地适应现代软硬件设计趋势。

- 生态建设与市场定位:

文献提及,LoongArch在桌面和服务器市场上相对于RISC-V具有优势,这反映在已经形成的软件生态、商业应用支持以及与特定行业标准的对接上。在高性能计算和关键基础设施领域,LoongArch可能通过与国内产业深度合作,更快地建立起符合特定行业需求的解决方案。相比之下,MIPS和RISC-V虽然也在积极发展生态,但可能在某些特定市场领域的成熟度和针对性上不及LoongArch。

- 技术演进与支持:

龙芯中科作为国内专注于处理器设计的企业,对LoongArch架构有着持续的研发投入和迭代升级能力。这意味着LoongArch有望随着技术进步不断更新和完善,以保持竞争力。相比之下,MIPS作为历史悠久的架构,其技术演进速度可能相对放缓,而RISC-V作为新兴开放架构,虽然社区活跃,但具体实现的演进速度和方向可能取决于社区共识和各参与方的努力。

对比

32位MIPS指令

- 组成部分与位数: MIPS 32位指令通常由以下几个部分组成:

-

操作码(Opcode):指定要执行的基本操作,通常占用6位。MIPS使用固定的指令长度(32位),操作码字段较小,意味着指令集相对紧凑。

-

寄存器源字段(RS, RT, RD):指定操作数所在的寄存器。MIPS有32个通用寄存器,通常使用5位来编码每个寄存器字段。

-

RS(Source Register):指定第一个源操作数所在的寄存器,一般为5位。

-

RT(Target Register):指定第二个源操作数或结果存放的寄存器,同样是5位。

-

RD(Destination Register):指定目标寄存器,存放运算结果,也是5位。

-

立即数(Immediate Value):直接包含在指令中的数值,用于提供常数值或偏移量。立即数的位数根据指令的不同而变化,通常为16位。

-

函数代码(Function Code, Func):对于某些指令(如jr、jalr),用于指定特殊操作的附加信息,占用6位。

-

移位量(Shift Amount, SA):在涉及逻辑或算术移位的指令中,指定移位的位数,通常为5位。

-

内存地址计算字段:

-

基址寄存器(Base Register, BASE):指定内存访问的基地址寄存器,5位。

-

偏移量(Offset):对于内存访问指令,提供一个16位的有符号立即数偏移量,用于计算最终内存地址。

2.指令种类: MIPS指令集主要包括以下几种类型的指令:

- 算术逻辑指令(ALU Operations):如加减乘除、位逻辑操作等。

- 数据传送指令(Data Transfer):包括寄存器间的数据移动、加载/存储内存数据等。

- 分支指令(Branches):条件分支、无条件跳转、子程序调用/返回等。

- 延迟槽(Delayed Slot):MIPS使用延迟分支机制,分支指令后的下一个指令(延迟槽)通常用来填充流水线,以提高处理器效率。

- 系统控制指令(System Control):如中断处理、特权级别切换等。

RISC-V 32位指令

1.组成部分与位数: RISC-V 32位指令采用变长编码,但最常见的是压缩(C)扩展后的16位指令和标准32位指令。这里主要描述32位指令格式:

-

操作码(Opcode):指示基本操作,RISC-V 32位指令的操作码通常占7位。

-

寄存器字段(Rs1, Rs2, Rd):分别指定源寄存器和目标寄存器,通常每个字段为5位,共计15位。

-

Rs1:第一个源寄存器。

-

Rs2:第二个源寄存器(某些指令可能只有一个源寄存器)。

-

Rd:目标寄存器,存放运算结果。

-

立即数(Immediate Value):不同指令的立即数位数和格式各异,可以是12位、20位等,具体取决于指令类型和所采用的立即数编码方案。

-

功能编码(Funct3, Funct7):进一步细化操作码,提供指令子类型或特定操作信息。Funct3通常占3位,Funct7占7位。

2.指令种类: RISC-V指令集同样包括多种指令类型:

- 算术逻辑指令(ALU Operations):如加减乘除、位逻辑操作、比较等。

- 数据传送指令(Load/Store):包括寄存器到寄存器的数据移动、从内存加载数据到寄存器、将寄存器数据存储到内存等。

- 分支指令(Branches and Jumps):条件分支、无条件跳转、间接跳转、子程序调用/返回等。

- 压缩指令(Compressed Instructions):16位压缩指令集,提供更高效的编码以减少代码大小。

- 向量指令(Vector Extension, V):可选扩展,支持SIMD(单指令多数据)操作,高效处理大量数据。

- 浮点指令(Floating-Point Extension, F/D/Q):支持单精度、双精度和四精度浮点运算。

- 其他扩展指令:如原子操作(A)、乘法累加(M)、特权指令(P)、用户级中断(U)等。

LoongArch 32位指令

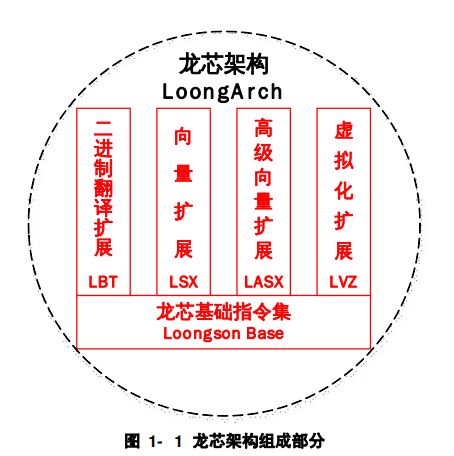

LoongArch架构采用基础部分(Loongson Base)加扩展部分的组织形式。其中扩展部分包括:二进制翻译扩展(Loongson Binary Translation,简称 LBT)、虚拟化扩展(Loongson Virtualization,简称LVZ)、向量扩展(Loongson SIMD Extension,简称 LSX)和高级向量扩展(Loongson Advanced SIMD Extension,简称 LASX)。MIPS,RISC-V,LoongArch 32位指令集都有自己的指令集编码格式,都有着完备的基础功能,但LoongArch的指令集编码格式更加的复杂,包含了更多的指令类型和操作数。

个人认为的很有特征的点

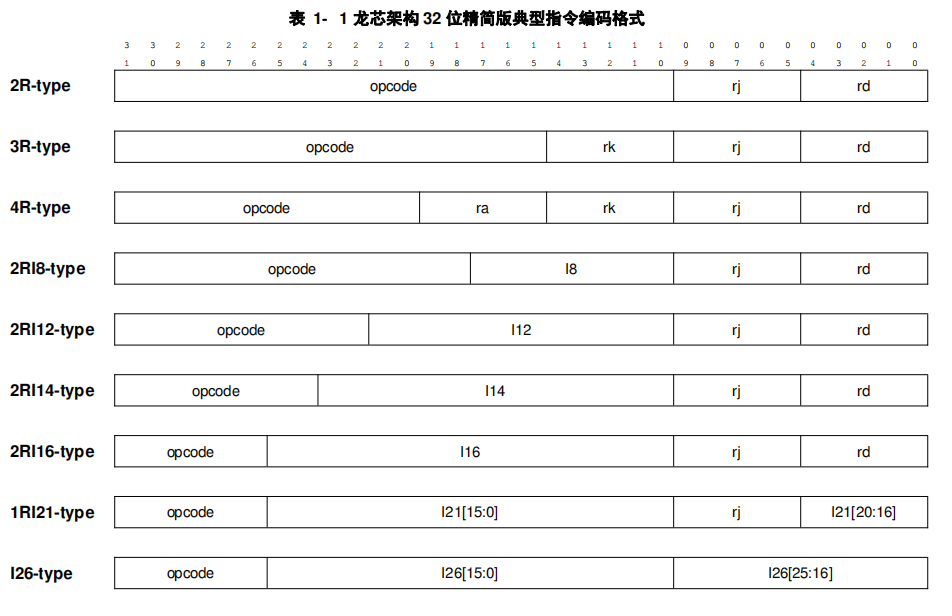

操作码都是从第 31 比特开始从高到低依次摆放。如果指令中包含有立即数操作数,那么立即数域位于寄存器域和操作码域之间,根据不同指令类型有不同的长度。具体来说,包含 9 种典型的指令编码格式,即 3 种不含立即数的编码格式 2R、3R、4R,以及 6 种含立即数的编码格式 2RI8、2RI12、2RI14、2RI16、1RI21、I26。

以下图片来自于LoongArch官方文档:龙芯架构32位精简版参考手册_v1.03.pdf

这就表明LoongArch的扩展性更加的强大,可以支持更多的指令类型和操作数,而且指令集编码格式也更加的复杂,更加的适合于高性能计算、安全应用等场景。