IIC总线的一些特征

• 只要求两条总线线路 一条串行数据线 SDA 一条串行时钟线 SCL

• 每个连接到总线的器件都可以通过唯一的地址和一直存在的简单的主机 从机关系软件设定地

址 主机可以作为主机发送器或主机接收器

• 它是一个真正的多主机总线 如果两个或更多主机同时初始化数据传输可以通过冲突检测和仲裁

防止数据被破坏

• 串行的 8 位双向数据传输位速率在标准模式下可达 100kbit/s 快速模式下可达 400kbit/s 高速

模式下可达 3.4Mbit/s

• 片上的滤波器可以滤去总线数据线上的毛刺波 保证数据完整

• 连接到相同总线的 IC 数量只受到总线的最大电容 400pF 限制

应用优点

极低的电流消耗

抗高噪声干扰

电源电压范围宽

工作的温度范围广

两线――串行数据 SDA 和串行时钟

一般都是外接上拉电阻

电阻不能太小,一般是4K-10K,电阻过小,上拉不可控

SCL 线在连接到总线的器件间传递信息 每个器件都有一个唯一的地址识别

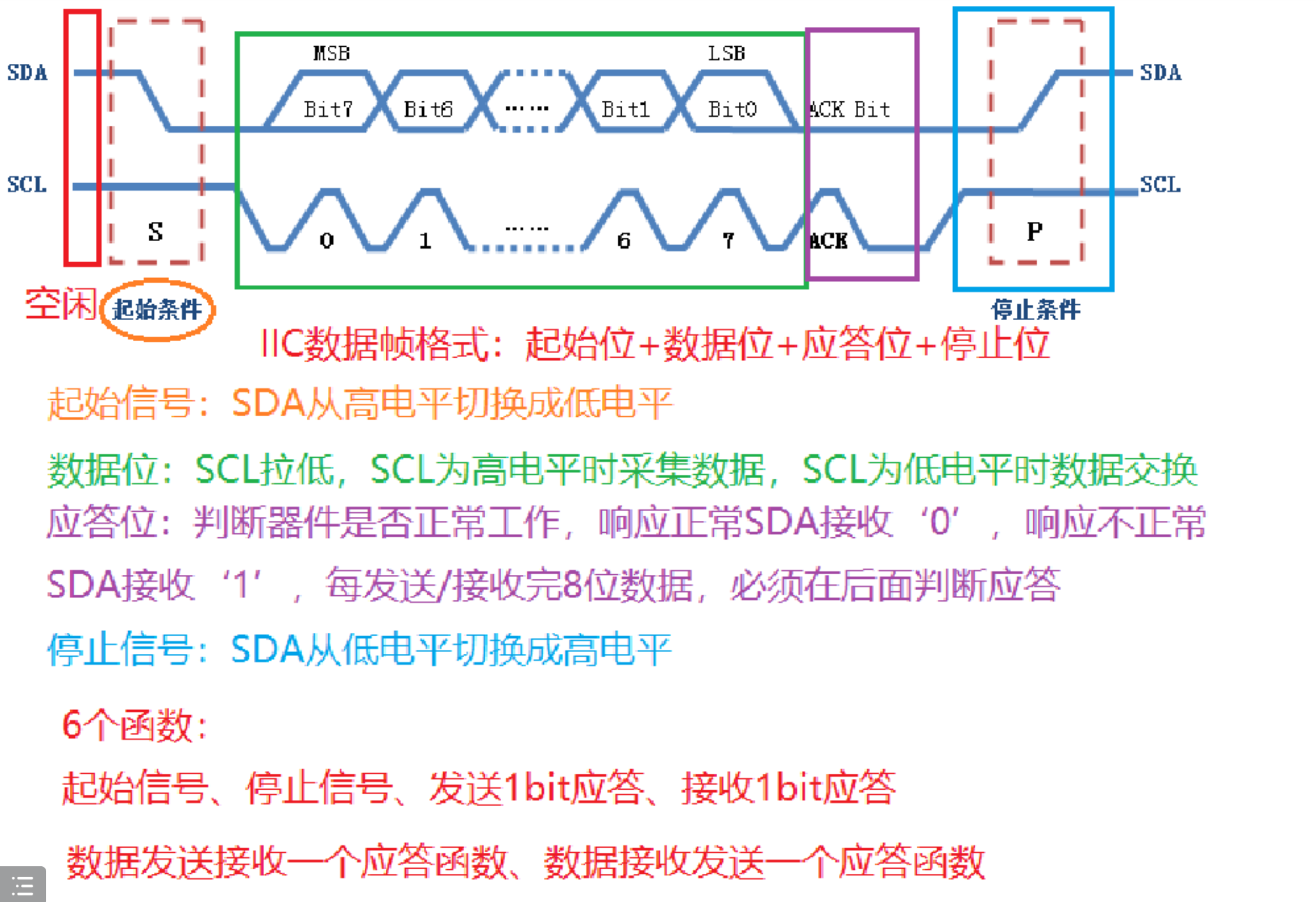

在 IIC 总线中 唯一出现的是被定义为起始 S 和停止 P 条件 见下图的情况,也就是起始信号和停止信号

发送到 SDA 线上的每个字节必须为 8 位 每次传输可以发送的字节数量不受限制 每个字节后必须跟一个响应位

首先传输的是数据的最高位

因为IIC是半双工通信,所以不是同时进行收发数据,时钟线拉低一瞬间发送数据,或者说SCL拉高一瞬间接收数据

下图有点差异,可以理解为在边沿触发的一瞬间就开始了通信,然后需要延时保证通信的完整性,这个延时是必须要有的且非常重要,一般6微秒比较通用,每次主动发起边沿就加上延时等待边沿变化完成,基本能保证框架的有效性。

标准模式100kbit/s:5 - 6us

快速模式400kbit/s:2 - 3us

IIC总体数据交互时序图:

起始信号:

IIC_SDA_H;

IIC_SCK_H;

TIM5_delay_us(us);

//在进行发送起始信号前,默认为拉高的SCK和SDA

//拉低SDA

IIC_SDA_L;

TIM5_delay_us(us);停止信号:

IIC_SDA_L;

//拉高SCK

IIC_SCK_H;

TIM5_delay_us(us);

//等待后拉高数据线

IIC_SDA_H;

TIM5_delay_us(us);

//等待后进行操作

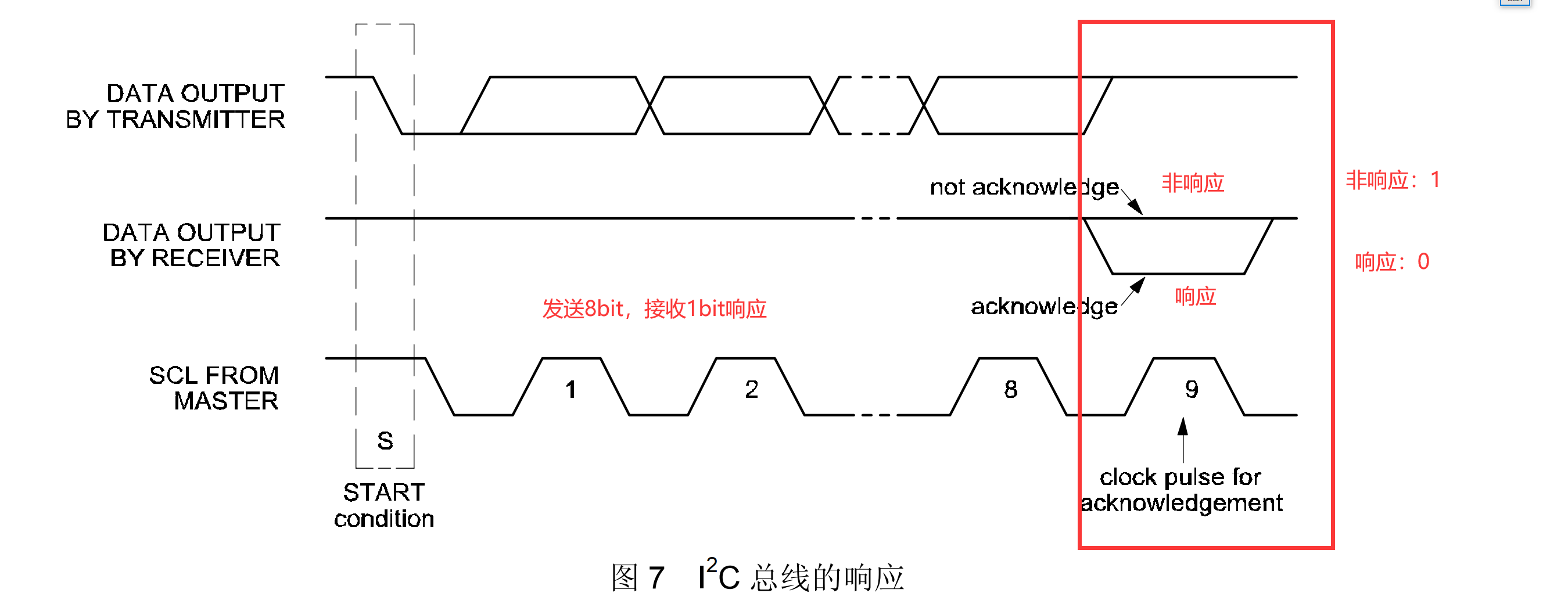

每发送或者接收完8bit数据后必须要有的应答信号,接收8位数据发送一位应答,发送8位数据接收一位应答,0表示成功应答,1表示无应答

发送应答:在接受完第8位数据后,SCL拉低,马上发送1位应答,然后等待,等待后已经是低电平,这时为了周期的完整性要把CLK拉高,然后延时,这样周期才完整

//SCK拉低准备发送

IIC_SCK_L;

//拉低马上发送 发送是在拉低的一瞬间开始

if(ack)

{

IIC_SDA_H;

}

else

{

IIC_SDA_L;

}

TIM5_delay_us(us);//等待数据发送完,也就是一个边沿变化缓冲时间

//等待后拉高时钟线

IIC_SCK_H;

TIM5_delay_us(us);

IIC_SCK_L;

TIM5_delay_us(us);//这里必须拉低,对于多位数据来说接收应答:在发送完第8位数据后,让SDA输出高电平,因为配置的时候是SCL为通用推挽输出,SDA为通用开漏输出,SDA输出1为高阻态,输出完全关闭,切换为输入状态,这样就可以接收来自SDA的数据,,拉高SCL,马上接收1位应答,然后等待,等待后已经是高电平,这时为了周期的完整性要把CLK拉低,然后延时,这样周期才完整

u8 ack = 0;

IIC_SDA_H;//开漏拉高输出关闭,进行输入

IIC_SCK_L;

TIM5_delay_us(us);

//SCL拉高准备接收

IIC_SCK_H;

//拉高马上接收

if(IIC_SDA)

{

ack = 1;

}

TIM5_delay_us(us);

//等待后拉低

IIC_SCK_L;

TIM5_delay_us(us);

return ack;

上面是整个IIC的框架,需要对时序进行充分理解,且必须要保证框架的可用性,不能有一点差错