Versal

串行

I/O

硬件调试流程

Versal

™

ACAP

无需再生成

IBERT IP

,

因为使用系统内串行

I/O

调试所需的必要逻辑现已集成到

GTY

收发器架构内。使

用

GTY

收发器的任何设计均可用于串行

I/O

硬件调试。

Versal

串行

I/O

硬件调试流程具有

2

个不同阶段

:

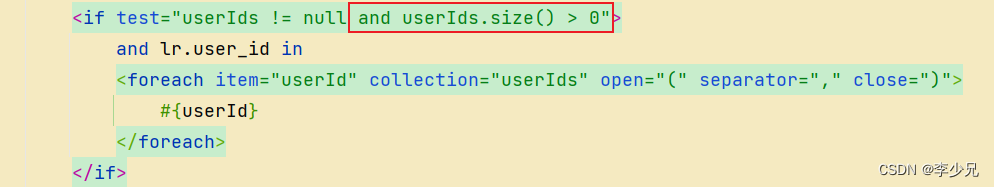

1.

设计创建

:

自定义并生成使用器件

GTY

收发器的设计

,

这通常是使用

Versal ACAP Transceivers Wizard

来完成

的。

2.

串行

I/O

分析阶段

:

使用

Vivado

®

硬件管理器与设计中的

GTY

收发器进行交互

,

以对高速串行

I/O

链路中的问题

进行调试和验证。

在硬件中调试串行

I/O

设计

实现

IBERT

核后

,

您可使用运行时串行

I/O

分析器功能来对硬件中的设计进行调试。仅限

IBERT

核

v3.0

版本和更高版

本才能使用串行

I/O

分析器功能来访问。

使用

Vivado Serial I/O Analyzer

来调试设计

Vivado

®

Serial I/O Analyzer

功能用于与设计中的

IBERT

调试

IP

核进行交互。要访问

Vivado Serial I/O Analyzer

功

能

,

请单击

Flow Navigator

的“编程和调试”部分中的“

Open Hardware Manager

”按钮。

对硬件中的设计进行调试的步骤如下

:

1.

连接到硬件目标并使用比特文件对

FPGA

进行编程。

2.

创建链路。

3.

修改链路设置并检验状态。

4.

按需运行扫描。

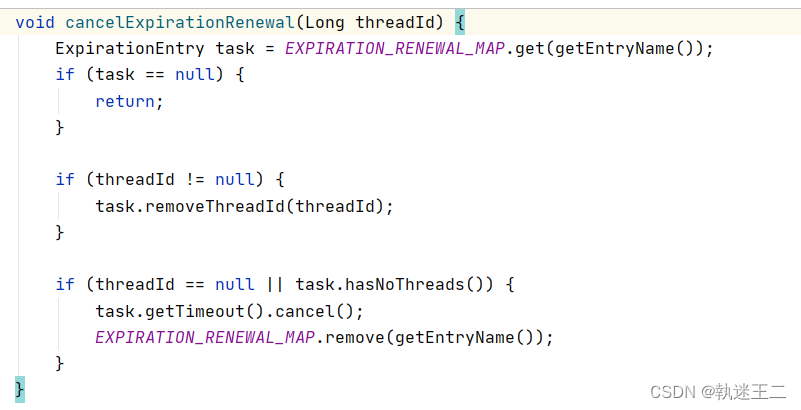

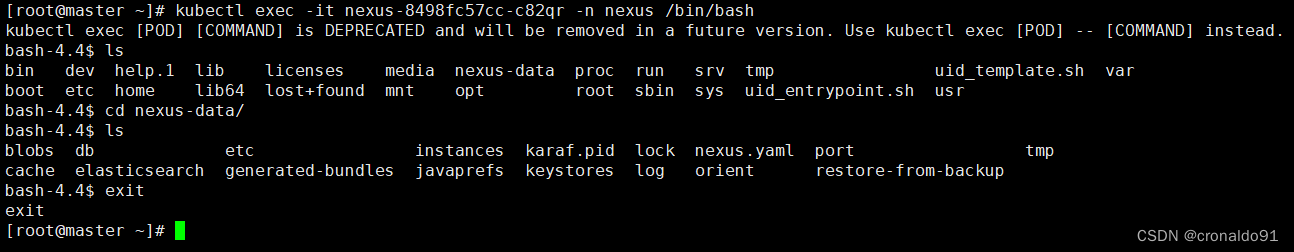

连接至硬件目标并执行器件编程

在调试前对

FPGA

或

ACAP

执行编程的步骤与“对

FPGA

或

ACAP

进行编程”中所述步骤完全相同。使用包含

IBERT

核的

.pdi

文件完成器件编程后

,

“硬件

(Hardware)

”窗口就会显示

IBERT

核的组件

,

并在其右侧括号内显示扫描器

件时检测到的

RTL

实例名称

(

如下图所示

)

。

重要提示

!

如果在您的设计中为

UltraScale

和

UltraScale+

设计使用了

In-System IBERT IP

,

那么您将在

“

Hardware

”窗口中看到检测到的

In-System IBERT

核。

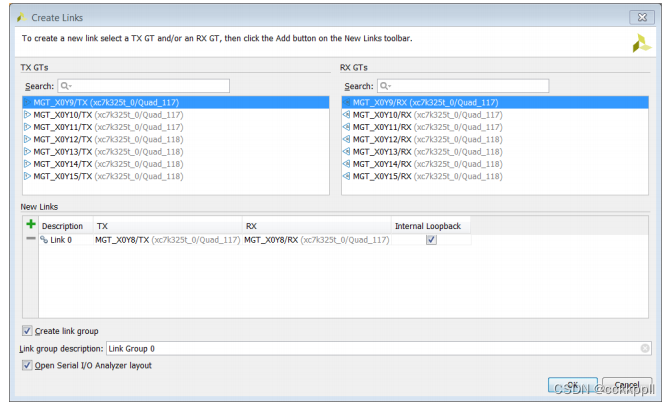

创建链路和链路组

设计中存在的

IBERT

核会显示在“硬件

(Hardware)

”窗口中的目标器件下。如果未显示此核

,

请右键单击器件并选中

“

Refresh Hardware

”命令。这样将重新扫描

FPGA

并刷新“

Hardware

”窗口。

注释

:

如果编程和

/

或刷新

FPGA

器件后仍未显示

IBERT

核

,

请检查并确保已使用正确的

.bit

文件完成了器件编程。此

外

,

请检查并确保已实现的设计包含

IBERT v3.0

核。

Vivado Serial I/O Analyzer

功能是围绕链路概念构建的。链路是开发板上通道的模拟链路

,

具有发射器和接收器。发射

器和接收器可能采用相同或不同

GT

、位于相同或不同器件上或者采用相同或不同架构。由于链路必须同时与发射器和

接收器关联

,

因此不支持将外部模式生成器连接到单一

GT

接收器。要创建

1

条或多条链路

,

请转至

Vivado

中的

“

Links

”选项卡

,

并单击“

Create Links

”按钮

,

或者右键单击并选择“

Create Links

”。这将显示“创建链路

(Create

Links)

”对话框

,

如下图所示。

检测到

IBERT

核时

,

硬件管理器会发现不存在任何链路

,

并在顶部显示绿色条幅。请单击“

Create Links

”以打开对话

框

,

如下图所示。

从可用列表中选择

TX

和

/

或

RX

。或者在搜索字段中输入字符串以缩小列表范围。然后单击“

+

”

(

添加

)

按钮

,

以将

链路添加到列表中。针对所有目标链路重复此过程。

重要提示

!

任一给定

TX

或

RX

端点只能属于单一链路。

链路还可包含在链路组中。默认情况下

,

所有新链路都分组在一起。您可通过取消选中“

Create link group

”来避免将

链路添加到同一组中。链路组名称可在“链路组描述

(Link group description)

”字段中指定。