A "population count" circuit counts the number of '1's in an input vector. Build a population count circuit for a 255-bit input vector.

译:

一个“population count”电路用于计算输入向量中'1'的数量。为一个255位的输入向量构建一个人口计数电路。

module top_module(

input [254:0] in,

output [7:0] out );

int i;

always@(*)begin

out=0;

for (i=0;i<255;i++) begin

if(in[i]==1'b1)begin

out = out + 1 ;

end

end

end

endmodule

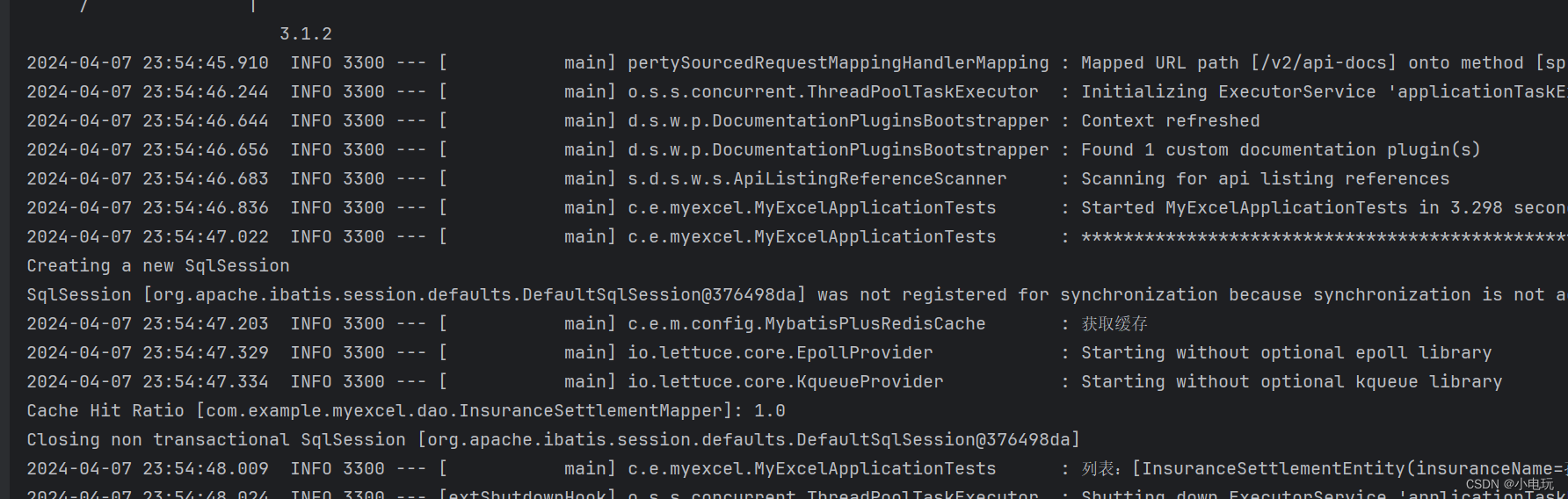

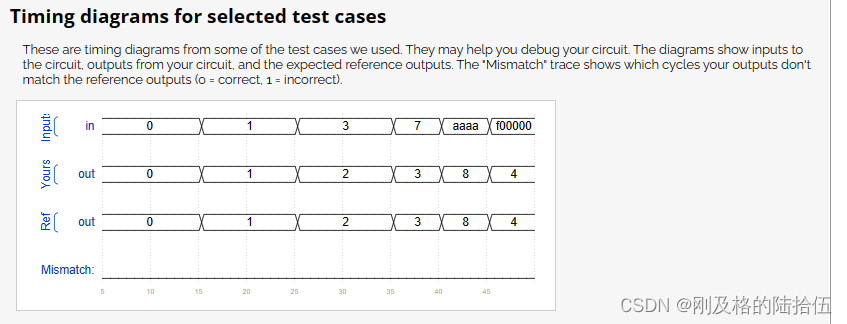

运行结果:

代码分析:

在做的过程中,我失误的一点在于没有写 out = 0 , 没有将它初始化,导致运行结果没有输出;下面解释下为什么必须要写这一行

在Verilog中的 always 块中,如果没有明确地将输出 out 赋值为0或者不对其进行任何操作,输出 out 的行为将是不确定的。这是因为在硬件描述语言中,信号的状态必须明确定义,否则它们不会自动初始化或保持在某个特定的状态。

out=0; 这一行是必要的,因为它确保了在每次 always 块触发时,输出计数器被重置为0。如果没有这行代码,输出 out 将保持其上一次的状态,这通常不是我们想要的行为,特别是在计算新的输入向量中 '1' 的数量时。

如果没有写 out=0;,那么在第一次执行 always 块时,out 可能会包含一个随机值或者保持其之前的值,这会导致计算的结果是不正确的。在硬件电路中,这种未定义的状态可能会导致电路无法正常工作或者产生错误的输出。

因此,为了确保每次计算都是从一个已知的初始状态开始,我们在处理计数器或者累加器时,通常会在每次循环或操作开始前将其重置为初始值。在这个例子中,就是在 always 块的开始处将 out 赋值为0,以确保正确计算输入向量中 '1' 的数量