1. 存储单元

1.1. 半导体

半导体(semiconductor)指常温下导电性能介于导体与绝缘体之间的材料。纯净半导体一般是四价原子(如硅或锗)。

1.1.1. P型半导体

P型半导体是通过将一个纯净的半导体材料(如硅或锗)中掺杂少量的三价杂质原子(如铝或硼)而形成的。这些杂质原子具有比半导体材料中的四价原子(如硅或锗)少一个电子。由于这个缺失的电子,形成了称为“空穴”的正电荷载流子。

在P型半导体中,空穴是主要的载流子,它们可以在材料中移动,并参与导电。当提供一定的外部电场激励时,空穴会在P型半导体中向负电极移动,形成正电流。

1.1.2. N型半导体

N型半导体是通过将一个纯净的半导体材料中掺杂少量的五价杂质原子(如磷或砷)而形成的。这些杂质原子具有额外的电子,这些额外的电子可以自由地在材料中移动。

在N型半导体中,自由电子是主要的载流子,它们可以在材料中移动,并参与导电。当提供一定的外部电场激励时,自由电子会在N型半导体中向正电极移动,形成负电流。

1.1.3. 二级管

二极管是一种最简单的半导体器件,由P型半导体和N型半导体组成。它具有两个电极,分别称为阳极(A)和阴极(K),其中阳极连接到P型半导体,阴极连接到N型半导体。

当二极管处于正向偏置时,即阳极连于正电压源,阴极连于地或负电压源,P端与正极相连,而N端与负极相连。在这种情况下,电流可以自由地通过二极管,形成正向电流。当二极管处于反向偏置时,即阳极连于负电压源,阴极连于正电压源。在这种情况下,PN结会形成一个电位垒,阻碍电流通过。这就是二级管的特性,单向导流。

1.1. MOS管

金属氧化物半导体型场效应管(Metal Oxide Semiconductor Field Effect Transistor,MOS-FET)是一种MOS管。

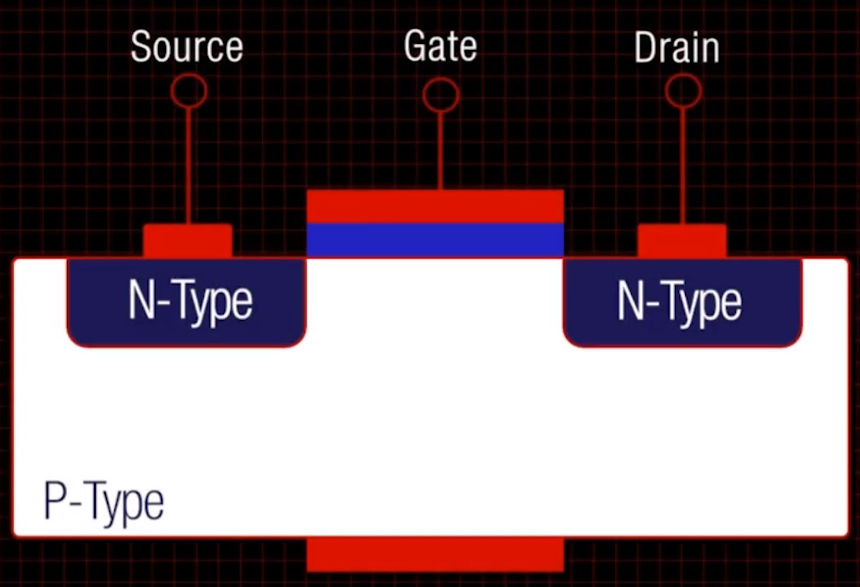

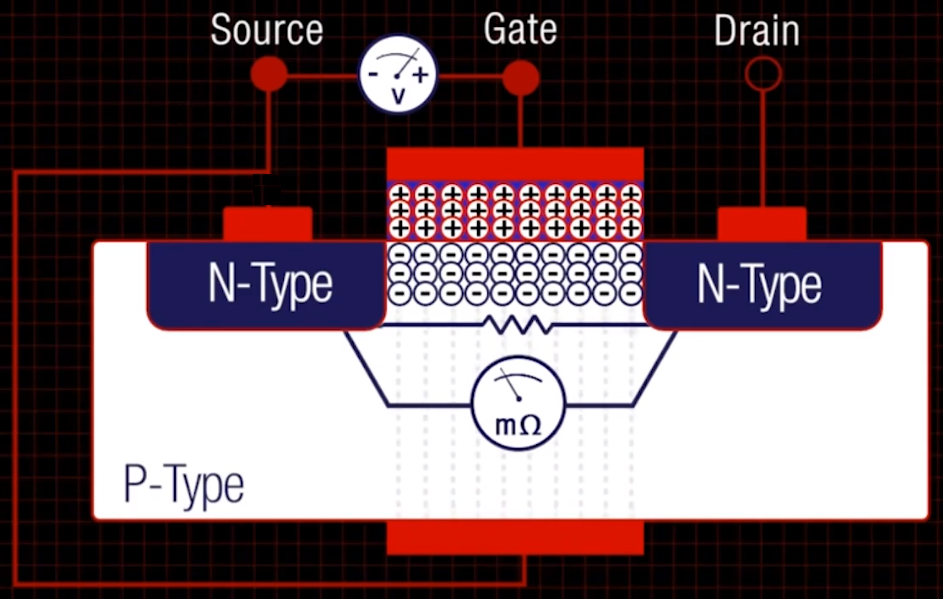

1.1.1 截止

下图中的红色方块为金属极,蓝色为氧化物,一般为二氧化硅(绝缘层)。当源极(Source)和漏极(Drain)接通电源时,由于两个N型半导体之间隔着P型半导体,因为P型半导体未加电场,P型半导体中的电子随机分布,无法为两个N型导通提供足够的电子通道。

1.1.2. 导通

当栅极(Gate)和P型衬底接通电源时,因为电场的缘故,P型半导体中的电子都往氧化绝缘层靠近,当绝缘层附近的电子足够多时,两个N型半导体之间的电子通道(N沟道)就形成了,两个N型半导体和中间的电子通道相当于一整个N型半导体。此时,在源极和漏极接上电源,就能够导通。

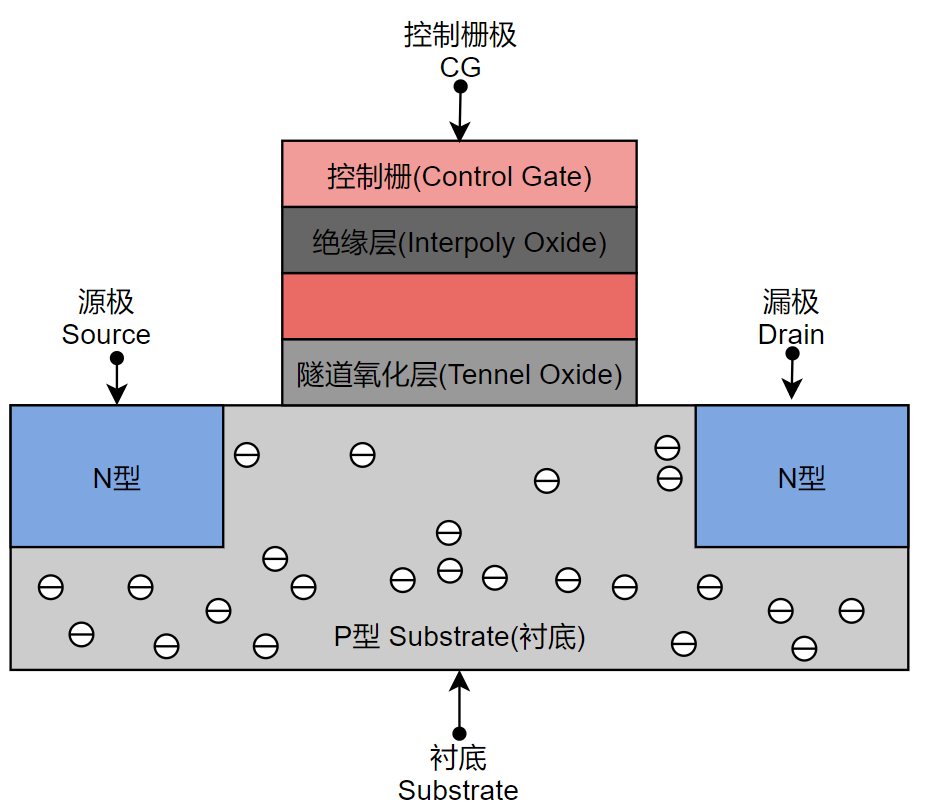

1.2. 浮栅MOS管

1.2.1. 概念

浮栅MOS管就是在MOS管栅极绝缘层中添加了一层浮栅层,浮栅层一般是金属或半导体。在控制栅和P型衬底接通足够大的电压,P型半导体中的电子会穿过SiO_{2}隧道氧化物绝缘层(这是因为隧穿效应)达到浮栅层。当断开控制栅的电源时,浮栅层的电子因为两边的绝缘层的阻隔,继续留在浮栅中,这样就达到存储的效果。

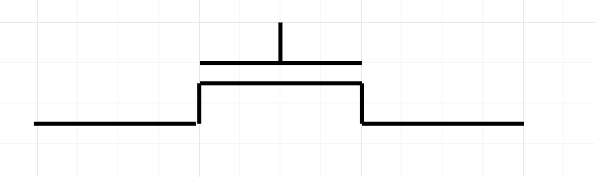

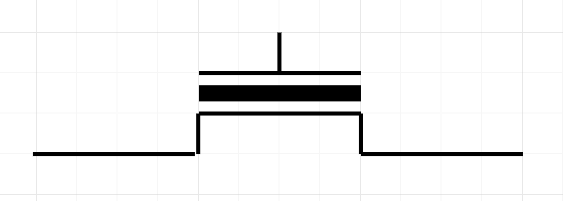

浮栅MOS管(Floating Gate MOSFET)符号:

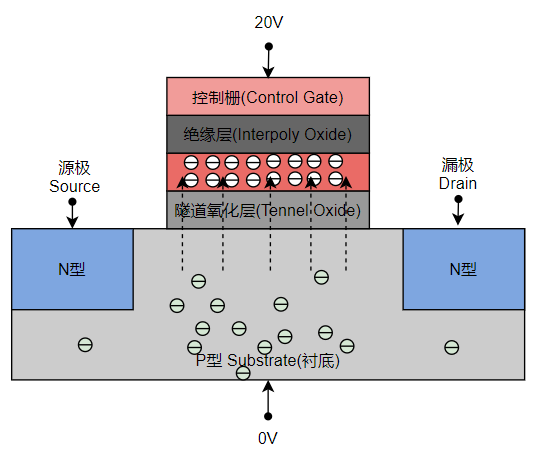

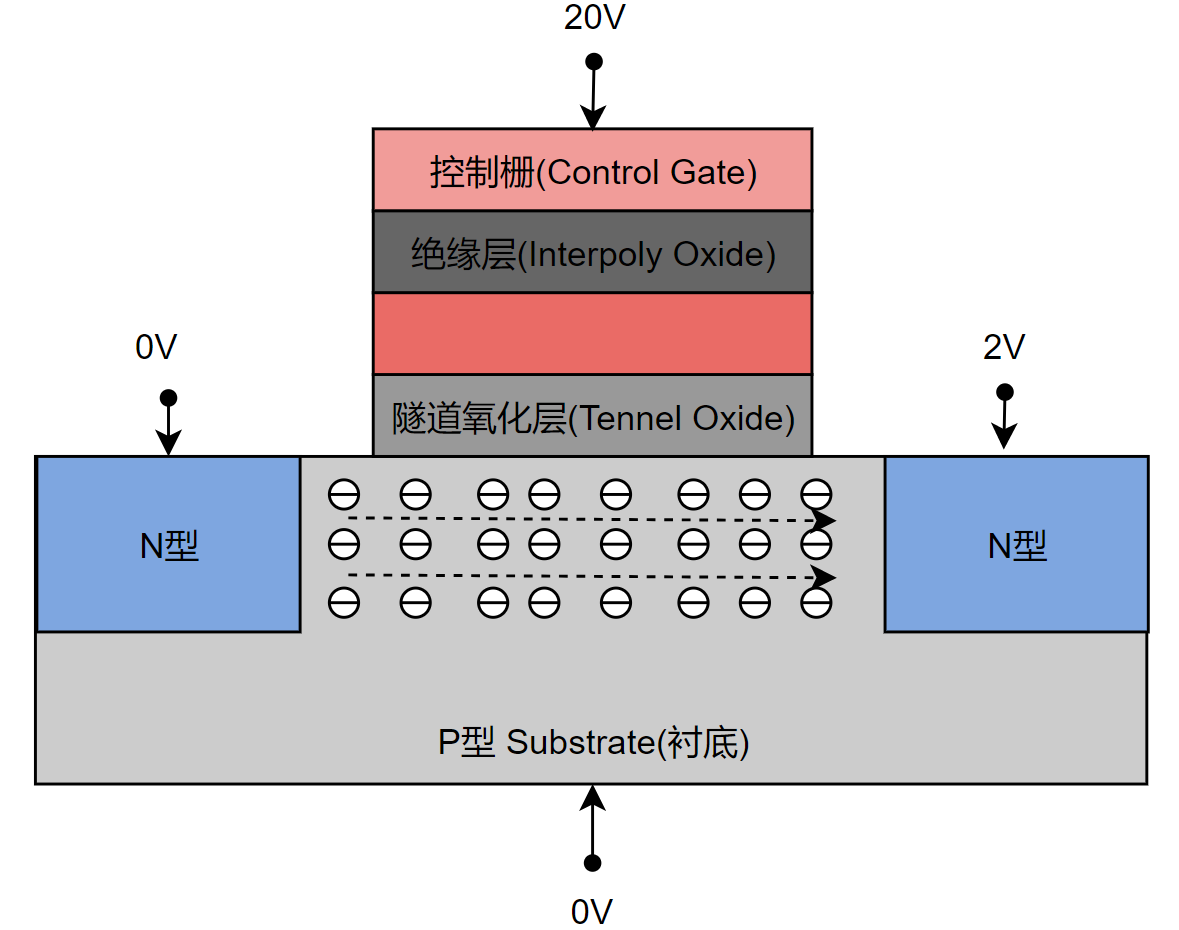

1.2.2. 写

写可以理解为充电,如下图,在控制栅加20V电压,在电场的作用下(因为电场足够,且隧道氧化层很薄,就会发生隧穿效应)P型半导体中的电子就穿过隧道氧化绝缘层进入浮栅层。在写操作完成之后,控制栅断开电源,浮栅层继续保存电子,达到存储信息的结果。写操作一般被理解为写0。

注意,在写的时候,如果给源极和漏极添加电压,那么就会在N型之间形成电子通道,源极和漏极直接导通了,电子将从源极向漏极流动,而不会穿透隧道氧化层进入浮栅层。

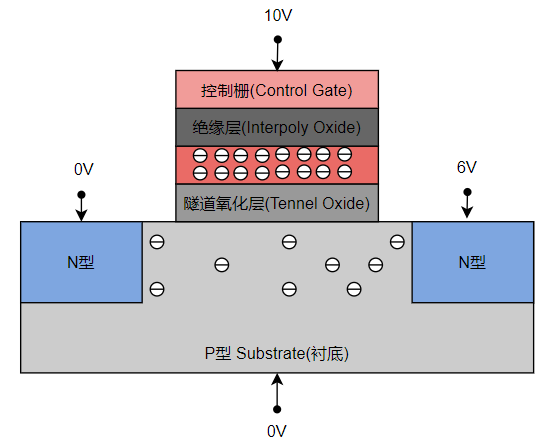

1.2.3. 读0

因为大部分电子已经被吸到浮栅导以,当控制栅加10V电压时,只有部分电子聚集到两个N型半导体之间,这些电子不够形成一个电子通道,导致源极和漏极之间无法导通,此时表示读到0。

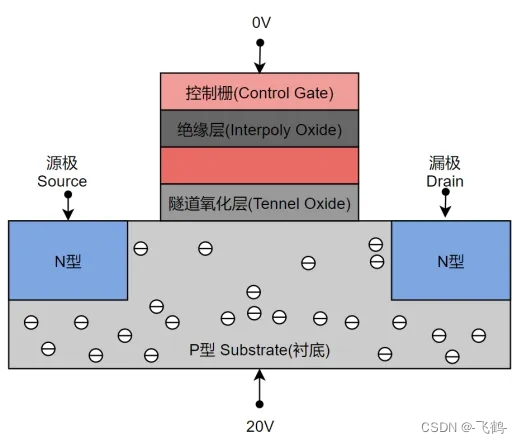

1.2.4. 擦除

擦除可以理解为放电,相当于写1,简单来说就是控制栅接地,衬底接20V,这样浮栅中存储的电子又被电场吸引到P型半导体中,浮栅中就不再存在多作的电子。

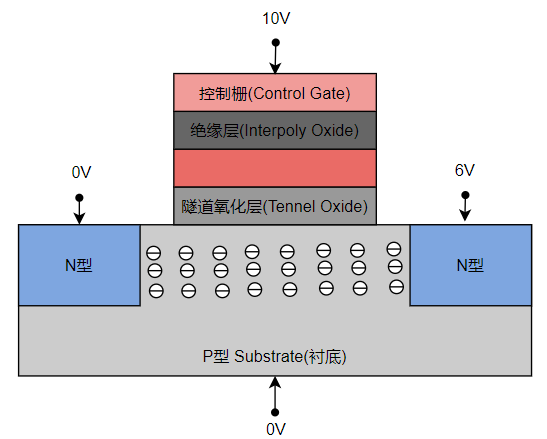

1.2.5. 读1

擦除之后读,因为浮栅层的电子全部释放回了P型半导体中,这时在控制栅加10V电压,P型半导体中的电子会聚集到N型半导体之间形成电子通道,源极和漏极之间接上电源,会导通,此时表示读到‘1’。

1.2.6 阈值电压

阈值电压(Threshold Voltage, Vth),就是浮栅MOS管源极漏极导通时栅极需要加的电压。通过控制P型衬底、N型极中的杂质含量,在浮栅中新增电荷为0时,可以让控制栅接0V或负电压时,源极和漏极就能够导通。NAND Flash就是这样的设计。Cell的实际的导通电压可以称为源阈值电压,而校验值的阈值电压可以称为目标阈值电压。

1.3. 多状态

早期浮栅MOS管只能存储1Bit,表示0和1。后来随着技术的发展,浮栅MOS管可以存储2bit、4bit、8bit甚至16bit。

1.3.1. 原理

在控制栅和衬底之间加20V电压,可以触发隧道氧化层发生隧穿效应,P型半导体中的电子会穿越隧道氧化层到达浮栅层。继续加大控制栅的电压,以及持续的时间,可以控制到达浮栅层电子的数量。简单举例:

- 控制栅加20V电压,持续100ms,可以让浮栅层存储100个电子。此时要让源极和漏极导通,需要在控制栅加上10V电压,那么Vth=10V。

- 控制栅加21V电压,持续200ms,可以让浮栅层存储200个电子。此时要让源极和漏极导通,需要在控制栅加上11V电压,那么Vth=11V。

- 控制栅加21V电压,持续300ms,可以让浮栅层存储300个电子。此时要让源极和漏极导通,需要在控制栅加上12V电压,那么Vth=12V。

- 控制栅加22V电压,持续400ms,可以让浮栅层存储400个电子。此时要让源极和漏极导通,需要在控制栅加上13V电压,那么Vth=13V。

- 控制栅加23V电压,持续500ms,可以让浮栅层存储500个电子。此时要让源极和漏极导通,需要在控制栅加上14V电压,那么Vth=14V。

- 控制栅加24V电压,持续500ms,可以让浮栅层存储600个电子。此时要让源极和漏极导通,需要在控制栅加上15V电压,那么Vth=15V。

- 控制栅加25V电压,持续600ms,可以让浮栅层存储700个电子。此时要让源极和漏极导通,需要在控制栅加上16V电压,那么Vth=16V。

通过上面的示例可以看出,通过控制栅电压和时间来精确控制浮栅层存储的电子可以达到多bit信息的效果,然后通过不同的导通电压大小来确定具体存储的信息。

1.3.2. 1bit

存储0,让浮栅层存储100个电子;存储1,浮栅层释放所有电子即可。然后控制栅加10V电压,判断导通与截止即可以判断存储的是0还是1。导通电压大于等于10V即为1,不导通即为0。

1.3.3. 2bit

2bit可以表达4种状态,b10、b00、b01和b11。4种状态,需要3个分界线来区分,即3个导能电压Va(10V)、Vb(11V)、Vc(12v),可以称为阈值电压。

读操作,控制栅10V时,浮栅MOS管导通,判别为b11;如果不导通,则继续加大电压读。这种方式,针对b11需要1次读操作,针对b01需要2次读操作,针对b10和b00需要3次读操作。

假如从11V开始读,那么每个状态的判别均为2次操作。这种操作更稳定,实际的判别方式多为这种二分操作方式,更为稳定。

1.3.4. 3Bit

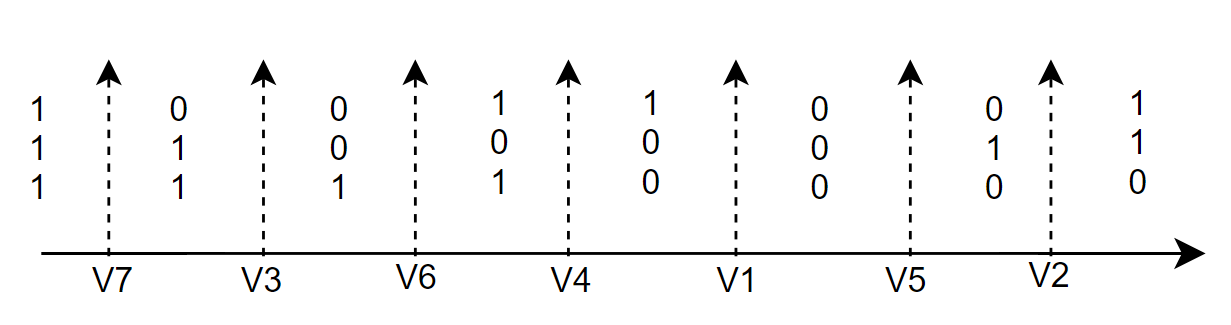

3bit可以表达8种状态b000、b001、b011、b111、b100、b110、b101、b000,需要7个阈值电压V1-V7来判别。读操作,先加上V4,导通为右边状态,不导通为左边状态,再读V3/V5,最后依次读出每一个状态。读出真实的状态,需要3步操作。

1.3.5. 更多Bit

通过更精确的控制浮栅电压和时间,达到更精确的存储电子的数量,再通过更对应的导通电压就可以达到存储更多位状态。如存储4bit的16个状态,存储5bit的32个状态。

2. NAND Flash

NAND Flash由许多存储单元(浮栅MOS管)构成存储阵列(NAND Array),达到可以存储大量的数据。NAND Flash根据存储单元中的状态数量,分为SLC(Single-Level Cell)、MLC(Multi-Level Cell)、TLC(Triple-Level Cell)、QLC(Quad-Level Cell、PLC(Penta-Level Cell)。

2.1. SLC

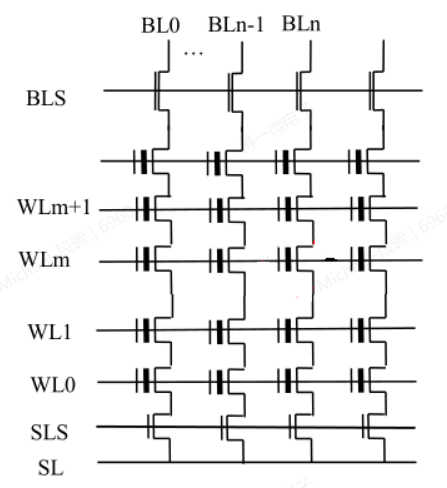

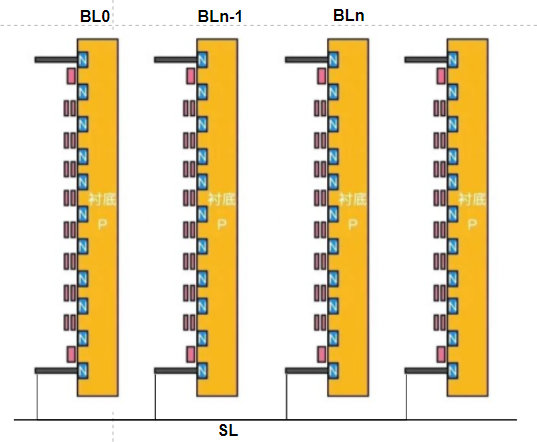

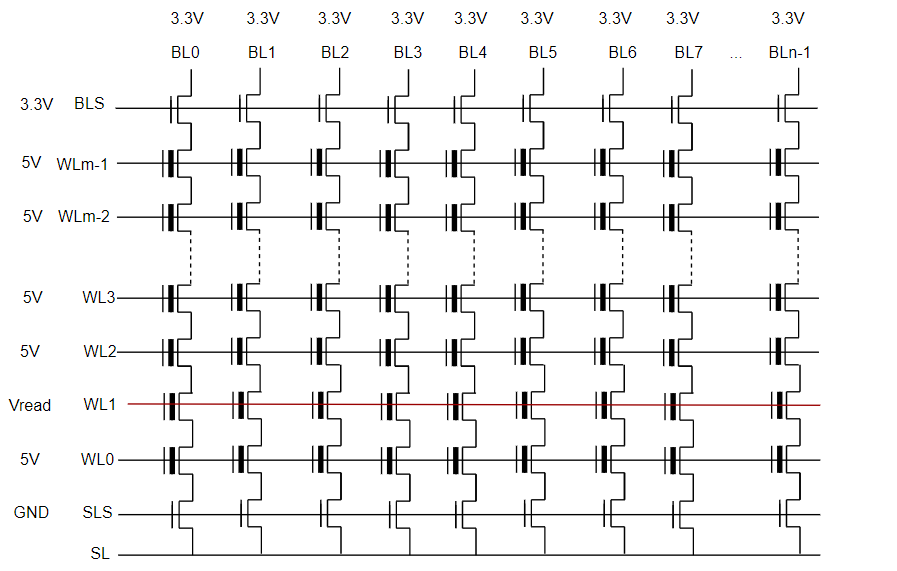

SLC(Single-Level Cell)因为只存储1bit,所以其存储、读取速度都比较快,并且可靠性也比较高,适用于一些对速度或可靠性有要求的场景。SLC 存储阵列由水平排列的MOSFET构成,其排列如下图:

行由Word Line(WL)连接,列由Bit Line(BL)连接,存储队列两边分别配置了普通MOS管,用来做开关。BLS(Bit Line Selector)用来控制位线的开断,SLS(Source Line Selector)用来控制源线的开断。ONFI (Open NAND Flash Interfact) 国际组织规定了NAND Flash的统一接口操作序列,如擦除、编程(写)、读等。

NAND Flash为了更好的操作,将存储阵列进行了更进一步的拆分管理,分为块(Block),块下面分为页(Page),页由连接在字线上的MOSFET构成。如果一款NAND Flash有2112个块,每个块有128个页,每个页有2112*8bit(MOSFET),总共512MB。

2.1.1. 擦除

一个块上所有的MOSFET的衬底都连接在一起,这样就可以同时擦除一个块上所有MOSFET的数据,所以擦除的速度非常快。

2.1.2. 编程(写)

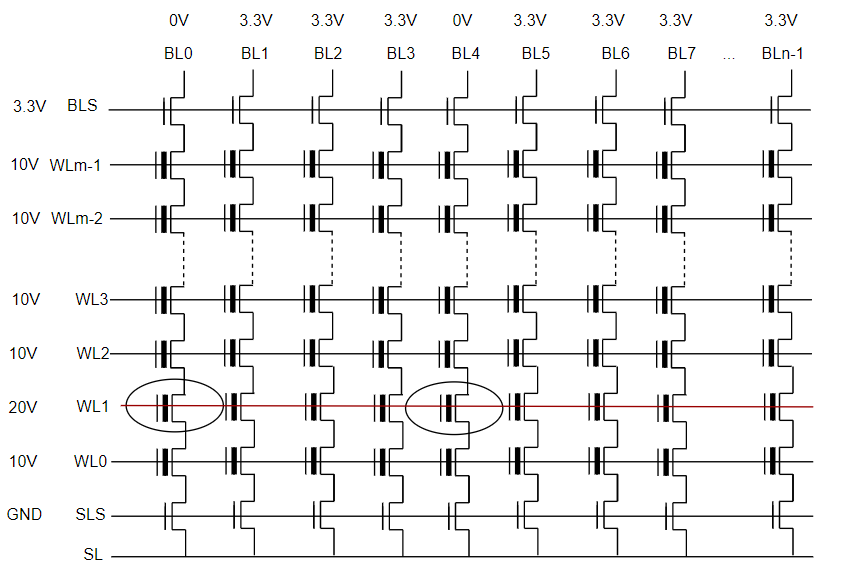

因为WL上的所有MOSFET的控制栅都连在一起,所以编程最小单位为WL,即一个页。如下图是一个块的存储矩阵,其有m个页,每个页有n个bit。在编程前,确认此块已经擦除,即所有MOSFET的浮栅中均没有存储电荷,即均表示1。要编程Page1,即WL1,对应的数据为b01110111...1,那么只需要 对Bit0、bit4进行编程即可。要给WL1编程,那么就需要在控制栅加上20V电压,然后所有的源极接地,然后所BLS导通,然后通过BL来控制具体的编程。

WL1所有的MOSFET的控制栅都加上了20V电压,但是只有Bit0、Bit4需要进行充电编程,其他bit不用编程。通过前文知道,如果在编程时,如果源极漏极接通电源,会导致N沟通形成,电子会在源极和漏极间传递,而不是进入浮栅层。所以其他不编程的MOSFET需要保持导通。那么其所在的整个位线上的MOSFET都需要导通。所有非编程WL都添加导通电压Vpp=10V,所有不用充电的MOSFET对应的BL都添加检测电压3.3V。

针对需要编程的MOSFET,只需要保证漏极没有接上电源,那么在20V的电压上,字线上没有接通电源的位线对应的MOSFET就会开始进行充电操作。充电是阶梯式往上充电,充一次电,然后在位上接上电源,检测是否导通,若是此位线导通,那么就继续导通,这样就相当于关闭了此位线的充电操作。依次直到所有位线都导通,就完成了整个WL的编程,也即页编程。然后依次可以给整个块完成编程,然后整个NAND Flash。

通过上面的编程步骤可以发现,给NAND Flash上写1会更容易,只需要控制栅加夺,然后并行检测位线是否导通即可。所以给NAND Flash写1会明显给写0快很多。

2.1.2.1. 编程操作

- 按需要写入的数据Bit,0对应0V,1对应3.3.V依次将所有位线设置相应的电压。

- 将加编程的字线加上20V电压,即完成编程。

2.1.2.2. 编程干扰

- 如果位线有Cell坏了或位线设置为0V,导致整个位线不导通,那么整个位线所在的Cell都会加上电压,导致弱编程现象,让电子更多地进入到浮栅中,导致相应Cell的阈值电压增大。

- 字线所在的Cell漏极设置为3.3V,源极漏极导通,但是控制栅上的20V电压和漏极3.3V电压的共同影响下,所在Cell的控制栅依然有8V左右的电压,依然会发生弱编程现象,同样会让Cell的阈值电压增大 。

2.1.3. 读

读0和读1会有两个阈值电压,先在栅极施加读0的阈值电压,检测是否导通,如果导通,输出1,结束。如果不导通,则再施加读0的阈值电压。为什么不设计为读1阈值电压不导通,直接认定为0呢?这是因为有可能读0时阈值电压也不导通,这个单元可能存在问题,或是1阈值电压要往下调。

2.1.3.1. 读操作

- 所有漏极均接上电源,所有非目标WL均接5V导通电压。

- 指定WL的栅极加上读1的Vth=0,如果当前位线导通,则当前位线WL对应的Cell存储的是1,否则为0。

2.1.3.2. 读干扰

当某个位线中有个Cell坏了时,导致整个位线无法导通,那么整个位线上被加5V电压的Cell可能存在一个弱编程的现象,会导致这些Cell的阈值增大。

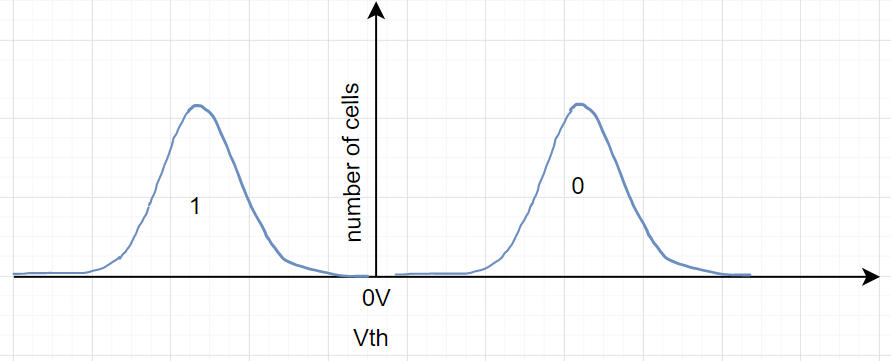

2.1.4. 阈值与电子分布

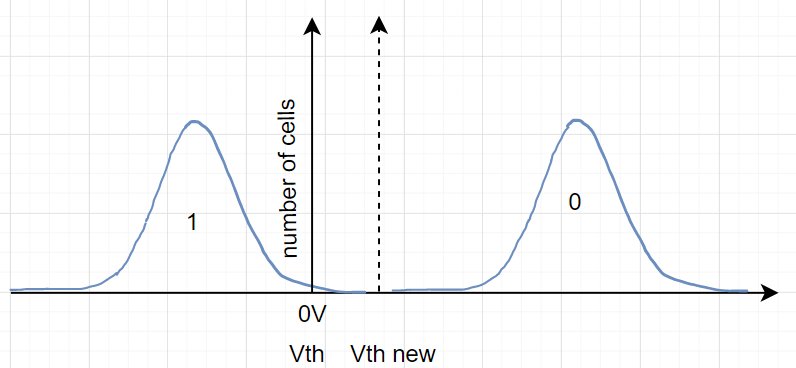

下图横坐标为栅极电压,纵坐标为NAND Flash在相应栅极电压下导通的Cell数量(0和1各一半随机分布在Flash上)。

当因为编程和读时产生的弱编程影响,Cell的导通电压会变大。目标阈值电压相对往后移了,此时为了更准确地区分所有的数据,可以将阈值电压增大。