DDR协议基础进阶(三)——(基本功能、初始化、MR寄存器)

一、DDR基本功能

DDR基本功能主要包括:

- 8-bit prefetch预取——8-bit,是指8位数据,即8倍芯片位宽的数据。由于DDR内部数据传输是32bit,外部pin口DQ位宽4bit(存储单元数据位宽),在发起读数据(写同理)操作时,会先从bank中取出32bit数据存入寄存器中,然后再将32bit数据由并转串发出去,完成读数据操作;相当于一次性从bank中获取了8倍的DDR数据接口位宽的数据放入寄存器中,这种存取数方式即为8bit prefecth预取。实际上DDR内部一次性获取了大量数据,而只是将DDR接口处时钟进行倍频以便做并转串或串转并操作,从而达到高速访问的效果。

- 双沿采样——DDR接口处时钟会在上下边沿进行采样,一个时钟周期内会采到两倍于DDR接口位宽的数据。

- Burst传输——可以是常规的burst length为8bit的传输,也可以是burst chop length=4bit的传输。

- 必须先Power up和初始化操作——在对DDR进行操作之前,需要先对其中的目标颗粒进行ACTIVE(激活)操作,在激活颗粒之前必须先对颗粒进行上电初始化,才可进行正常访问。

——————————————————————————————————————————————————————————————

1.1、什么是Prefetch?

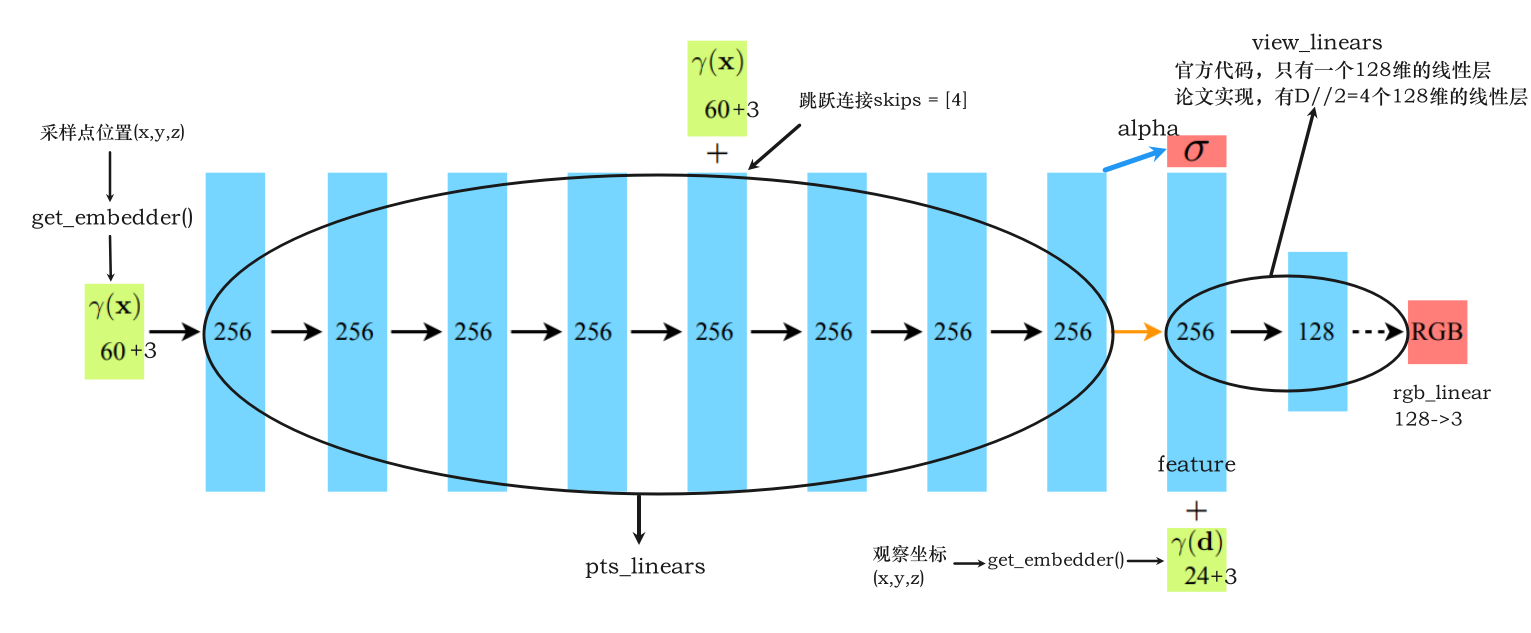

DDR核心技术点就在于:(1)双沿传输。(2)预取prefetch。

实际上,Prefetch并不是什么新技术,在DDR1就开始应用了,我们以前经常能看到这样描述DDR,“在时钟周期的上沿和下沿都能传输数据,所以传输率比SDRAM快了一倍”,这就说上沿传输一位数据,下沿传输一位数据,在一个时钟周期内一共传输两位数据(2-bit),但这2-bit数据得先从存储单元预取出来才行(一个时间周期)。换句话说,一次读2-bit的数据,然后在I/O时钟上升沿和下降沿传输出去,这就是2-bit Prefetch技术。当然这只是表面的解释,实际情况要比这复杂得多,要注意是,这儿的2-bit,是指2位数据,即2倍芯片位宽的数据。

在DDR2时代,使用了4-bit预取技术,一次从存储单元预取4-bit的数据,然后在I/O时钟上升沿和下降沿传输出去,由于4-bit需要2个时钟周期才能完成传输,这就是为什么DDR2的I/O时钟频率为存储单元频率两倍的原因。

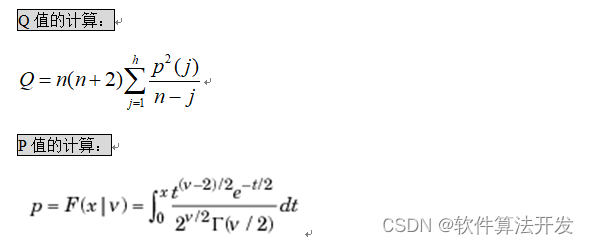

到了DDR3,8-bit预取技术也自然水到渠成,**一次从存储单元预取8-bit的数据,在I/O端口处上下沿触发传输,8-bit需要4个时钟周期完成,所以DDR3的I/O时钟频率是存储单元核心频率的4倍,由于是上下沿都在传输数据,所以实际有效的数据传输频率达到了核心频率的8倍。**比如,核心频率为200MHz的DDR3-1600,其I/O时钟频率为800MHz,有效数据传输频率为1600MHz。

显然,通过使用Prefetch架构可以解决存储单元内部数据总线频率(核心频率)较低的瓶颈。8-bit预取,正是DDR3提升带宽的关键技术。同样的核心频率,DDR3能提供两倍于DDR2的带宽。

总结: DDR SDRAM内部存储单元的核心频率提高比较困难且成本较高,为了解决外部数据传输率和核心速度之间的矛盾,DDR3引进了8-bit Prefetch(数据预取架构)技术,它能够提供比DDR2更高的数据传输率。

1.2、时钟频率关系

DDR的频率:(1)核心频率、(2)时钟频率、(3)数据传输频率;核心频率就是内存的工作频率;DDR1内存的核心频率是和时钟频率相同的,到了DDR2和DDR3时才有了时钟频率的概念,就是将核心频率通过倍频技术得到的一个频率。数据传输频率就是传输数据的频率。DDR1预读取是2位,DDR2预读取是4位,DDR3预读取是8位…

- 表中的I/O频率即为时钟频率,如下图所示;

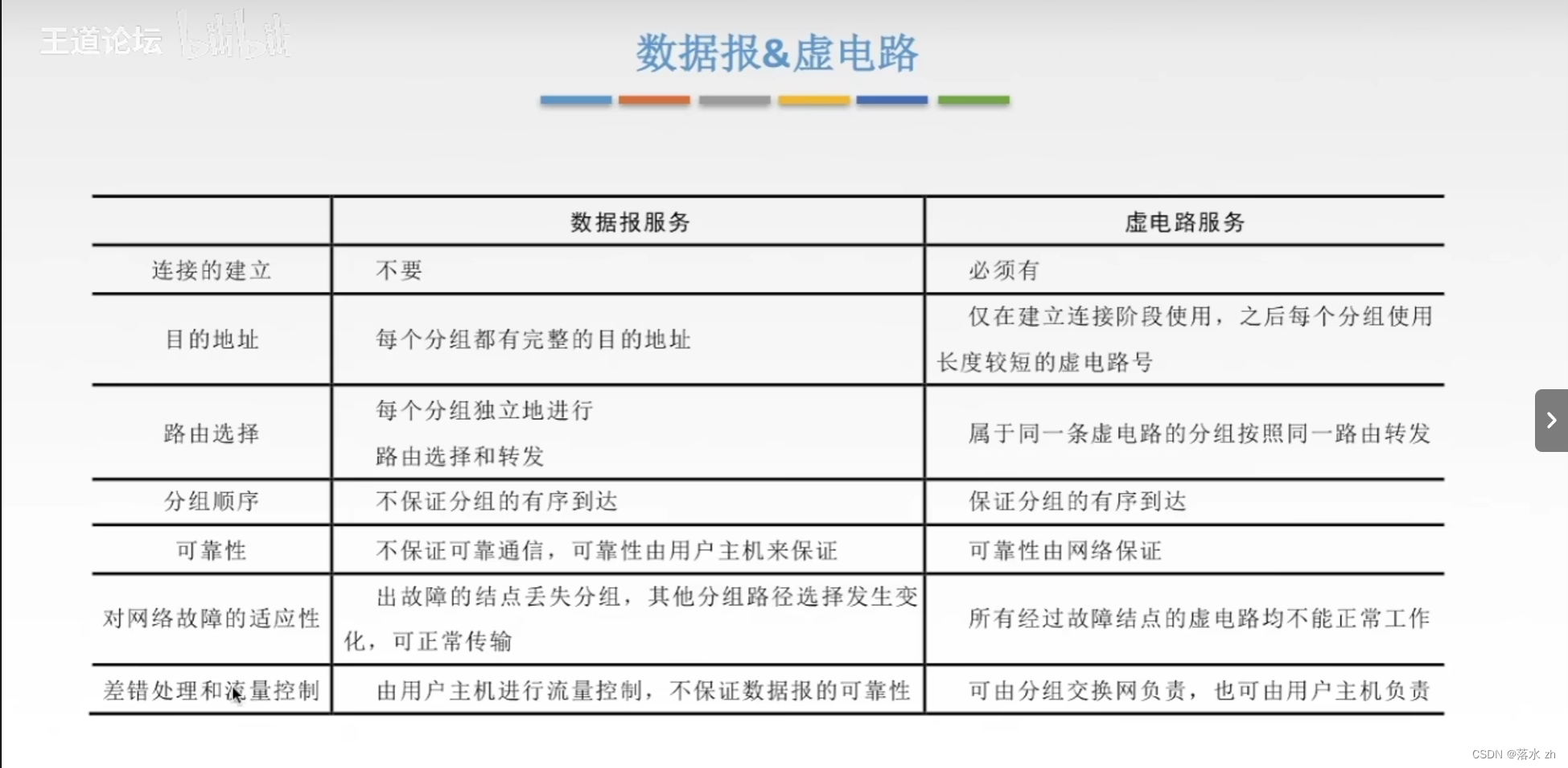

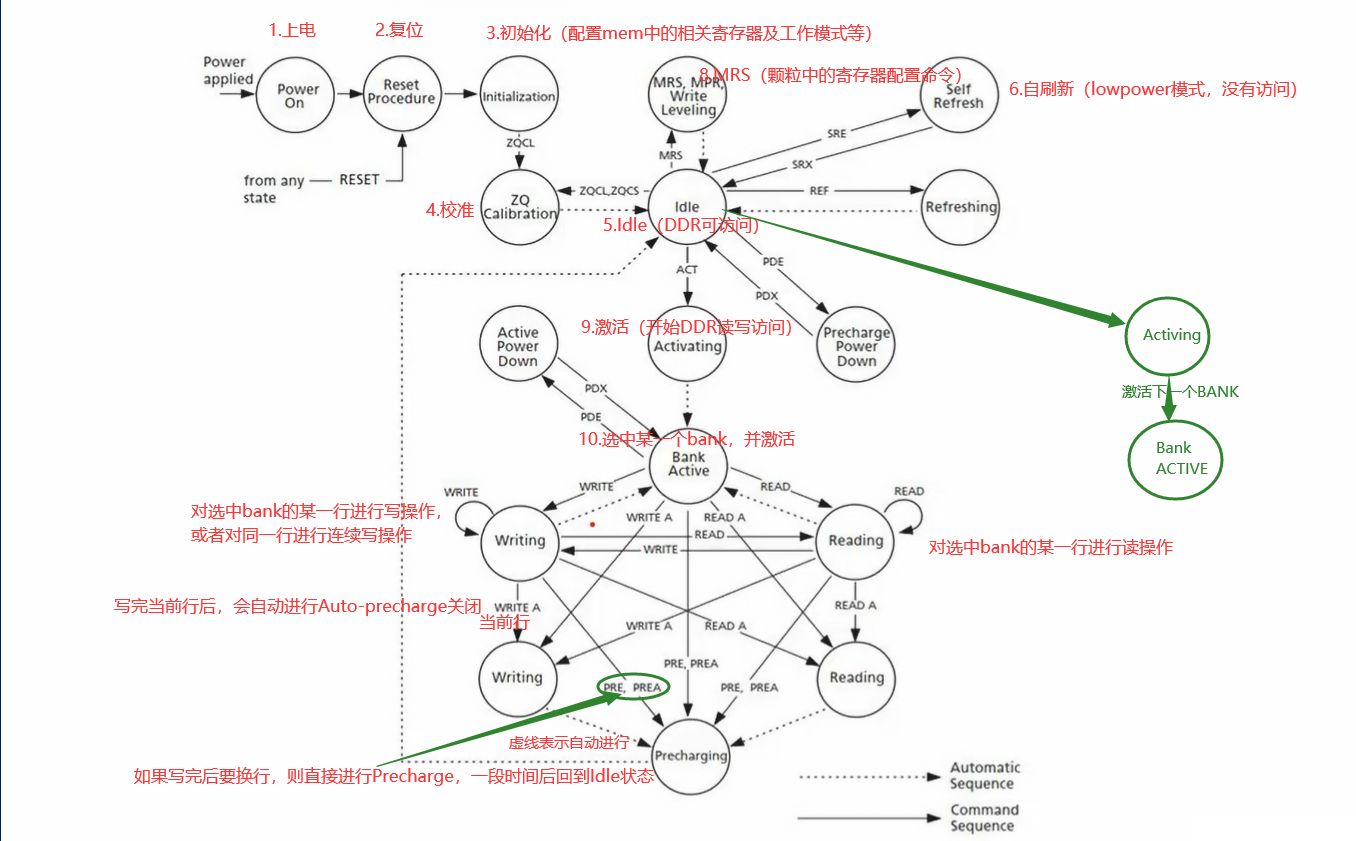

二、DDR状态转换流程

DDR的状态转换基本流程如下图所示,包括从“上电复位 —> 初始化 —>…—>数据读写访问”整个流程。(仅供学习参考)

在实际的DDR访问过程中,考虑到DDR的效率,一般并不会按照上图流程进行访问,而是会预先在DDR Controller中规划好Bank的访问流程,从而实现更为高效的DDR mem颗粒访问。

DDR状态转换过程中的刷新:

- DRAM之所以称为动态随机存取存储器,就是因为它要不断进行刷新(Refresh)才能保留住数据,因此它是DRAM最重要的操作。

- DDR的刷新操作分为两种:自动刷新(Auto Refresh,简称ASR)与自刷新(Self Refresh,简称SR)。

对于ASR, SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者 说CAS在RAS之前有效。所以,ASR又称CBR(CAS Before RAS,列提前于行定位)式刷新。由于刷新涉及到所有L-Bank,因此在刷新过程中,所有L-Bank都停止工 作,而每次刷新所占用的时间为9个时钟周期(PC133标准),之后就可进入正常的工作状态,也就是说在这9个时钟期间内,所有工作指令只能等待而无法执行。 一段时间之后则再次对同一行进行刷新,如此周而复始进行循环刷新。显然,刷新操作肯定会对SDRAM的性能造成影响,但这是没办法的事情,也是DRAM相对于 SRAM(静态内存,无需刷新仍能保留数据)取得成本优势的同时所付出的代价。 SR则主要用于休眠模式低功耗状态下的数据保存,这方面最著名的应用就是STR(Suspend to RAM,休眠挂起于内存)。在发出AR命令时,将CKE置于无效 状态,就进入了SR模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新 指令),只有重新使CKE有效才能退出自刷新模式并进入正常操作状态。

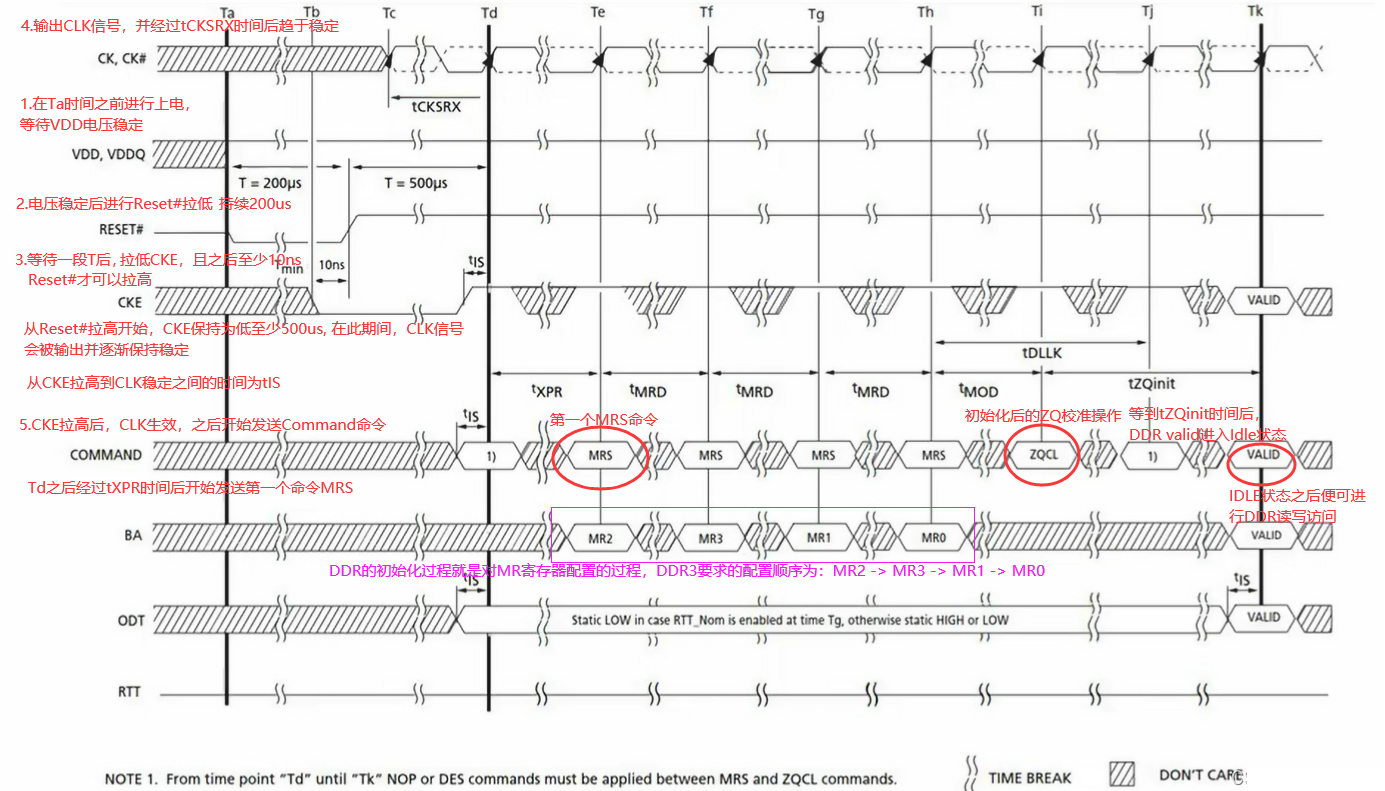

三、DDR的初始化

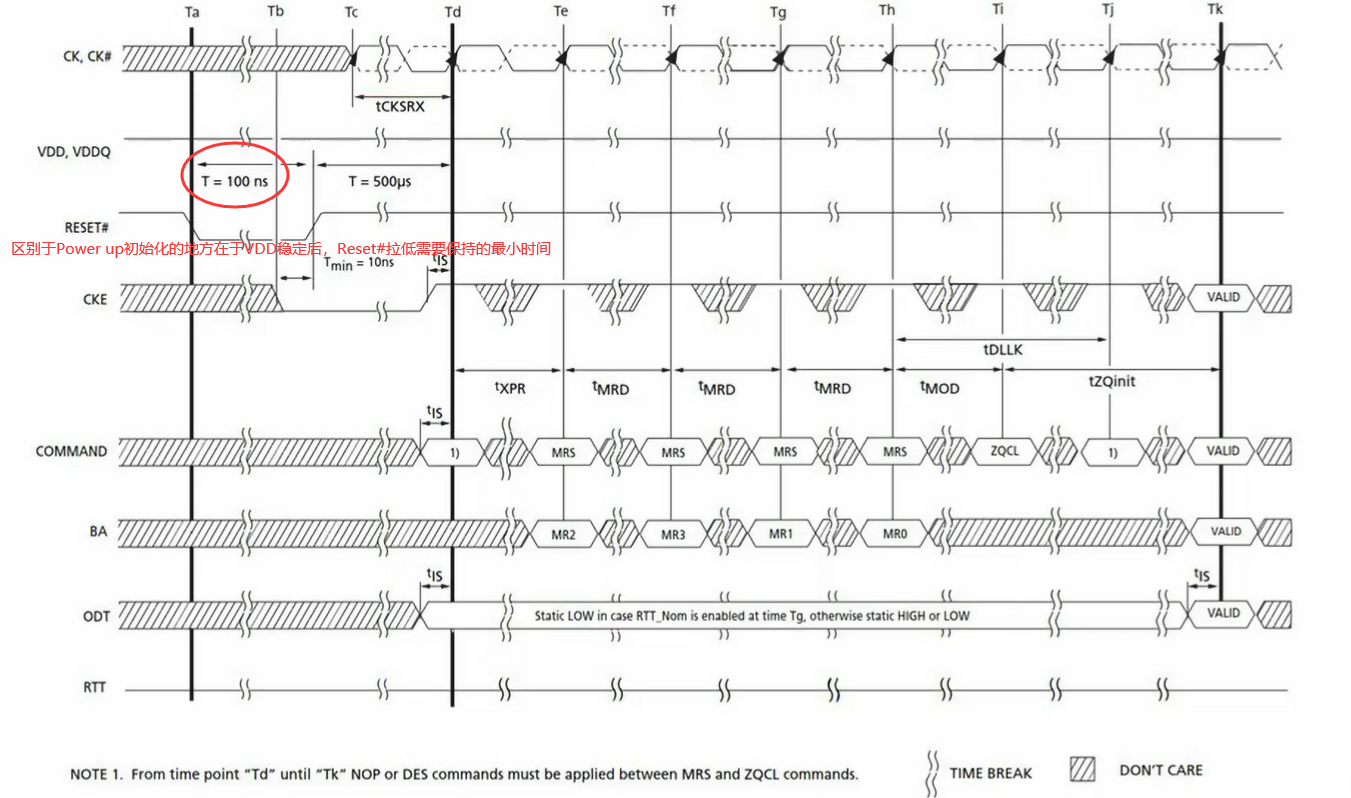

DDR的初始化分为上电Power up初始化和复位Reset初始化两种,二者过程基本相同。不同之处在于:电压VDD稳定后,Reset#信号拉低所持续的时间,DDR3要求上电初始化过程的Reset#至少持续200us,而复位初始化要求Reset#至少持续100us。

实际上真正的DDR初始化过程就是对MR寄存器按照特定顺序进行配置的过程,DDR3要求MR寄存器的配置顺序为:MR2 -> MR3 -> MR1 -> MR0。

3.1、Power up initialization

- tXPR: DDR上电复位后,从CKE拉高到发出第一个有效的命令MRS之间的最小时间间隔;

- tMRD:DDR初始化过程中,两个连续的MRS命令之间持续的最小时间间隔;

- tMOD:MRS命令发送完毕后,让所有寄存器生效需要等待的时间;

- ZQCL:上电初始化之后,对DDR内部的ODT打开进行信号校准操作,属于长延时的操作;

- tZQinit:等待ZQCL校准完成的时间,至少需要512个clock;

- tDLLK:在MR0配置时,同时需要使能DLL,让颗粒中的DLL开始工作,而使能DLL至少需要保持的时间即为tDLLK.

3.2、Reset initialization

复位初始化可以在任意状态执行,之后可以继续进行状态跳转。需要说明的是,复位初始化并不会改变mem颗粒的中的数据内容,而只是改变和初始化相关的寄存器值,但这并不代表复位完后寄存器的值和原来一样,这是由于复位需求的时间较长,可能由于没有及时刷新而导致原来的寄存器值被丢弃。所以复位完后依然需要进行正常的状态跳转,而不能认为复位后原来的寄存器中的值任然被保存。

四、MR寄存器

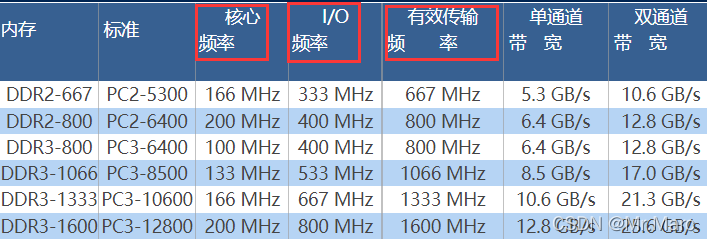

DDR3 SDRAM共有4个模式寄存器,分别为:MR2、MR3、MR1、MR0。

上述的Mode Register不存在default value,因此在DDR初始化过程中必须对MR寄存器进行配置,其每一bit都有其特定的作用。这些MR寄存器除了在DDR初始化过程中进行配置,在正常访问过程中也可以通过进入DDR的Idle状态进行配置,见第二部分DDR的状态图。

DDR中的MR寄存器的配置不会影响到Mem颗粒中的数据内容,但有可能会影响时序导致DDR mem读写数据不一致。。

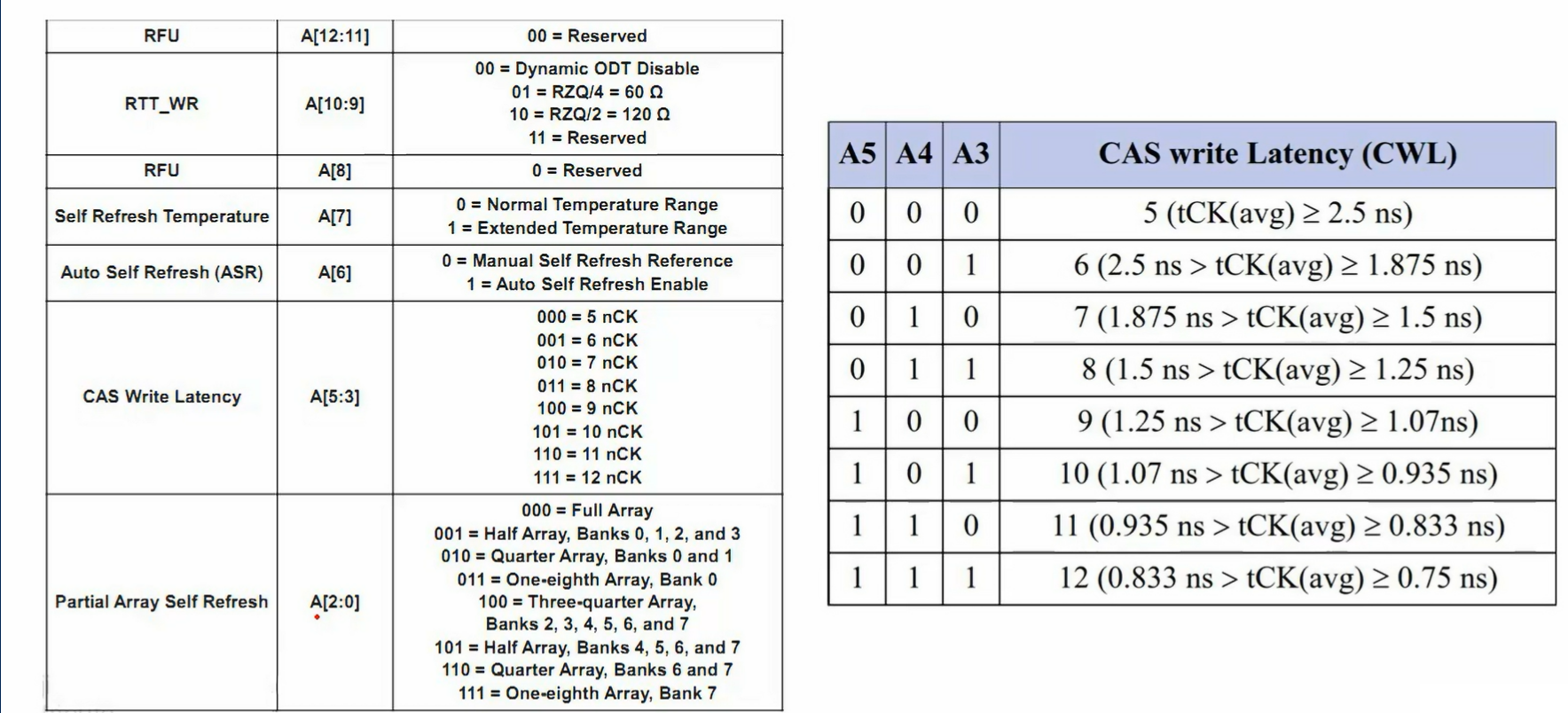

- MR2用来存储控制更新的特性, Rtt_WR阻抗,和CAS写长度。

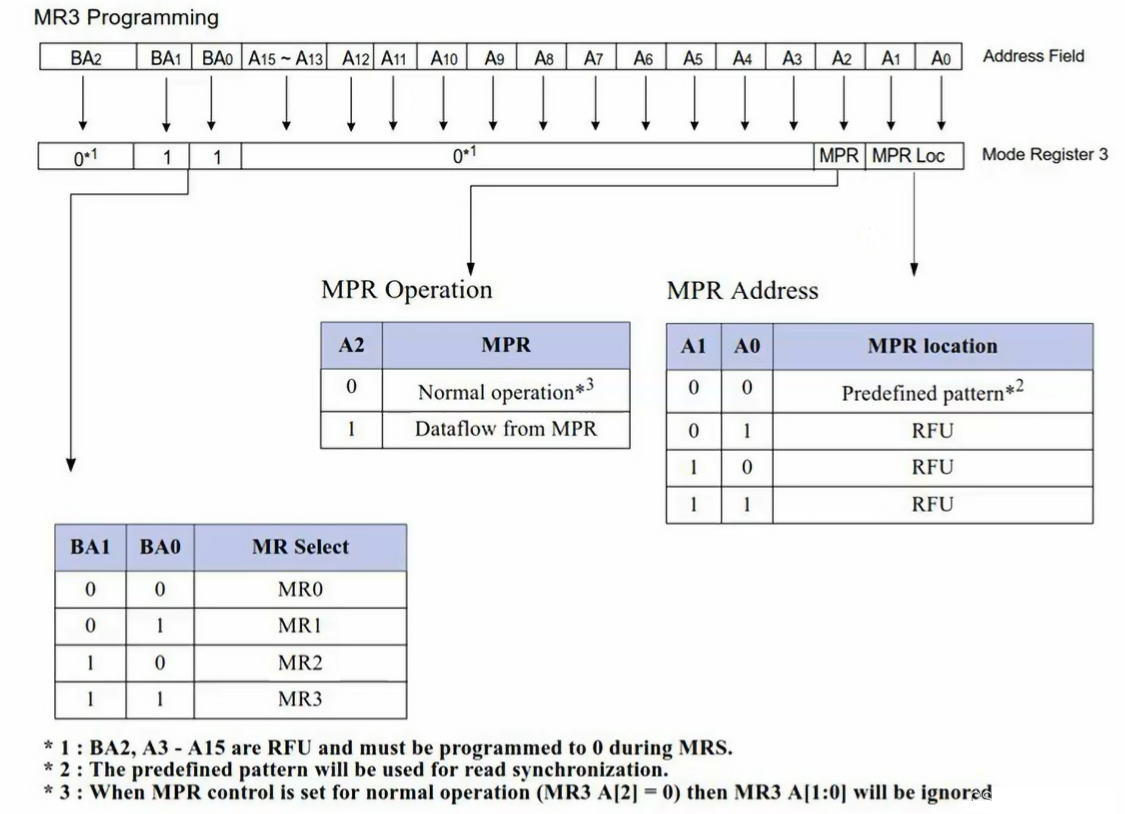

- MR3用来控制MPR。

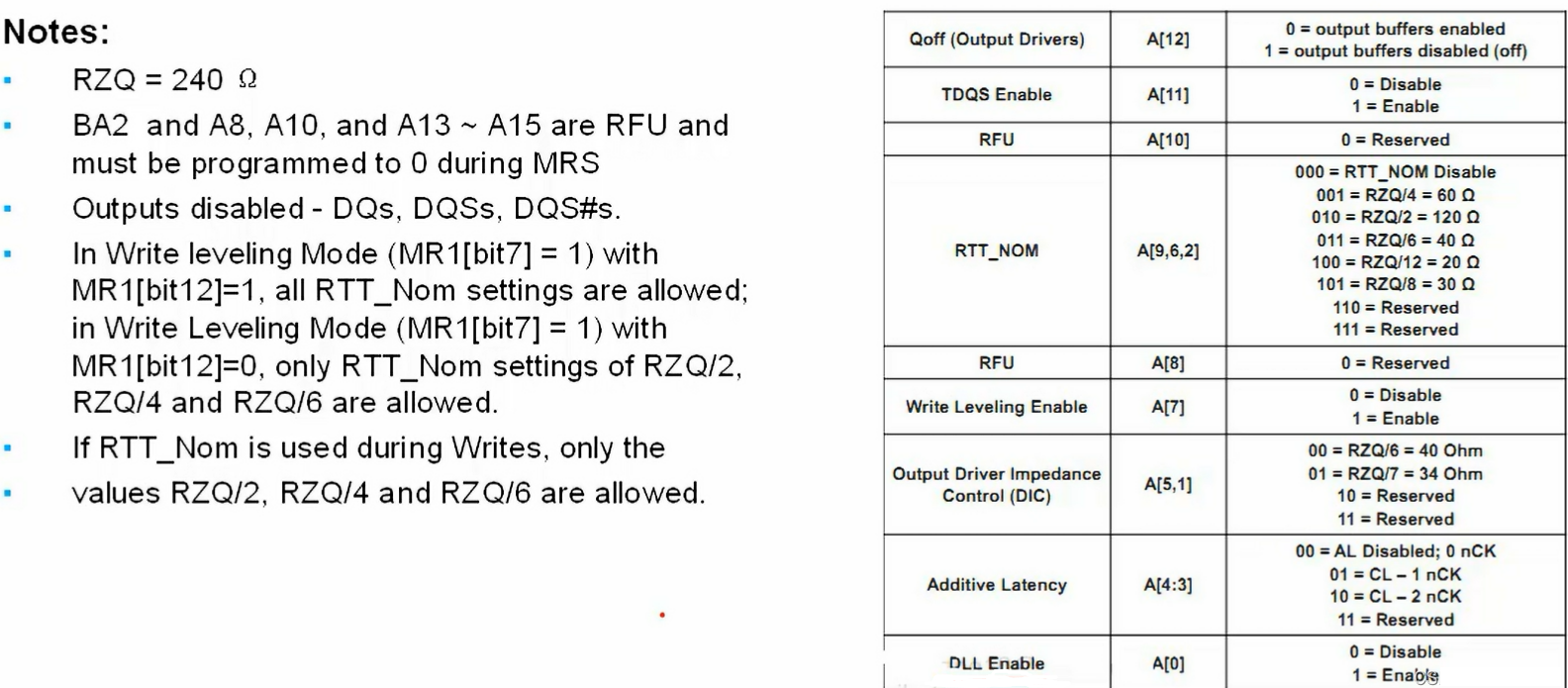

- MR1用来存储是否使能DLL、输出驱动长度、Rtt_Nom、额外长度、写电平使能等。

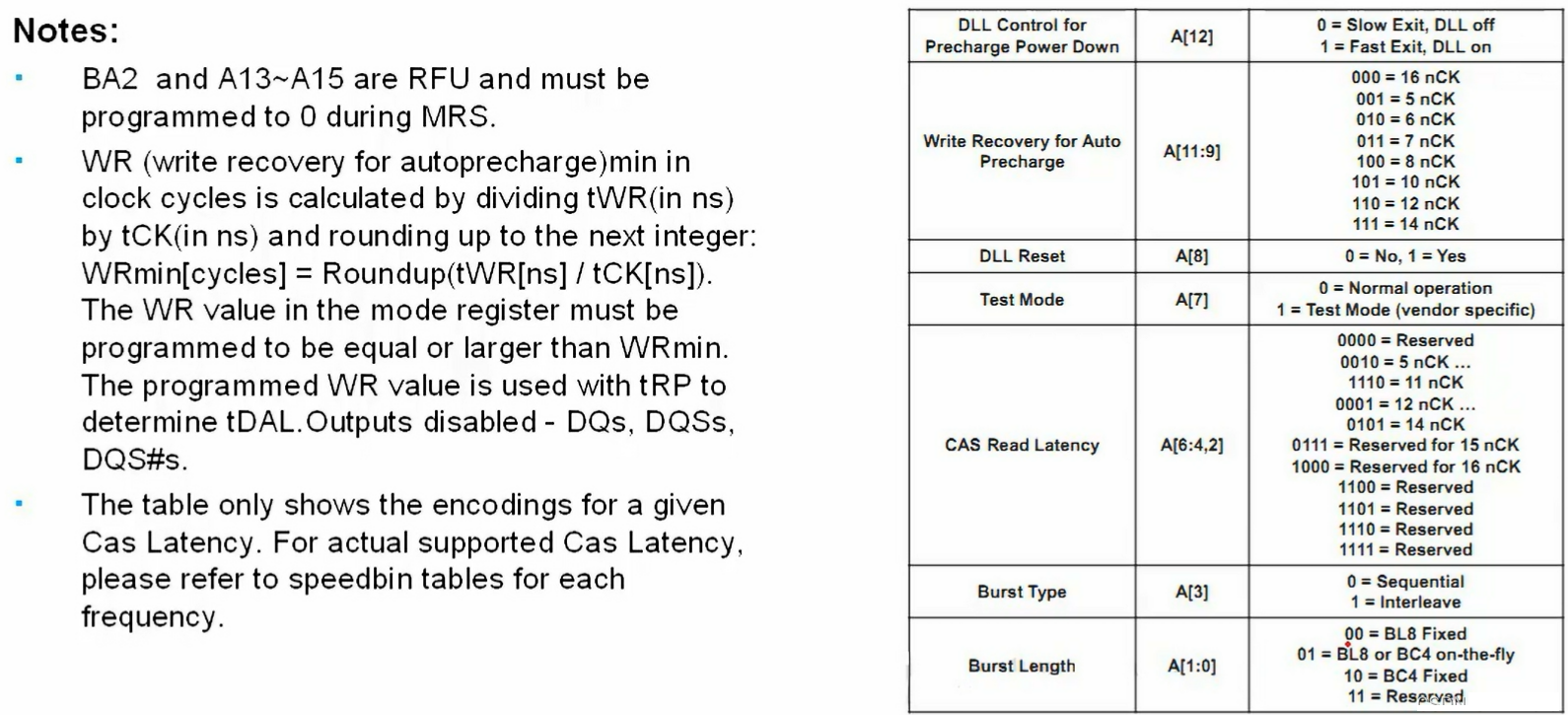

- MR0用来存储DDR3的不同操作模式的数据:包括突发长度、读取突发种类、CAS长度、测试模式、DLL复位等。

4.1、MR2/MR3 definition

MR2寄存器信息如下表:(不同厂商提供的DDR MR寄存器表格信息有所不同)

- A[2:0]:Partial Array Self Refresh,有目的的选择某一个或者某几个Bank进行自刷新self Refresh,该bit位信号一般直接刷新所有的Bank;

- A[5:3]:CAS Write Latency(CWL), 指从发起写命令到实际写数据进DDR颗粒之间延迟时间;

- A[6]:Auto Self Refresh,选择DDR的刷新模式,Self Refresh(SR) 和 Auto Self Refresh(ASR);

- A[7]:Self Refresh Temperature,选择自刷新的温度范围,与A[6]配合使用;

- A[8]:RFU,空白保留域;

- A[10:9]:RTT_WR,选择ODT的阻值,不常使用;

MR3寄存器信息如下图:

- A0-A15:寄存器地址信号;在配置MR寄存器时并不是通过DQ来实现而是通过地址来实现相应配置;

- BA0-BA1:Bank地址用来选择具体配置哪一个MR寄存起,然后通过地址A0-A15来实现该寄存器具体配置;

- A0-A1:MPR地址,Multi-purpose register address. 多用途寄存器的地址;

- A2:MPR操作模式。MPR的功能是读出一个预先设定的系统时序校准比特序列;当打开MPR模式时,在读取颗粒中的数据时,数据将会从MPR地址处读出预设的pattern而非来自mem阵列。

4.2、MR1/MR0 definition

MR1寄存器信息如下图:

- A[0]:DLL Enable,颗粒中存在DLL,若让DDR实现高速访问,则需打开DLL,

- A[4:3]:Additive Latency (AL),命令真正传递到寄存器中存在的延迟时间;

- A[5,1]:Output Driver Impedance Control (DIC) , 输出驱动阻抗控制,用来调节I/O输出驱动能力;

- A[7]:Write Leveling Enable,控制写training的功能;

- A[9, 6, 2]:RTT_NOM,可认为是一个标准的ODT阻值,通常情况下都会用到此ODT,常用60Ω;

- A[11]:TDQS,通常Disable状态;与DM信号互斥,二者只能有一个起作用,

- A[12]:Qoff(Output Driver), 通常Enable状态,若disable掉则会变成纯输入模式,没有输出负载,一般只在测试时会用到;

MR0寄存器信息如下图:

- A[1:0]:Burst length,可以是固定长度8,固定长度4,也可是动态的切换长度8/4;

- A[3]:Burst Type,通常选择sequential类型;

- A[6:4, 2]:CAS Read Latency,指从发起读命令被颗粒接收到实际数据从DDR颗粒读出之间延迟时间;具体的选择需要根据不同频率来选择;

- A[7]:Test mode,厂商自测用,通常置0;

- A[8]:DLL Reset,初始化的最后一步,需要进行DLL Reset,一般配为1;

- A[11:9]:Write Recovery for Auto Precharge,写数据之后要进行Auto Precharge,而从发出Auto-precharge命令到真正完成precharge所需的时间需要通过该bit域进行配置;根据不同频率进行配置;

- A[12]:DLL Control for Precharge Power Down,选择Precharge Power Down的退出模式,通常选择Fast exit。

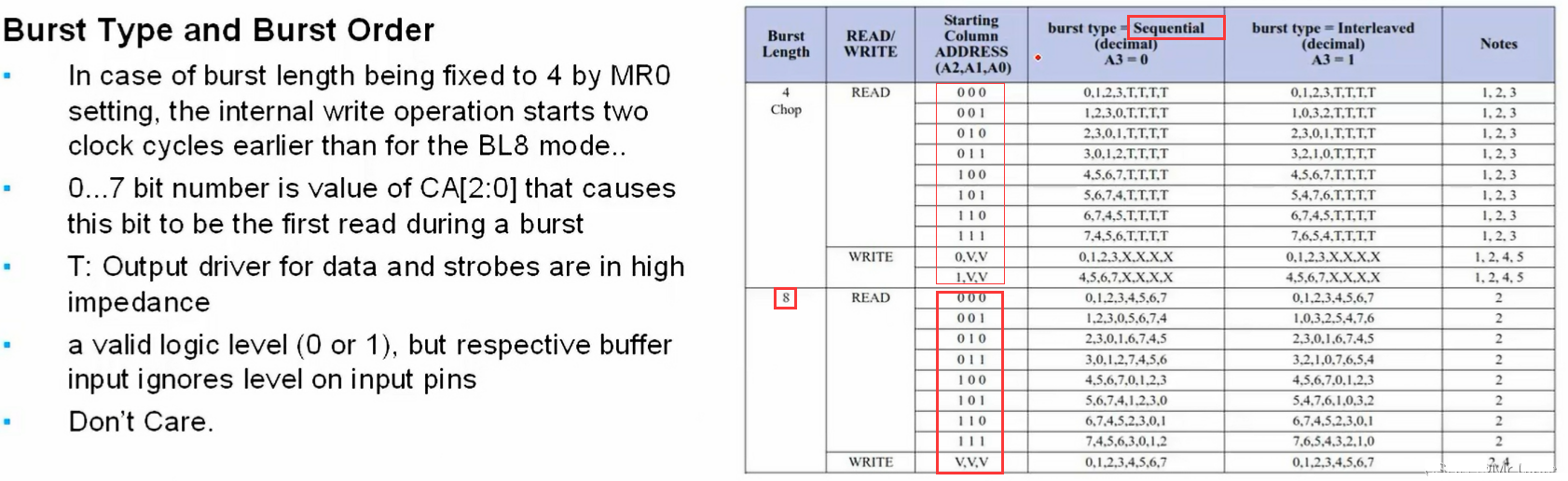

4.3、Burst类型及顺序

可以发现,Column Address的**A2,A1,A0三位被用于Burst Order功能,并且A3也被用于Burst Type功能**。由于一般情况,我们采用的都是顺序读写模式(即{A2,A1,A0}={0,0,0}),所以此时的A3的取值并无直接影响。

CA[2:0]的值决定了一次Burst sequence的读写地址顺序。

比如一次Burst Read的时候如果CA[2:0]=3’b001表示低三位从地址1开始读取,CA3=0的时候按顺序读取1,2,3,0,5,6,7,4,CA3=1的时候交错 读取1,0,3,2,5,4,7,6。 对于Prefetch而言,正好是8-bit Prefetch,对于Burst而言对应BL8。 BC4其实也是一次BL8的操作,只是丢弃了后一半的数据。

参考:https://www.expreview.com/168-5.html

参考:https://www.sohu.com/a/126626646_463982

参考:https://www.cnblogs.com/zhongguo135/p/8483346.html