摸鱼记录 Day_15 ~( ̄▽ ̄~)(~ ̄▽ ̄)~

review

前边已经学习了:

串口发送Vivado 串口通信(UART)------串口发送-CSDN博客

按键基于状态机的按键消抖实现-CSDN博客

1. 今日摸鱼任务

| 控制四个按键[3:0]key 按下按键后: 使用串口发送对应的拨码开关的值到电脑 发送完成后对应的led闪烁 |

2. design sources

| key_one 基于状态机的按键消抖实现-CSDN博客 |

| module key_one( endmodule |

| uart_txx Vivado 串口通信(UART)原理A ------串口发送实验-CSDN博客 |

| module uart_txx(input clk , |

| //以上两个函数对应之前的学习笔记 |

| 开始主函数哩: |

| key_main |

| module key_main( input clk , ); //四个按键 wire [3:0] key_flag; key_one key_0 key_1 key_2 key_3 //对应uart_tx wire [3:0] tx_data_; endmodule |

| 一开始的想法当然很简单啦~ |

| 第一个问题:uart_txx uart_tx_0(. clk(clk) , . reset_n(reset_n), . data(data) ,

用key_flag[0] 作为串口发送使能信号,key_flag[0] 在按键按下、释放都会产生脉冲信号,故在按键按下会发送两次信号 解决方法:if((key_flag[0])&&(key_state[0]==0)) Send_Go_[0] <= 1'b1 ; 添加使能信号 reg [3:0]Send_Go_ ; |

| 第二个问题:

[DRC MDRV-1] Multiple Driver Nets: Net uart_tx_3/tx_data_OBUF has multiple drivers: uart_tx_2/uart_tx__reg/Q, uart_tx_3/uart_tx__reg/Q, uart_tx_0/uart_tx__reg/Q, and uart_tx_1/uart_tx__reg/Q. uart_txx uart_tx_0(. clk(clk) , . reset_n(reset_n), . data(data) , 解决方法: wire [3:0] tx_data_; 并添加reg [3:0]Send_Go_flag ; 控制 tx_data此时的输出信号 |

| module key_main( input clk , wire [3:0] tx_data_; |

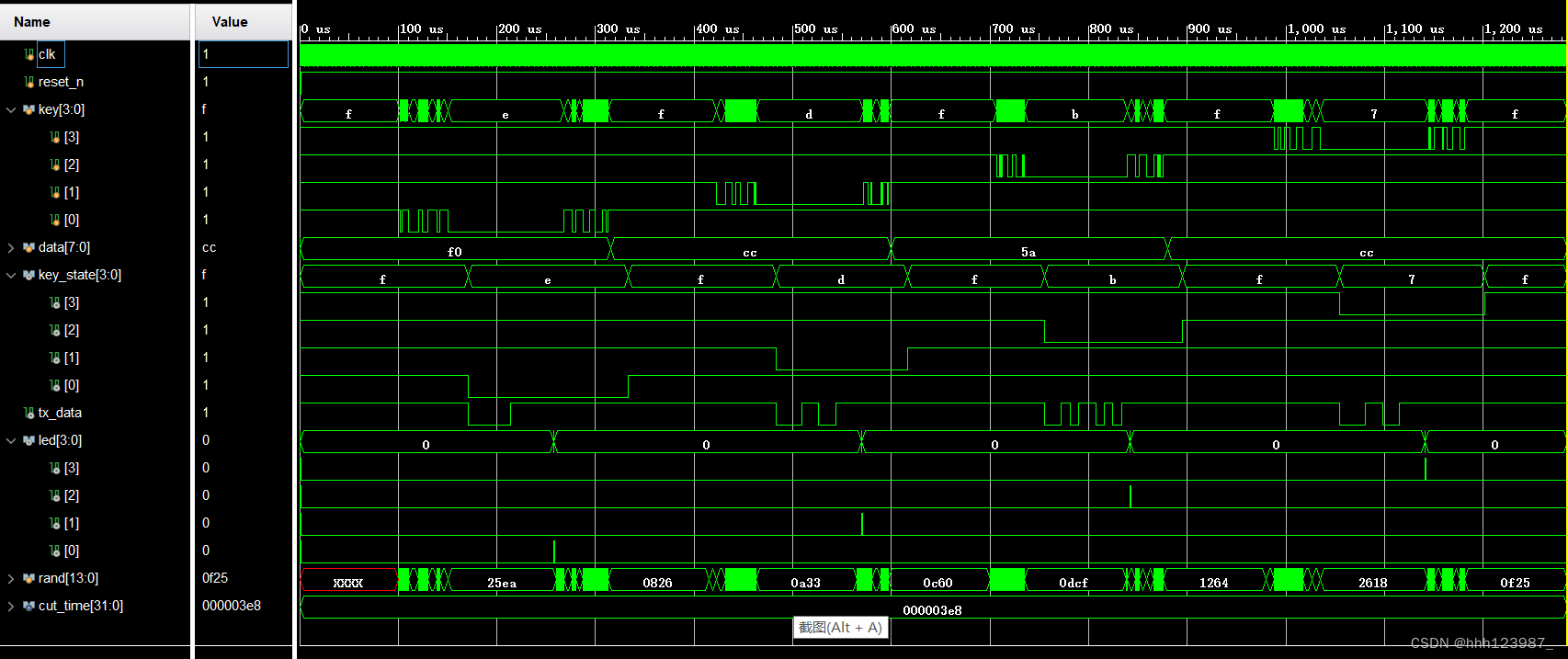

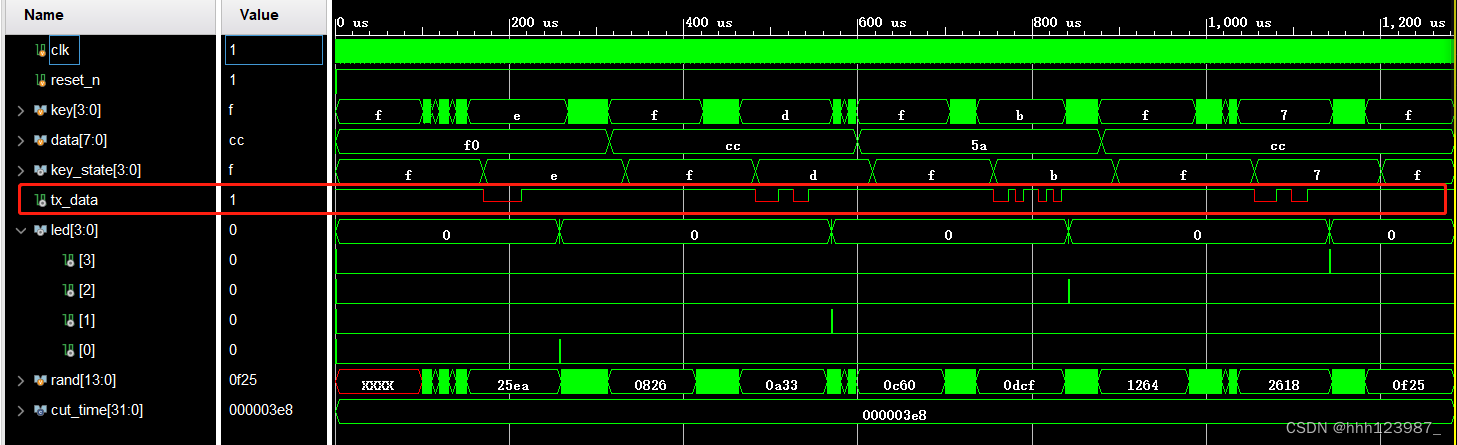

3. key_tb

| `timescale 1ns / 1ns module key_tb( ); reg clk , reset_n ; reg [3:0]key; reg [7:0]data; wire [3:0]key_state; wire tx_data; wire [3:0]led; parameter cut_time = 1000; key_main key_4( . clk(clk) , . reset_n(reset_n),. key(key),.data(data), . key_state(key_state), . tx_data(tx_data), .led(led) ); defparam key_4.cnt_num = cut_time; initial clk = 1; always#10 clk = ~clk ; initial begin reset_n = 0 ; key = 4'b1111; #201; reset_n = 1 ; key_press(2); $stop; end reg [13:0] rand; task key_press; input[3:0]seed; begin key = 4'b1111 ; data = 8'b1111_0000; #100000; // key[0] repeat(10) begin rand = {$random(seed)} % 10000; #rand; key[0]=~key[0]; end key = 4'b1110 ; #100000; repeat(10) begin rand = {$random(seed)} % 10000; #rand; key[0]=~key[0]; end key = 4'b1111 ; data = 8'b1100_1100; #100000; // key[1] repeat(10) begin rand = {$random(seed)} % 10000; #rand; key[1]=~key[1]; end key = 4'b1101 ; #100000; repeat(10) begin rand = {$random(seed)} % 10000; #rand; key[1]=~key[1]; end key = 4'b1111 ; data = 8'b0101_1010; #100000; // key[2] repeat(10) begin rand = {$random(seed)} % 10000; #rand; key[2]=~key[2]; end key = 4'b1011; #100000; repeat(10) begin rand = {$random(seed)} % 10000; #rand; key[2]=~key[2]; end key = 4'b1111 ; data = 8'b1100_1100; #100000; // key[3] repeat(10) begin rand = {$random(seed)} % 10000; #rand; key[3]=~key[3]; end key = 4'b0111 ; #100000; repeat(10) begin rand = {$random(seed)} % 10000; #rand; key[3]=~key[3]; end key = 4'b1111 ; data = 8'b1100_1100; #100000; end endtask endmodule |

|

4. constraint

| set_property IOSTANDARD LVCMOS33 [get_ports {data[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {data[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {data[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {data[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {data[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {data[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {data[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {data[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {key[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {key[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {key[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {key[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {key_state[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {key_state[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {key_state[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {key_state[0]}] set_property IOSTANDARD LVCMOS33 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports reset_n] set_property IOSTANDARD LVCMOS33 [get_ports tx_data] set_property PACKAGE_PIN U18 [get_ports clk] set_property PACKAGE_PIN H18 [get_ports reset_n] set_property PACKAGE_PIN J16 [get_ports tx_data] set_property PACKAGE_PIN E17 [get_ports {data[7]}] set_property PACKAGE_PIN D18 [get_ports {data[6]}] set_property PACKAGE_PIN H15 [get_ports {data[5]}] set_property PACKAGE_PIN F16 [get_ports {data[4]}] set_property PACKAGE_PIN K14 [get_ports {data[0]}] set_property PACKAGE_PIN L15 [get_ports {data[1]}] set_property PACKAGE_PIN G14 [get_ports {data[2]}] set_property PACKAGE_PIN J14 [get_ports {data[3]}] set_property PACKAGE_PIN J19 [get_ports {key[3]}] set_property PACKAGE_PIN J20 [get_ports {key[2]}] set_property PACKAGE_PIN H16 [get_ports {key[1]}] set_property PACKAGE_PIN H20 [get_ports {key[0]}] set_property PACKAGE_PIN G17 [get_ports {led[0]}] set_property PACKAGE_PIN G19 [get_ports {led[1]}] set_property PACKAGE_PIN G20 [get_ports {led[2]}] set_property PACKAGE_PIN G18 [get_ports {led[3]}] set_property PACKAGE_PIN K19 [get_ports {key_state[0]}] set_property PACKAGE_PIN J18 [get_ports {key_state[1]}] set_property PACKAGE_PIN H17 [get_ports {key_state[2]}] set_property PACKAGE_PIN K18 [get_ports {key_state[3]}] |

//视频没办法插入,就这样子啦~

//好啦,摸鱼结束啦~( ̄▽ ̄~)(~ ̄▽ ̄)~

![[vscode]将命令行参数传递给调试目标](https://img-blog.csdnimg.cn/direct/1949876c1cb74d81b41dd1df671864d7.png)