介绍

AMD Vivado™合成支持可以合成的SystemVerilog RTL的子集。这个以下部分介绍了这些数据类型。

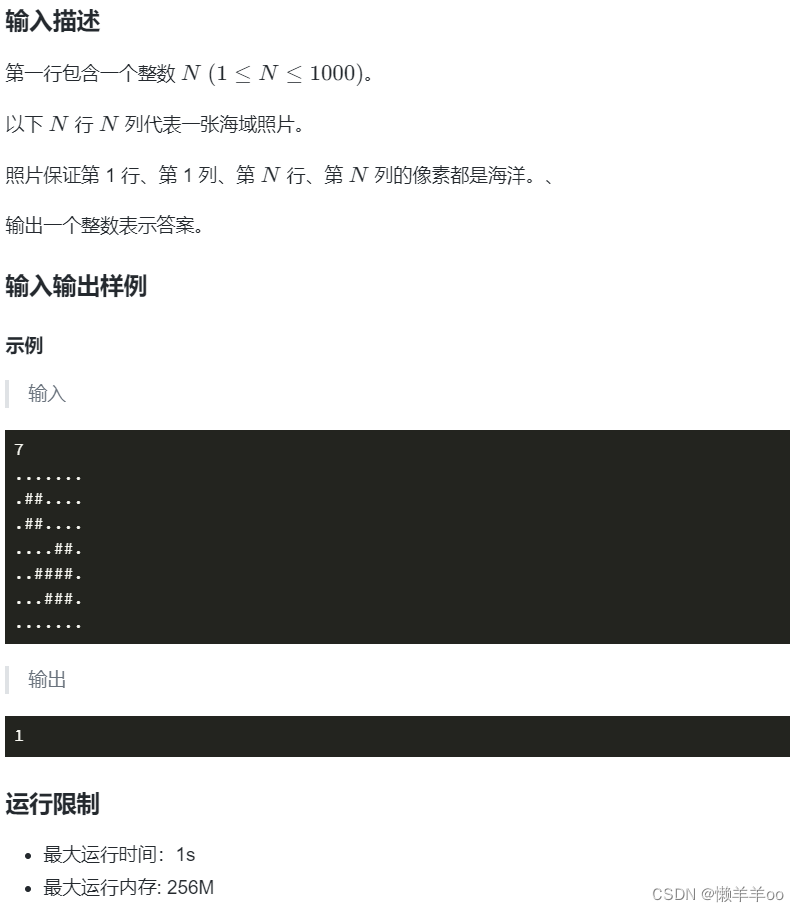

针对特定文件的SystemVerilog

默认情况下,Vivado合成工具使用Verilog 2005语法编译*.v文件和*.sv文件使用SystemVerilog语法。要在Vivado IDE中将SystemVerilog作为特定*.v文件的目标,请右键单击该文件,然后选择源节点属性。在“源文件属性”窗口中,将“文件类型”更改为SystemVerilog,然后单击“确定”。

设置属性的Tcl命令

或者,您可以在Tcl控制台中使用以下Tcl命令:

set_property file_type SystemVerilog[get_files<filename>.v]

以下部分介绍Vivado IDE中支持的SystemVerilog类型。

编制单位

System Verilog通过使用compilation支持单文件和多文件编译单位。

编译单元是一起编译的一个或多个SV源文件的集合。每一个编译单元和单个库相关联。编译单元范围是一个对于全局编译单元来说,作用域是本地的,它具有位于任何其他编译单元之外的所有声明设计范围。通常是函数、任务、参数、网络、变量和用户定义的类型在编译单元下的模块、接口、包或程序外部声明范围

例如,考虑以下设计。

在Tcl模式中

read_verilog-lib lib1{test1.sv}

read_verilog-lib lib2{test2.sv}

read_verilog test3.sv

或

集成电路设备

在前面的例子中,如果test1.sv在编译单元范围中有声明,例如params,typedefs等等,比如

并如前所述读取文件。编译器单元范围从读取文件test1.sv开始在lib1下,但是在使用lib2读取test2.sv时是非法的,因为编译单元应该与单个库相关联。这可以通过以下方式解决:

在Tcl模式下,将所有文件放在一个库中。

数据类型

支持以下数据类型以及控制它们的机制。

公告

按如下方式声明RTL中的变量:

[var][DataType]名称;

哪里

•var是可选的,如果不在声明中,则是隐含的。

•DataType是以下类型之一:

○ integer_vector_type:bit、logic或reg

○ integer_tom_type:byte、shortint、int、longint、integer或time

○ non_integer_type:shortreal、real或realtime

○ 结构

○ 枚举

整数数据类型

SystemVerilog支持以下整数类型:

•shortint:双状态16位有符号整数

•int:2状态32位有符号整数

•长度:2状态64位有符号整数

•字节:2态8位有符号整数

•位:2状态,用户定义的矢量大小

•逻辑:4状态用户定义的矢量大小

•reg:4状态用户定义的矢量大小

•整数:四态32位有符号整数

•时间:四态64位无符号整数

4态和2态是指可以分配给这些类型的值,如下所示:

•2状态允许0和1。

•4状态还允许X和Z状态。

X和Z态不能总是合成的;因此,2状态和4状态的项目是以相同的方式合成。

小心!使用4状态变量时要小心;RTL与模拟的不匹配可能发生。

•类型byte、shortint、int、integer和longint默认为带符号值。

•类型bit、reg和logic默认为无符号值。

有关Verilog的更多信息,请参阅Vivado Design Suite用户指南:逻辑仿真(UG900)模拟格式。

实数

合成支持实数;但是,它们不能用于创建逻辑。它们只能是用作参数值。SystemVerilog支持的真实类型有:

•真实

•短期

•实时

无效数据类型

只有没有返回值的函数才支持void数据类型。