文章目录

目录

概要

整体架构流程

技术名词解释

技术细节

为什么需要FIFO?

小结

概要

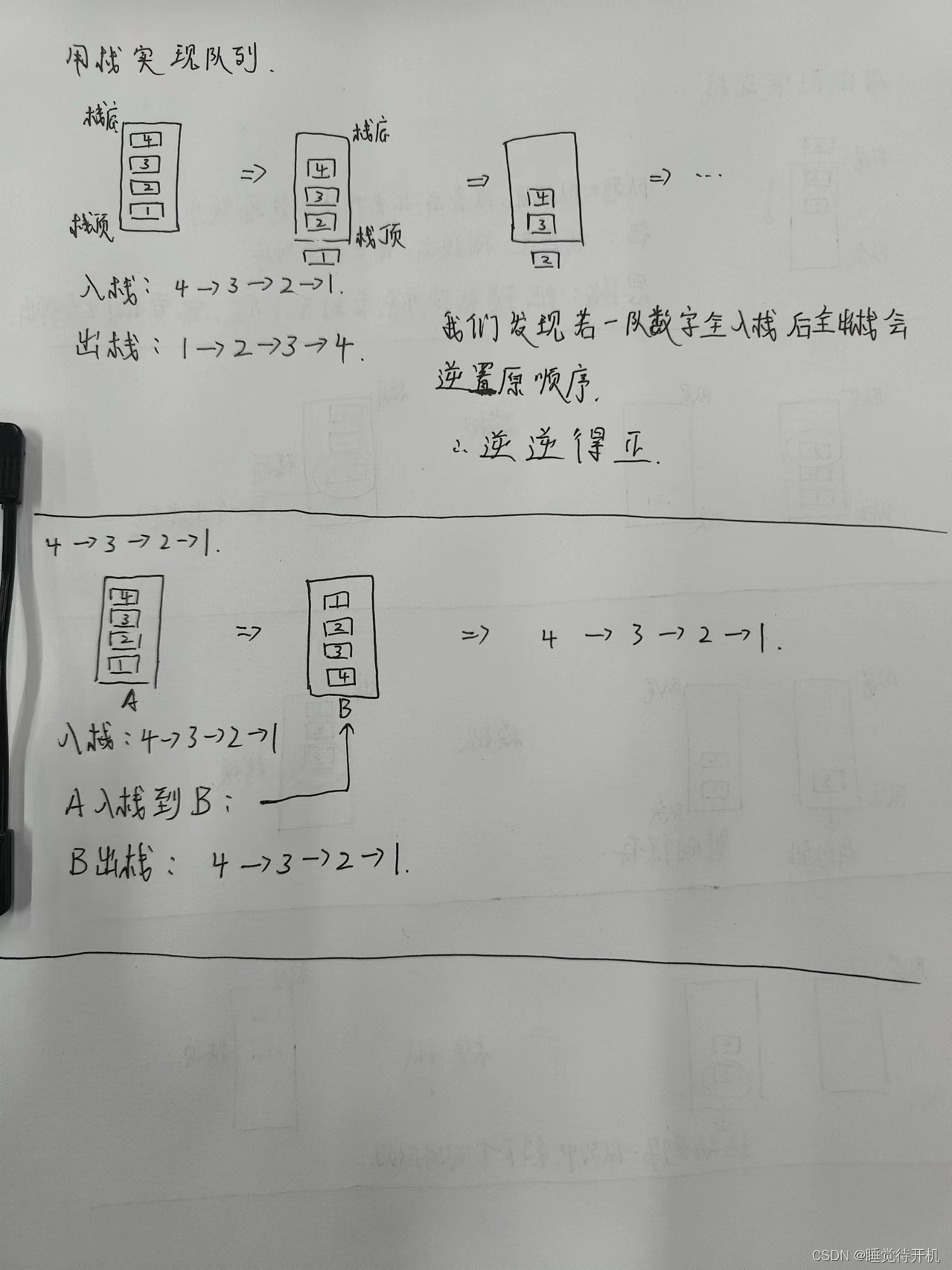

FIFO,全称为First-In, First-Out,意为先进先出。它就像是一个排队买东西的队伍,第一个进入队伍的人会第一个离开队伍。在芯片中,FIFO是一种数据缓冲区,能够按照先后顺序存储和输出数据,保证了数据的顺序性。

在芯片设计领域,从主要的应用场景和分类上可以将FIFO划分为同步FIFO和异步FIFO。同步FIFO即读写均在同一个时钟下进行,而异步FIFO的读写时钟为异步时钟。无论是同步还是异步FIFO,其基本原理都是数据的读写和管理。当数据输入时,它们被存储在FIFO的缓冲区中。当需要输出数据时,FIFO按照先进先出的原则,将最早进入的数据首先输出。这种按序处理的方式使得FIFO在各种应用中都具有重要作用,比如缓存数据、传输数据等。

FIFO在数字电路设计中广泛应用,例如在通信、图像处理、存储器和各类接口中都扮演着重要角色。在通信领域,FIFO用于调整不同速率的数据传输,确保数据不丢失且按序传送。在图像处理中,它能够临时存储图像数据,以便后续处理。同时,FIFO也在存储器控制中发挥作用,平衡不同速度的读写操作。在多核处理器、嵌入式系统等领域,FIFO也被广泛应用,提供了高效的数据传输和处理机制。

整体架构流程

除了基本工作原理外,FIFO设计还需考虑各种因素,包括数据宽度、深度、时钟域交叉、数据同步等。在设计FIFO时,需要平衡各种因素,以确保其稳定性、性能和适应性。此外,针对不同的应用场景,FIFO的设计和优化也会有所差异。

而在芯片验证领域也存在FIFO,毕竟先入先出就可以叫FIFO,也不是芯片设计的专属。UVM验证方法学中使用uvm_analysis_fifo作为传递数据对象(transactions)的数据结构。当然了这个并不是这个专栏要谈论的内容,就是同属芯片领域所以提一嘴。

技术名词解释

读写时钟:根据FIFO工作的时钟域分为同步/异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟在时钟沿来临时同时发生读写。异步FIFO读写时钟不一致,读写相互独立。

读写控制:读写控制的使能

满信号:FIFO里面的信号数量达到了最大深度值

空信号:FIFO里面的信号全部被读出

读写指针:总是指向下一个地址

深度:FIFO所能容纳的最大信号数量

技术细节

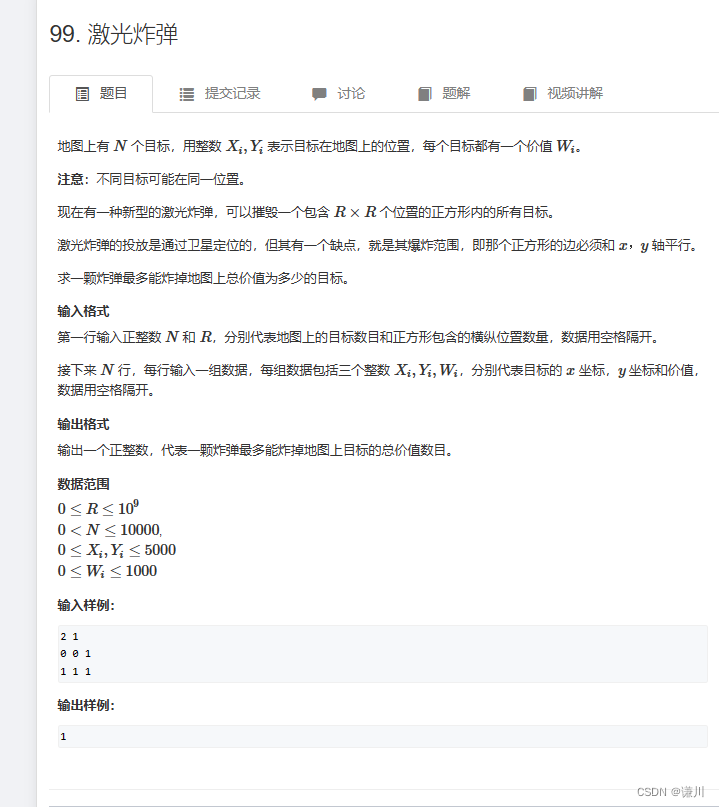

为什么需要FIFO?

FIFO存储器是系统的缓冲环节,如果没有FIFO存储器,整个系统就不可能正常工作。

FIFO的功能可以概括为

(1)对连续的数据流进行缓存,防止在进机和存储操作时丢失数据;

(2)数据集中起来进行进机和存储,可避免频繁的总线操作,减轻CPU的负担;

(3)允许系统进行DMA操作,提高数据的传输速度。这是至关重要的一点,如果不采用DMA操作,数据传输将达不到传输要求,而且大大增加CPU的负担,无法同时完成数据的存储工作。

小结

其实FIFO理解起来很简单,就像一个水池,如果写通道打开了,就代表我们在加水,如果读通道打开了就代表我们在放水,假如不间断的加水和放水,如果加水速度比放水速度快,那FIFO 就会有满的时候,如果满了还继续加水就会溢出overflow 如果放水速度比加水速度快 ,那么 FIFO就会有空的时候