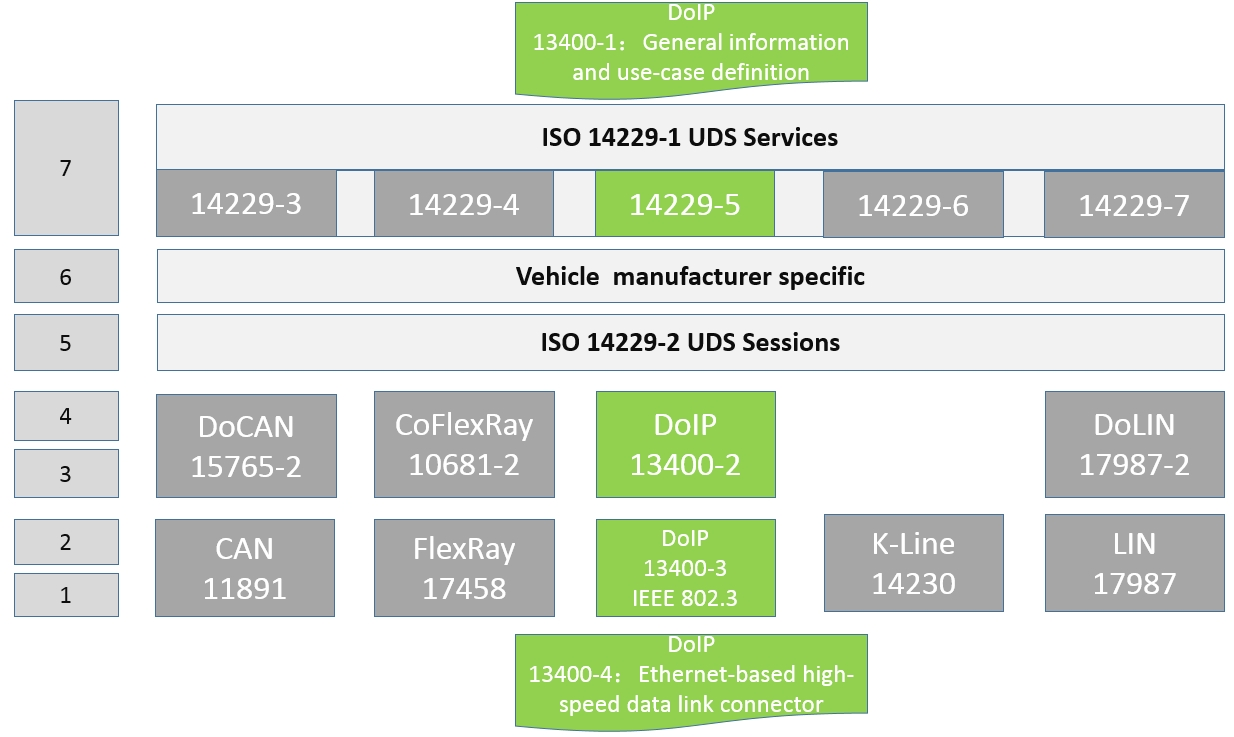

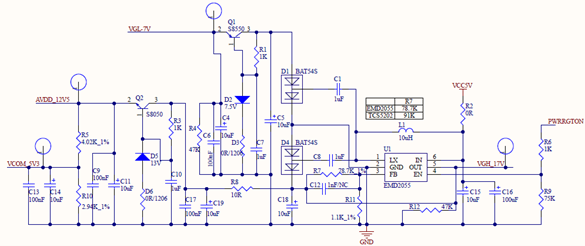

一 框图

二 代码修改

module Display

#(

parameter H_DISP = 1280,

parameter V_DISP = 1024,

parameter H_lcd = 12'd150,

parameter V_lcd = 12'd150,

parameter LCD_SIZE = 15'd10_000

)

(

input wire clk,

input wire rst_n,

input wire [11:0] lcd_xpos, //lcd horizontal coordinate

input wire [11:0] lcd_ypos, //lcd vertical coordinate

output wire [23:0] lcd_data //lcd data

);

wire [23:0] pic_data;

wire lcd_valid;

reg [14:0] rom_addra;

reg [23:0] data_lcd;

assign lcd_data = (lcd_valid == 1'b1) ? pic_data : data_lcd;

assign lcd_valid = ((lcd_xpos >=(((H_DISP-H_lcd)/2))))

&&((lcd_xpos >=(((H_DISP-H_lcd)/2)+H_lcd)))

&&((lcd_ypos >=(((V_DISP-V_lcd)/2))))

&&((lcd_ypos >=(((V_DISP-V_lcd)/2)+V_lcd)));

always@(posedge clk or negedge rst_n)

if(rst_n==1'b0)

rom_addra <= 15'd0;

else if(rom_addra == LCD_SIZE - 1'b1)

rom_addra <= 15'd0;

else if(lcd_valid == 1'b1)

rom_addra <= rom_addra+1'b1;

`ifdef VGA_HORIZONTAL_COLOR

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

lcd_data <= 24'h0;

else

begin

if (lcd_ypos >= 0 && lcd_ypos < (V_DISP/8)*1)

data_lcd <= `RED;

else if(lcd_ypos >= (V_DISP/8)*1 && lcd_ypos < (V_DISP/8)*2)

data_lcd <= `GREEN;

else if(lcd_ypos >= (V_DISP/8)*2 && lcd_ypos < (V_DISP/8)*3)

data_lcd <= `BLUE;

else if(lcd_ypos >= (V_DISP/8)*3 && lcd_ypos < (V_DISP/8)*4)

data_lcd <= `WHITE;

else if(lcd_ypos >= (V_DISP/8)*4 && lcd_ypos < (V_DISP/8)*5)

data_lcd <= `BLACK;

else if(lcd_ypos >= (V_DISP/8)*5 && lcd_ypos < (V_DISP/8)*6)

data_lcd <= `YELLOW;

else if(lcd_ypos >= (V_DISP/8)*6 && lcd_ypos < (V_DISP/8)*7)

data_lcd <= `CYAN;

else

data_lcd <= `ROYAL;

end

end

`endif

`ifdef VGA_VERTICAL_COLOR

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

lcd_data <= 24'h0;

else

begin

if (lcd_xpos >= 0 && lcd_xpos < (H_DISP/8)*1)

data_lcd <= `RED;

else if(lcd_xpos >= (H_DISP/8)*1 && lcd_xpos < (H_DISP/8)*2)

data_lcd <= `GREEN;

else if(lcd_xpos >= (H_DISP/8)*2 && lcd_xpos < (H_DISP/8)*3)

data_lcd <= `BLUE;

else if(lcd_xpos >= (H_DISP/8)*3 && lcd_xpos < (H_DISP/8)*4)

data_lcd <= `WHITE;

else if(lcd_xpos >= (H_DISP/8)*4 && lcd_xpos < (H_DISP/8)*5)

data_lcd <= `BLACK;

else if(lcd_xpos >= (H_DISP/8)*5 && lcd_xpos < (H_DISP/8)*6)

data_lcd <= `YELLOW;

else if(lcd_xpos >= (H_DISP/8)*6 && lcd_xpos < (H_DISP/8)*7)

data_lcd <= `CYAN;

else

data_lcd <= `ROYAL;

end

end

`endif

`ifdef VGA_GRAFTAL_GRAPH

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

lcd_data <= 24'h0;

else

lcd_data <= lcd_xpos * lcd_ypos;

end

`endif

`ifdef VGA_GRAY_GRAPH

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

lcd_data <= 24'h0;

else

begin

if(lcd_ypos < V_DISP/2)

lcd_data <= {lcd_ypos[7:0], lcd_ypos[7:0], lcd_ypos[7:0]};

else

lcd_data <= {lcd_xpos[7:0], lcd_xpos[7:0], lcd_xpos[7:0]};

end

end

`endif

vga_Demo_ip vga_inst (

.addra(addra),

.clka(clk),

.doa(pic_data)

);

endmodule

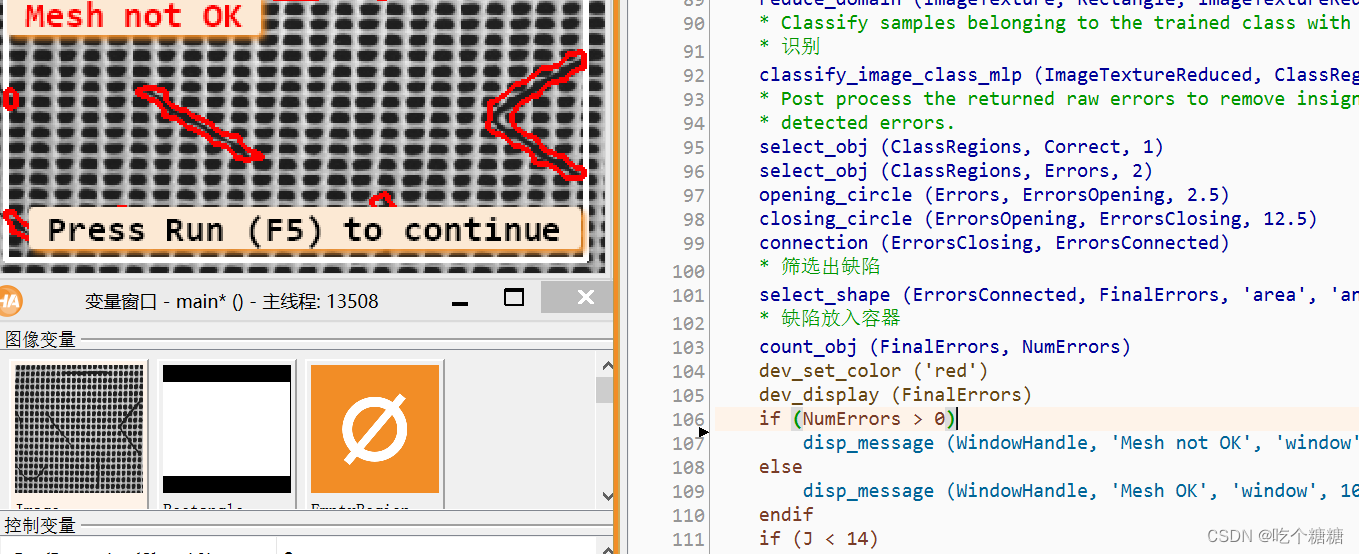

对工程中的数据生成模块进行了修改,例化了rom ip ,增添了逻辑语句,用于输出图像数据。

![[Python进阶] 识别验证码](https://img-blog.csdnimg.cn/direct/aa9549fafa054cf5ae4c747ea7abee38.png)