接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(8)

4.2 PCIe体系结构的组成部件

PCIe总线作为处理器系统的局部总线,其作用与PCI总线类似,主要目的是为了连接处理器系统中的外部设备,当然PCIe总线也可以连接其它处理器系统。在不同的处理器系统中,PCIe体系结构的实现方法略有不同。但是在大多数处理器系统中,都使用了RC、Switch和PCIe-to-PCI桥这些基本模块连接PCIe和PCI设备。在PCIe总线中,基于PCIe总线的设备,也被称为EP(Endpoint)。

4.2.1 基于PCIe架构的处理器系统

在不同的处理器系统中,PCIe体系结构的实现方式不尽相同。PCIe体系结构以Intel的x86处理器为蓝本实现,已被深深地烙下x86处理器的印记。在PCIe总线规范中,有许多内容是x86处理器独有的,也仅在x86处理器的Chipset中存在。在PCIe总线规范中,一些最新的功能也在Intel的Chipset中率先实现。本节将以一个虚拟的处理器系统A和PowerPC处理器为例简要介绍RC的实现,并简单归纳RC的通用实现机制。

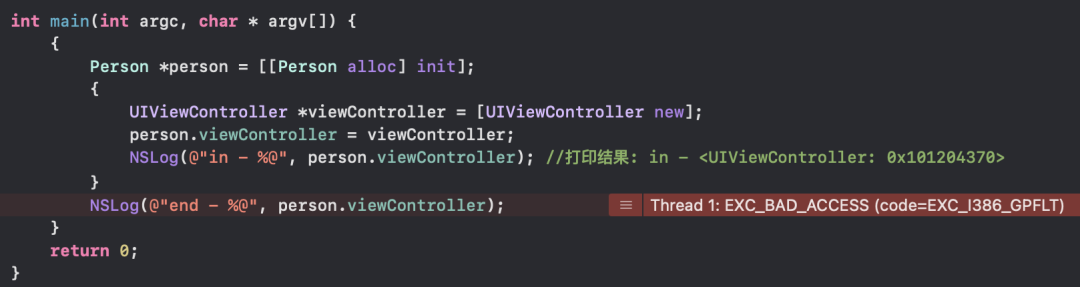

1. 处理器系统A

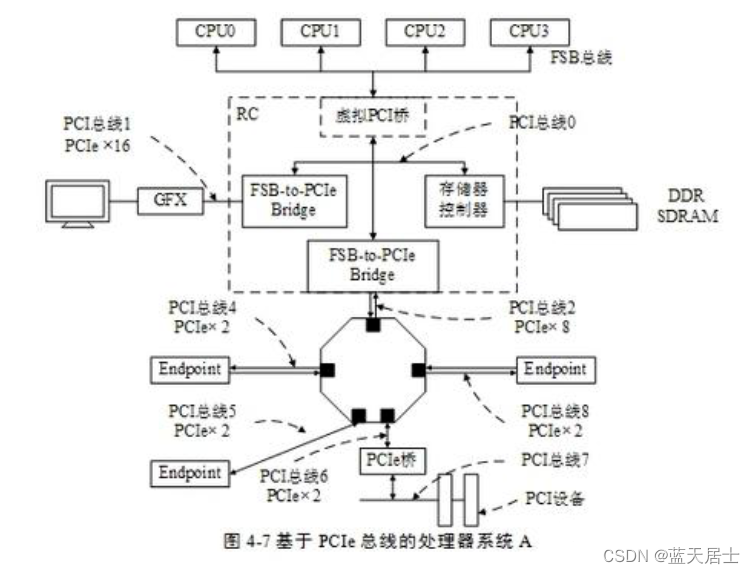

在有些处理器系统中,没有直接提供PCI总线,此时需要使用PCIe桥,将PCIe链路转换为PCI总线之后,才能连接PCI设备。在PCIe体系结构中,也存在PCI总线号的概念,其编号方式与PCI总线兼容。一个基于PCIe架构的处理器系统A如图4-7所示:

在上图的结构中,处理器系统首先使用一个虚拟的PCI桥分离处理器系统的存储器域与PCI总线域。FSB总线下的所有外部设备都属于PCI总线域。与这个虚拟PCI桥直接相连的总线为PCI总线0。这种架构与Intel的x86处理器系统较为类似。

在这种结构中,RC由两个FSB-to-PCIe桥和存储器控制器组成。值得注意的是在图4-7中,虚拟PCI桥的作用只是分离存储器域与PCI总线域,但是并不会改变信号的电气特性。RC与处理器通过FSB连接,而从电气特性上看,PCI总线0与FSB兼容,因此在PCI总线0上挂接的是FSB-to-PCIe桥,而不是PCI-to-PCIe桥。

在PCI总线0上有一个存储器控制器和两个FSB-to-PCIe桥。这两个FSB-to-PCIe桥分别推出一个×16和×8的PCIe链路,其中×16的PCIe链路连接显卡控制器(GFX),其编号为PCI总线1;×8的PCIe链路连接一个Switch进行PCIe链路扩展。而存储器控制器作为PCI总线0的一个Agent设备,连接DDR插槽或者颗粒。

此外在这个PCI总线上还可能连接了一些使用“PCI配置空间”管理的设备,这些设备的访问方法与PCI总线兼容,在x86处理器的Chipset中集成了一些内嵌的设备。这些内嵌的设备使用均使用“PCI配置空间”进行管理,包括存储器控制器。

PCIe总线使用端到端的连接方式,因此只有使用Switch才能对PCIe链路进行扩展,而每扩展一条PCIe链路将产生一个新的PCI总线号。如图4-7所示,Switch可以将1个×8的PCIe端口扩展为4个×2的PCIe端口,其中每一个PCIe端口都可以挂接EP。除此之外,PCIe总线还可以使用PCIe桥,将PCIe总线转换为PCI总线或者PCI-X总线,之后挂接PCI/PCI-X设备。多数x86处理器系统使用这种结构连接PCIe或者PCI设备。

采用此种结构有利于处理器系统对外部设备进行统一管理,因为所有外部设备都属于同一PCI总线域,系统软件可以使用PCI总线协议统一管理所有外部设备。然而,这种设备管理方法并非尽善尽美。使用这种结构时,需要注意存储器控制器使用的寄存器也被映射为PCI总线空间,从而属于PCI总线域,而主存储器(如DDR内存空间)仍然属于存储器域。因此在这种结构中,存储器域与PCI总线域的划分并不明晰。

在PCIe总线规范中并没有明确提及PCIe主桥,而使用RC概括除了处理器之外的所有与PCIe总线相关的内容。在PCIe体系结构中,RC是一个很模糊也很混乱的概念。Intel使用PCI总线的概念管理所有外部设备,包括与这些外部设备相关的寄存器,因此在RC中包含一些实际上与PCIe总线无关的寄存器。使用这种方式有利于系统软件使用相同的平台管理所有外部设备,也利于平台软件的一致性,但是仍有其不足之处。

PCIe总线在x86处理器中始终处于核心地位。Intel也借PCIe总线统一管理所有外部设备,并以此构建基于PCIe总线的PC生态系统(Ecosystem)。PCI/PCIe总线在x86处理器系统中的地位超乎想象,而且不仅限于硬件层面。

下一回重点讲解PowerPC处理器。