一、ISSP IP概要:

ISSP:In-System Sources & Probes Intel FPGA IP

作用:

- 分为In-System Sources与In-System Probes

- n-System Sources,输入端,等价于拨码开关,通过输入板载FPGA上的拨码开关状态改变FPGA内部功能

- In-System Probes,输出端,等价于LED灯仔,通常通过肉眼观察LED亮灭判断程序运行状态,如果没有设计板载LED邓状态,可以通过Quartus的In-System Probes读取

- 目前工程里用的最多的是Sources,即作为输入使用

- ISSP等价于没有实际IO pin引脚的FPGA的IO口

普通的IO口有具体的引脚输出,可以使用LED灯仔或者示波器抓取输入/输出信号,但是ISSP只能通过Quartus的软件在线查看;

二、创建ISSP IP

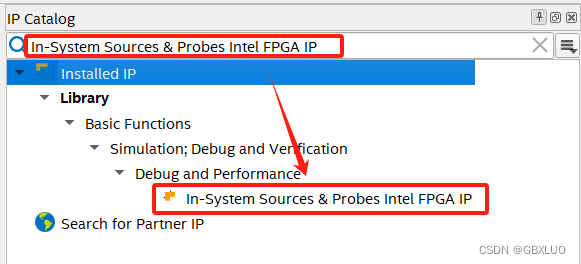

2.1 添加ISSP IP

在IP Catalog的搜索框输入:In-System Sources & Probes Intel FPGA IP并双击即可打开

2.2 设置IP路径与IP变体名称

2.3 设置IP-3步即可

- 先设置探针是8bit,

- 设置8bit输入源与初始值

- 勾选Use Source Clock,用来同步输入源数据与探针读取到的数据

2.4 点击Generate HDL

- 设置综合语言:Verilog或者VHDL,一般用Verilog

- 根据情况选择仿真模型:一般用Modelsim,但是ISSP设置很简单,不必仿真

三、使用方法

3.1 例化

在ISSP IP设置界面,选择Generate》Show Instantiation Template,在弹出的Instantiation Template中可以看到该issp_ip例化模板,点击Copy,并将其粘贴到Quartus工程的顶层/其他模块中即可。

3.2 编译工程生成可供下载的sof文件并下载

3.3 链接USB-Blaster并下载sof文件到FPGA芯片中

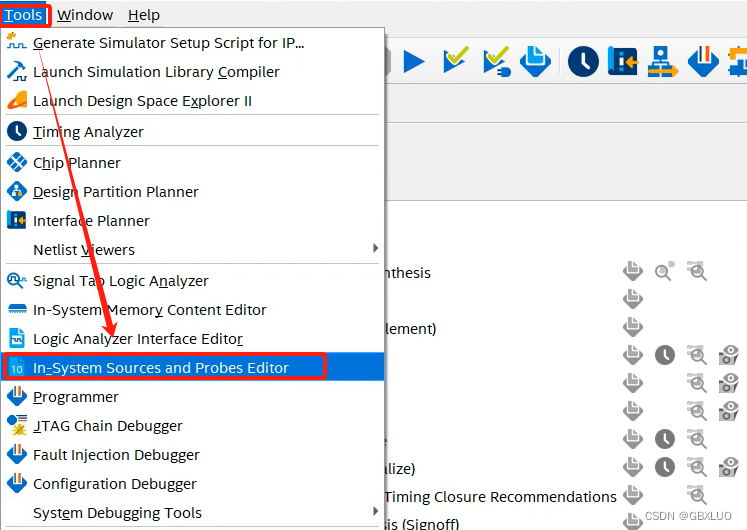

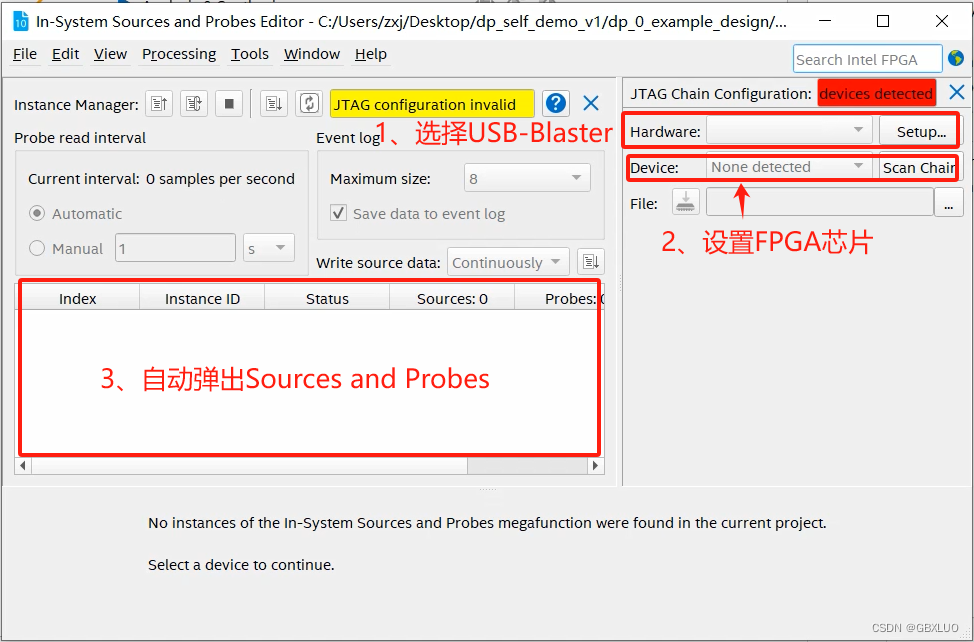

3.4 打开ISSP Editor与使用

在Quatus中,选择Tools》In-System Sources and Probes Editor

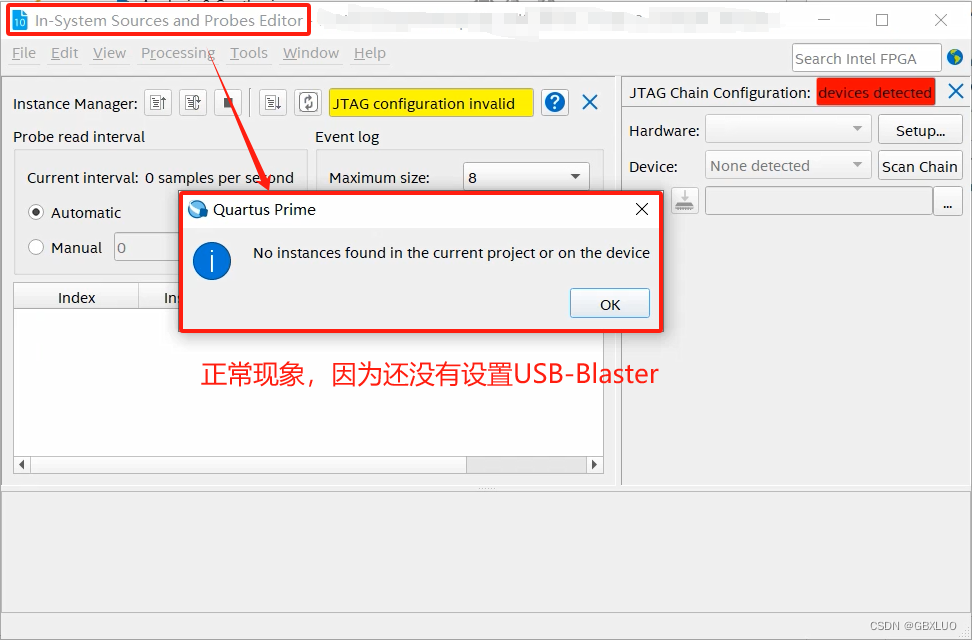

在弹出的In-System Sources and Probes Editor中点击OK关闭:No instance found in the current project or on the device。

因为还没有设置USB-Blaster,因此无法通过JTAG通信读取FPGA芯片中设置的ISSP内容

选择USB-Blaster与FPGA芯片(一般成功识别USB-Blaster后会自动读取FPGA芯片型号),并自动弹出FPGA芯片中下载的ISSP中的Sources与Probes信息。

具体的弹出Sources and Probes的界面,待后续有板子了再重新修订补充……

![XCTF:3-1[WriteUP]](https://img-blog.csdnimg.cn/direct/202ba1da85d74bd8badb47397bf73f62.png)