接前一篇文章:《PCI Express体系结构导读》随记 —— 第II篇 第4章 PCIe总线概述(4)

4.1.2 PCIe总线使用的信号

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。因为Vaux在多数情况下并不会被移除,因此当PCIe设备的Vcc恢复后,该设备不用重新恢复使用Vaux供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

PCIe链路的最大宽度为×32,但是在实际应用中,×32的链路宽度极少使用。在一个处理器系统中,一般提供×16的PCIe插槽,并使用PETp0~15、PETn0~15和PERp0~15、PERn0~15共64根信号线组成32对差分信号,其中16对PETxx信号用于发送链路,另外16对PERxx信号用于接收链路。除此之外PCIe总线还使用了下列辅助信号。

(1)PERST#信号

(2)REFCLK+和REFCLK-信号

(3)WAKE#信号

(4)SMCLK和SMDAT信号

(5)JTAG信号

JTAG(Joint Test Action Group)是一种国际标准测试协议,与IEEE 1149.1兼容,主要用于芯片内部测试。目前绝大多数器件都支持JTAG测试标准。JTAG信号由TRST#、TCK、TDI、TDO和TMS信号组成。其中TRST#为复位信号;TCK为时钟信号;TDI和TDO分别与数据输入和数据输出对应;而TMS信号为模式选择。

JTAG允许多个器件通过JTAG接口串联在一起,并形成一个JTAG链。目前FPGA和EPLD可以借用JTAG接口实现在线编程ISP(In-System Programming)功能。处理器也可以使用JTAG接口进行系统级调试工作,如设置断点、读取内部寄存器和存储器等一系列操作。除此之外JTAG接口也可用作“逆向工程”,分析一个产品的实现细节,因此在正式产品中,一般不保留JTAG接口。

(6)PRSNT1#和PRSNT2#信号

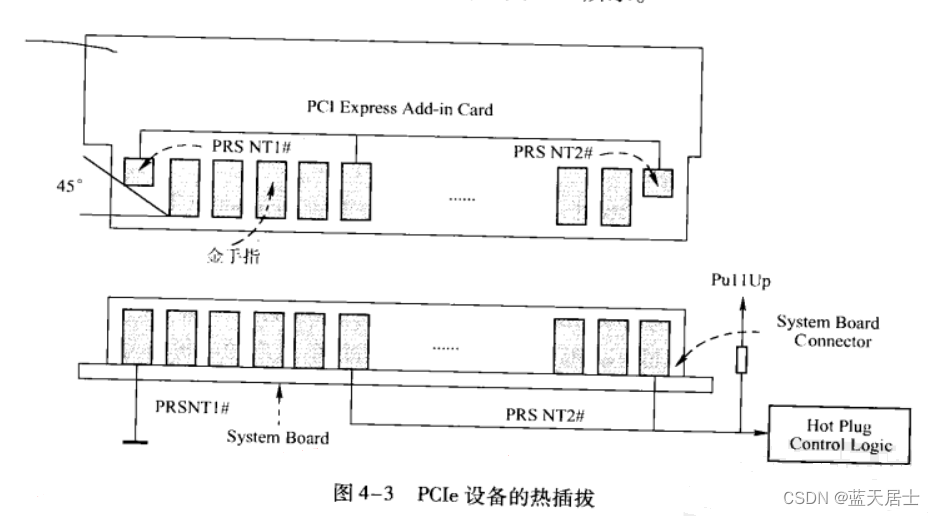

PRSNT1#和PRSNT2#信号与PCIe设备的热插拔相关。在基于PCIe总线的Add-in卡中,PRSNT1#和PRSNT2#信号直接相连;而在处理器主板中,PRSNT1#信号接地,而PRSNT2#信号通过上拉电阻接为高。PCIe设备的热插拔结构如图4-3所示:

- Add-In卡插入工作机制

Add-In卡未插入时,处理器主板的PRSNT2#信号由上拉电阻接为高;而当Add-In卡插入时,主板的PRSNT2#信号将与PRSNT1#信号通过Add-In卡连通,此时PRSNT2#信号为低。处理器主板的热插拔控制逻辑将捕获这个“低电平”,得知Add-In卡已经插入,从而触发系统软件进行相应地处理。

- Add-In卡拔出工作机制

Add-In卡拔出的工作机制与插入类似。Add-in卡连接在处理器主板时,处理器主板的PRSNT2#信号为低,当Add-In卡拔出后,处理器主板的PRSNT2#信号为高。处理器主板的热插拔控制逻辑将捕获这个“高电平”,得知Add-In卡已经被拔出,从而触发系统软件进行相应地处理。

不同的处理器系统处理PCIe设备热拔插的过程并不相同,在一个实际的处理器系统中,热拔插设备的实现也远比图4-3中的示例复杂得多。

值得注意的是,在实现热拔插功能时,Add-in Card(注意不是插槽)需要使用“长短针”结构。如图4-3所示,PRSNT1#和PRSNT2#信号使用的金手指长度是其他信号的一半。因此当PCIe设备插入插槽时,PRSNT1#和PRSNT2#信号在其它金手指与PCIe插槽完全接触,并经过一段延时后,才能与插槽完全接触;当PCIe设备从PCIe插槽中拔出时,这两个信号首先与PCIe插槽断连,再经过一段延时后,其他信号才能与插槽断连。系统软件可以使用这段延时,进行一些热拔插处理。有种“先天下之忧而忧,后天下之乐而乐”的意思。

更多内容请看下回。