不建Vivado工程,也能看Device视图

在FPGA设计与开发中,Device视图和Package视图发挥着重要的作用。

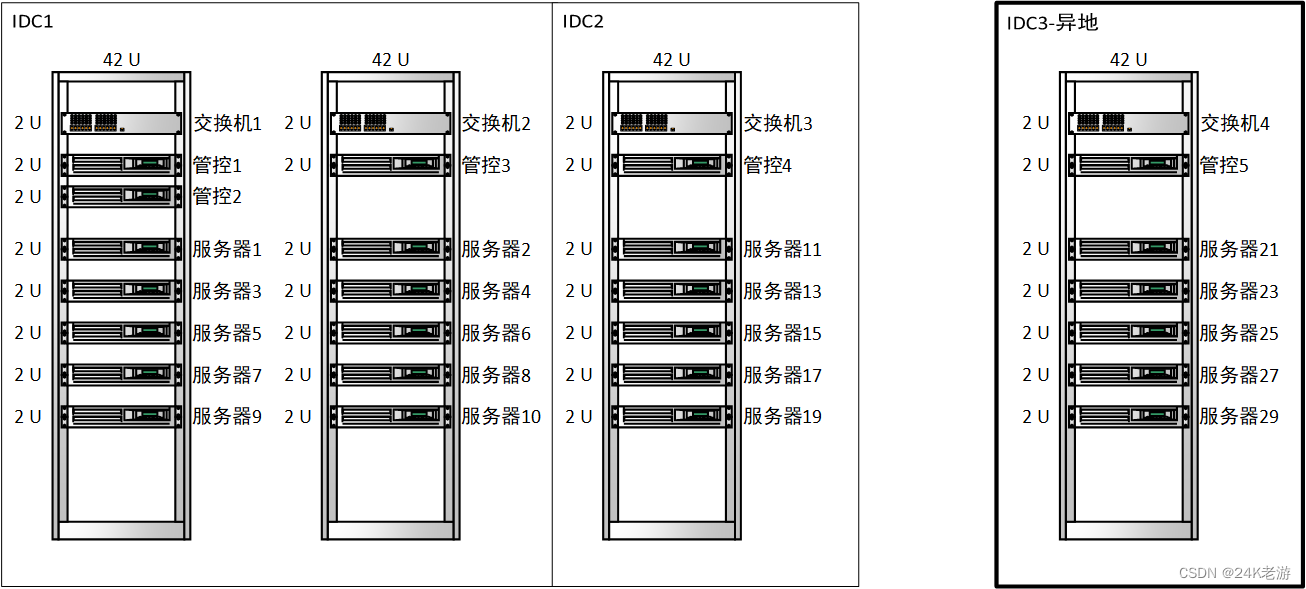

在Device视图下:

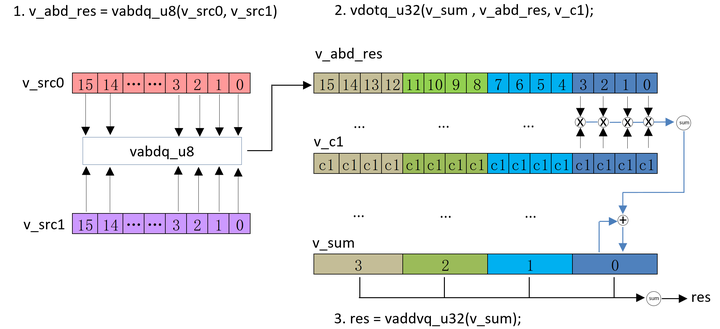

- 可以查看FPGA芯片可用资源

例如:LUT、FF、BRAM、DSP、URAM等的个数;

- 可以查看关键资源的分布情况

例如:PCIE的位置,高速收发器的位置,因为这些位置直接影响到PCB设计以及FPGA内部的数据流。

- 可用查看MMCM等时钟资源的位置

时钟的拓扑结构的质量直接影响到设计后期的时序收敛,在多die芯片中,这一点尤为重要。例如:某个芯片是3个die,设计中的一个时钟要给这3个die使用,那么最好将该时钟分配在中间那个die上,这样跨die次数最小,比较时钟跨die会增加Clock Skew。

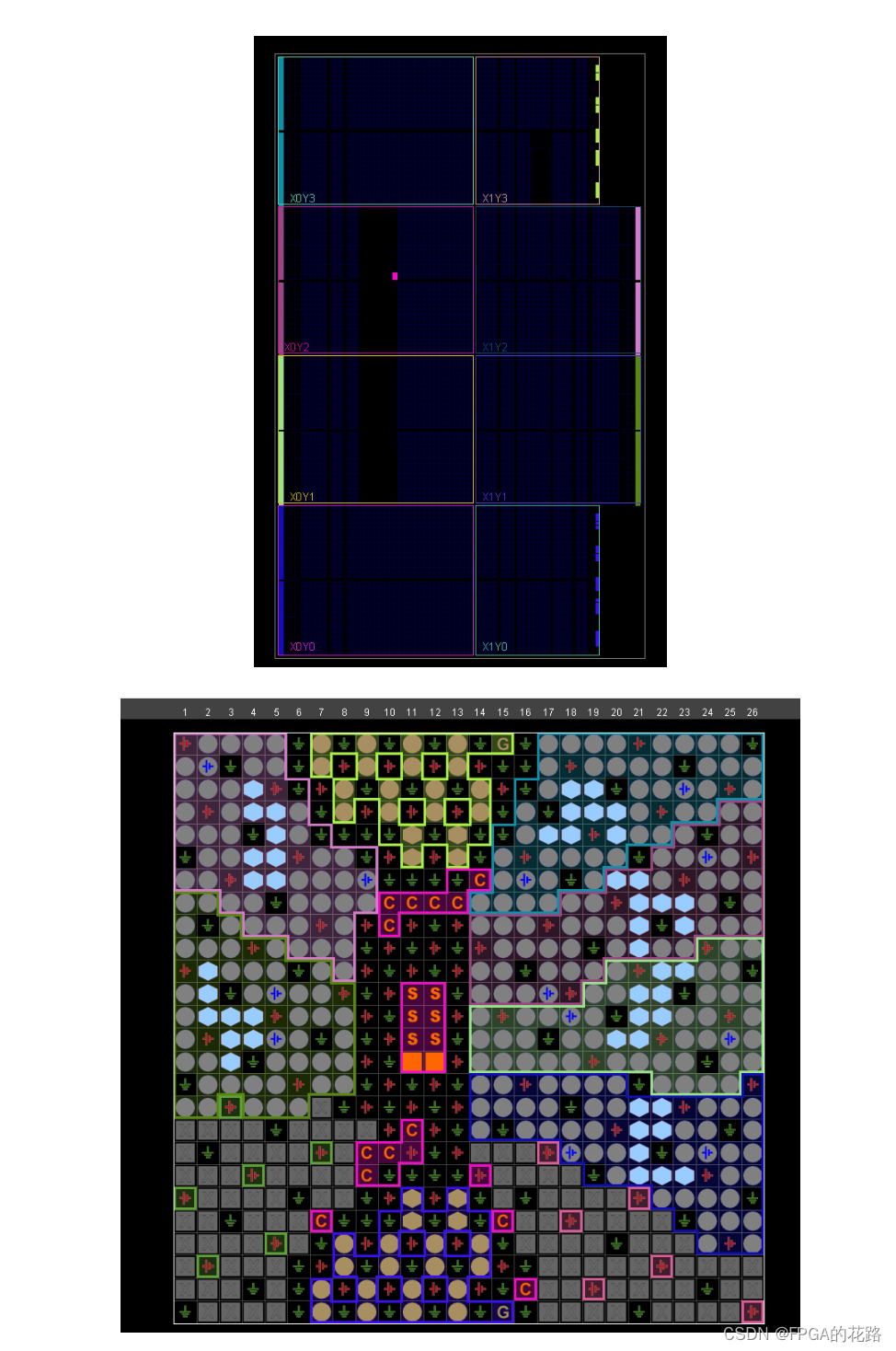

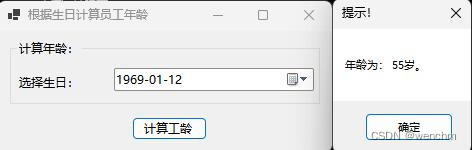

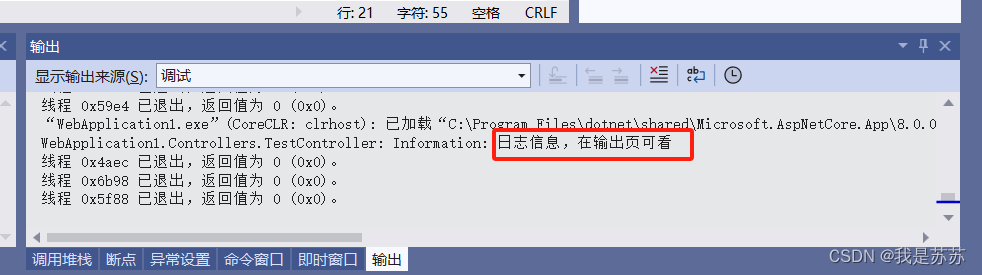

那么如何打开Device视图呢?一种可行的方法是创建Vivado I/O工程,但这仍然显得繁琐。这里我们介绍一种更为直接的方法,就是使用Tcl命令link_design。打开Vivado,在Tcl Console中直接输入如下图所示命令:

link_design -part xc7a100tfgg676-2

此时,该命令后只需跟随一个选项,即-part,-part用于指明具体的芯片型号。这样就打开了Vivado,之后选择Window,点击Device即可打开Device视图,点击Package即可打开Package视图。