使用软件: Vivado

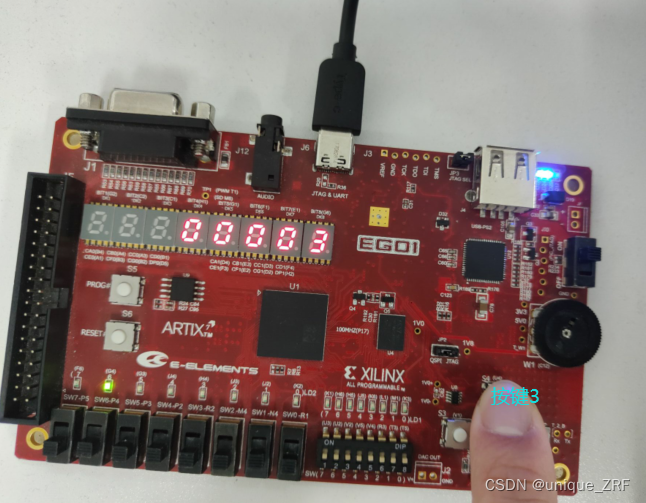

开发板: EGO1采用Xilinx Artix-7系列XC7A35T-1CSG324C FPGA

使用程序:按键案例

ILA详细使用方法

- 一、ILA简介

- 二、ILA的使用方法

- 方法1 — 使用IP核创建ILA调试环境

- 创建ILA IP核

- 方法二 — 使用 Debug 标记创建 ILA

- 对需观察信号进行标记

- 对工程进行保存后重新综合

- Debug信号和探针的关联

- 测试

- 方法三 — 使用路径标记和Set up debug 菜单创建 ILA 调试环境

- ILA调试及板级验证

- 烧录程序

- 基本操作

- 其他设置

- 总结

- 其他

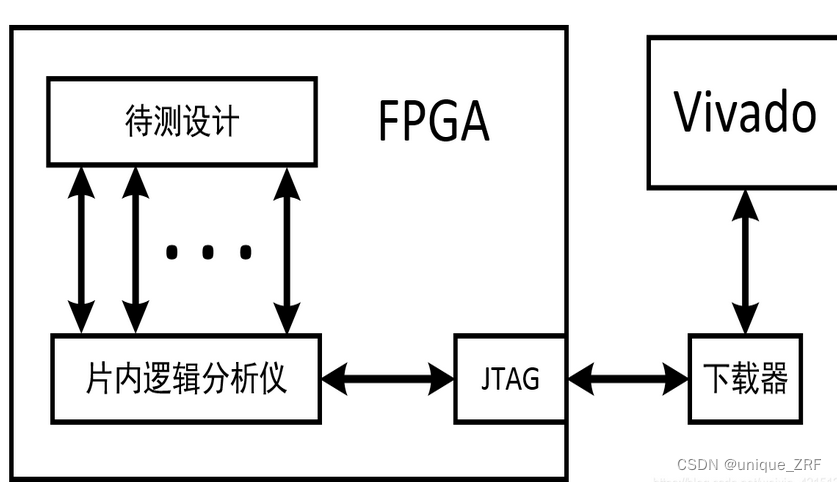

一、ILA简介

为了验证代码的正确性和不同条件下的可靠性,常通过仿真进行验证,但是仿真时间较长,工作量较大,有些驱动模块的模型无法获取的情况下,仿真很难进行,所以采用ILA工具,来实时抓取FPGA内部数字信号的波形,分析逻辑错误的原因,帮助debug。

二、ILA的使用方法

下面将分别介绍三种创建ILA调试环境的方法:

方法1:使用IP核创建ILA调试环境

方法2:使用 Debug 标记创建 ILA

方法3:使用路径标记和Set up debug 菜单创建 ILA 调试环境

方法1 — 使用IP核创建ILA调试环境

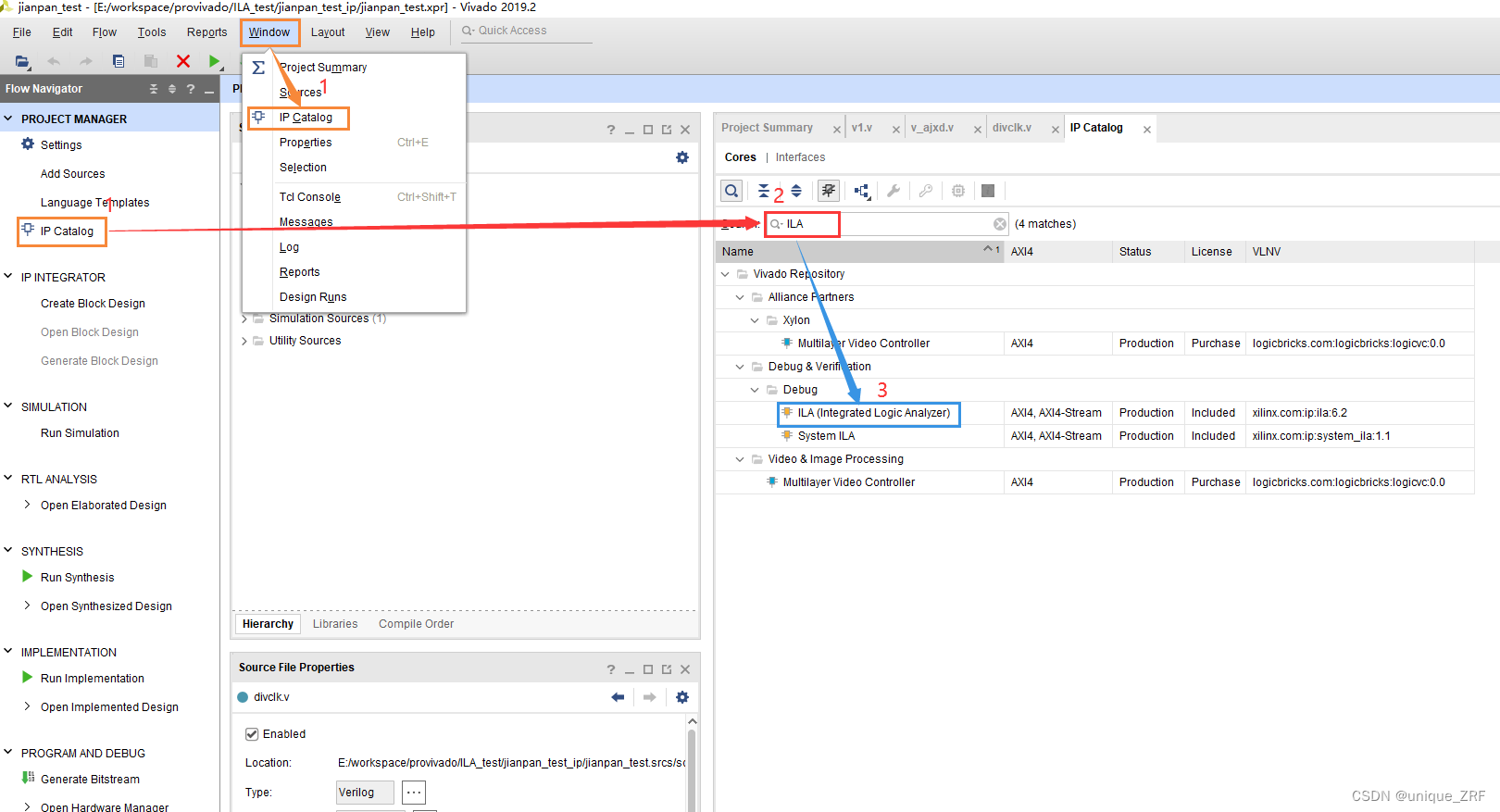

创建ILA IP核

- 点击左侧[PROJECT MANAGER]栏–>[IP Catalog]或者菜单栏下[Window]–>[IP Catalog],然后在右侧出现的[IP Catalog]窗口下搜索[ILA],双击选择[Debug]下的[ILA]进行IP配置,操作步骤如下图所示:

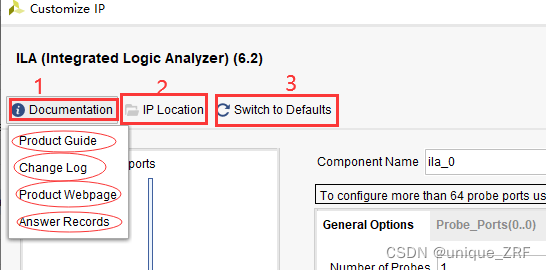

2. ILA IP的设置

(1)Documentation:IP 相关文档入口,其中的[Product Guide] 是 IP 手册查看入口,[Change Log] 是 IP 版本更新记录,[Product Webpage]是 IP 相关介绍的网页版

(2)IP Location:设置 IP 的存放路径入口,点击出现如下图所示窗口,在窗口里可以通过点击“…”设置更换存放路径,默认是存放在工程路径下的…<工程名>.srcs\ sources_1\ ip,这里我们就保持默认。

(3)Switch to Default:点击后所有的设置恢复到默认值。

(4)Component Name:设置生成 IP Core 的名称,这里保持默认设置。

(5)这里是一个提示,提示通过该界面设置最多可设置 64 个探针,如果想设置更多的探针需要使用 Tcl 脚本命令去设置,具体用法可以查询 IP 手册。

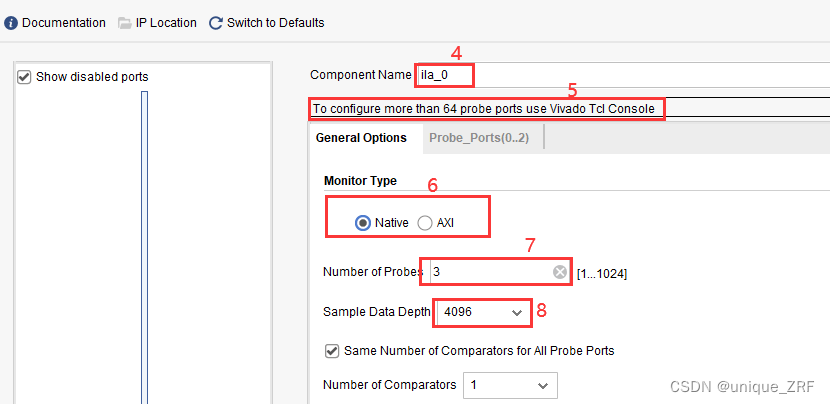

(6)ILA 探针接口类型设置

Native:常规普通接口模式

AXI:AXI 接口模式,用于调试 AXI 接口信号

(7)Number of Probes:探针数量设置,要观察3个信号,所以这里设置探针数量为3。

(8)Sample Data Depth:采样数据深度,设置的数值越大,采样的数据越多,看到的波形数据越多,但是最终占用的资源也会越多,并不是设置的越大越好。从下拉框也能看出最大也只能设置为 131072,这个根据实际需求进行合适的设置即可,我们这里选择设置 4096。

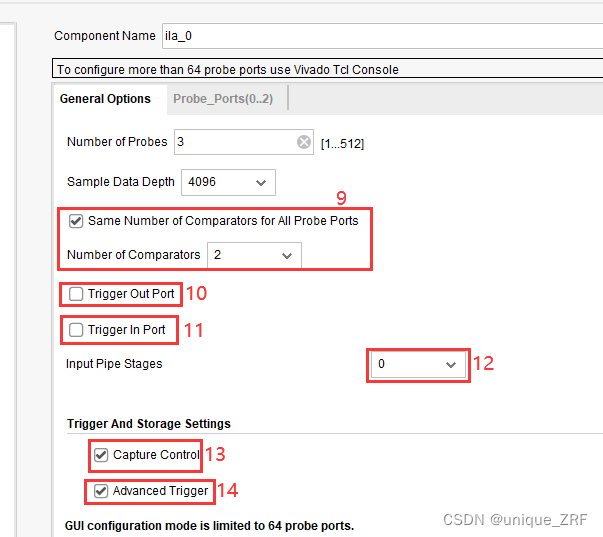

(9)Same Number of Comparators for All Probe Ports:这里是设置相同探针接口的 Comparators 的个数,不勾选,下面的 Number of Comparators 就会消失。默认勾选,后面的参数也保持默认,我们使用其基本功能。

(10)Trigger Out Port:触发输出端口,可用于 ILA 模块的级联或一些高级功能,

具体使用参考 IP 手册,这里保持默认不勾选。

(11)Trigger In Port:触发输入端口,可用于手工设置添加触发信号或进行 ILA

模块的级联或一些高级功能,具体使用参考 IP 手册,这里保持默认不勾选。

(12)Input Pipe Stages:设置待探测信号打拍次数,如下图所示,可设置数值0~6,

一般情况下,采样时钟和探测信号是一个时钟域下,这里可以默认设置为 0 即

可。

(13)Capture Control:这里勾选后可在调试查看波形窗口进行对 Capture mode

的设置,如果不勾选后面有关 Capture mode 就不可修改,这里勾选。

(14)Advanced Trigger:这里勾选后可在调试查看波形窗口进行对 Trigger mode

的设置,如果不勾选后面有关 Trigger mode 就不可修改,这里勾选。

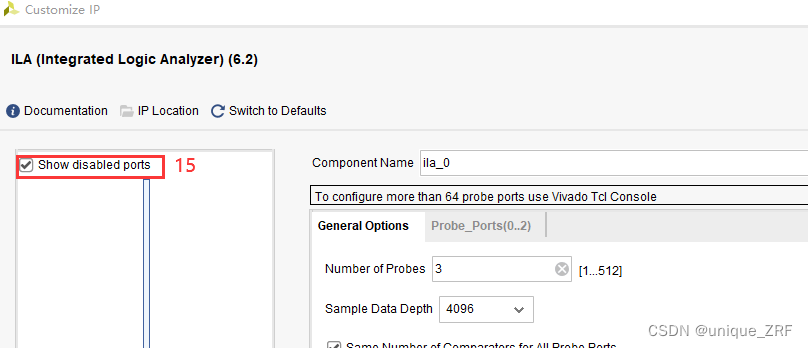

(15)Show disabled ports:在 IP 核的模拟示意图中展示出未使用信号引脚。

(15)Show disabled ports:在 IP 核的模拟示意图中展示出未使用信号引脚。

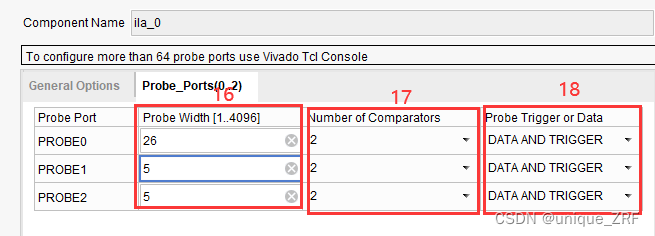

(16)Probe Width:探针数据信号的位宽设置,我们需要对一个 26bit 和两个 5bit 信

号进行在线观察,这里将 Probe0位宽设置为 26,Probe1和Probe2位宽设置为5。

(17)Number of Comparators:如果已经勾选(9)处,这里就不可设置,如果没有勾选,这里就可以设置。保持默认即可

(18)Probe Trigger or Data:对探针设置触发器或数据,有3种选项:

DATA AND TRIGGER:既是数据又可作为触发条件;

DATA:仅作为数据,不可作为触发条件;

TRIGGER:仅可作为触发条件。

设置完成后点击下方[OK]–>[Generate]生成IP核

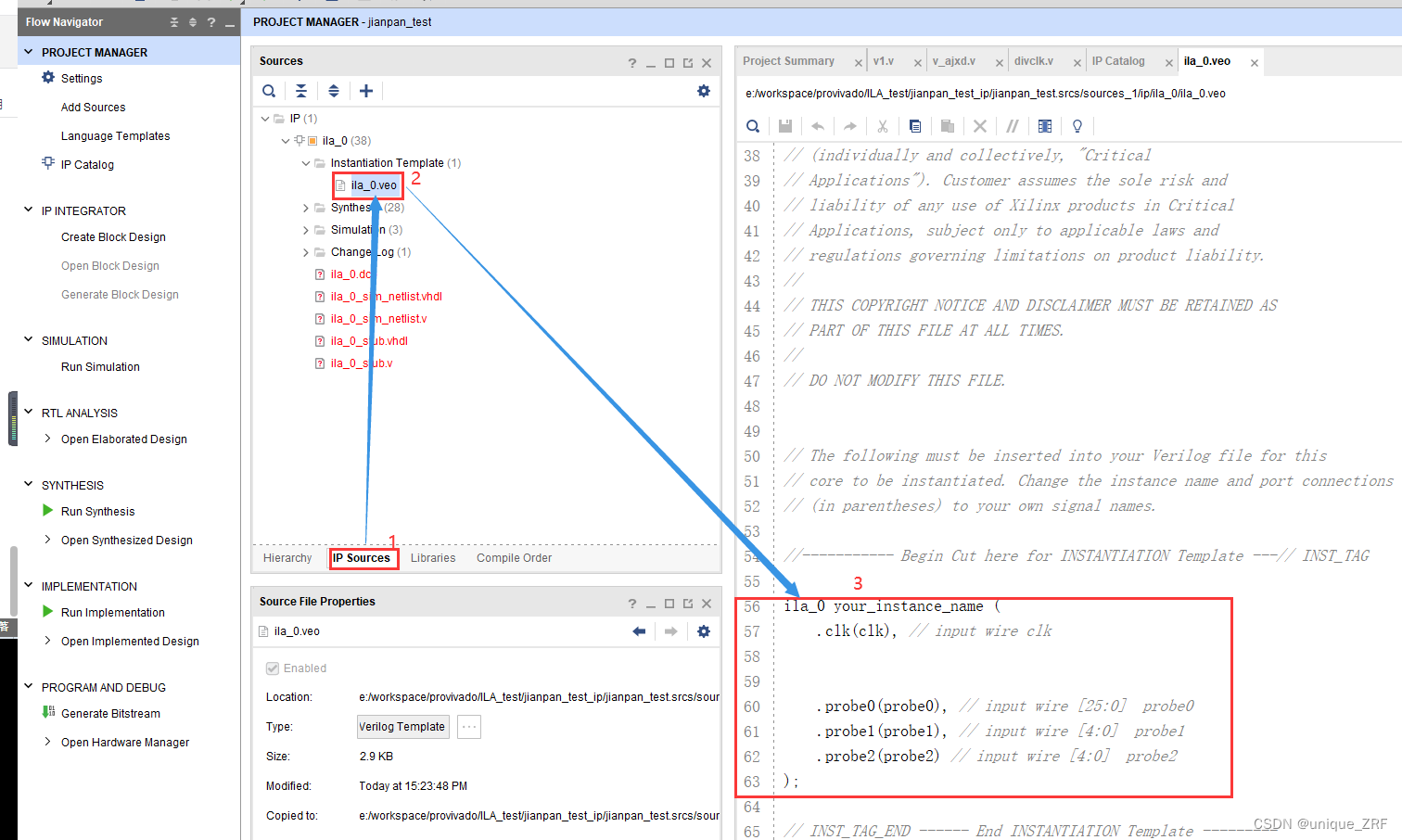

- IP核的使用

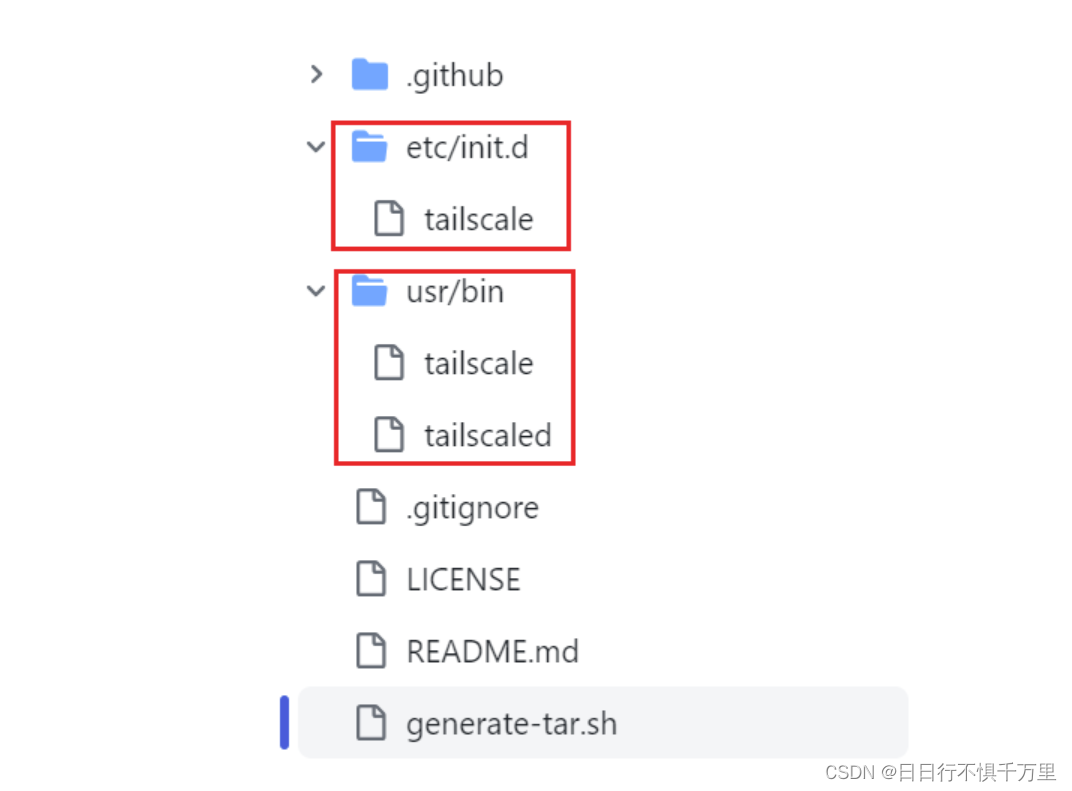

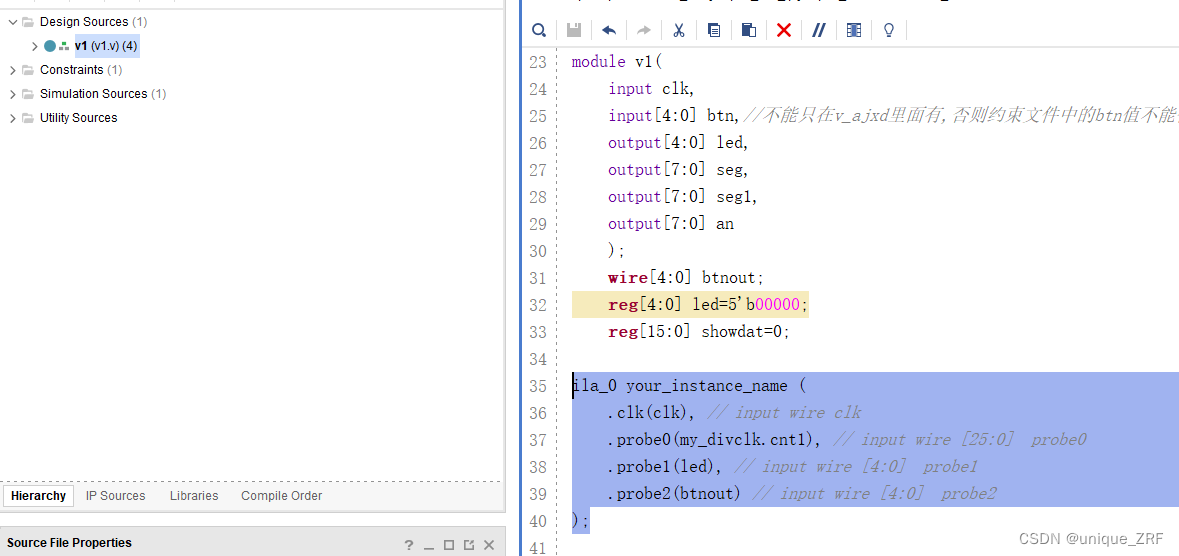

生成的ILA IP核的用法,在[IP Sources]下找到[ila_0.veo],如下所示,为调用举例,将其复制,放到主程序中。

Verilog 中“.”的含义是:下一级文件中的内容

要看的是divclk中cnt1、led和btnout信号的变化,所以填入对应的probe中进行绑定即可:

其硬件测试步骤在介绍完三种方法后一起来做~

方法二 — 使用 Debug 标记创建 ILA

对需观察信号进行标记

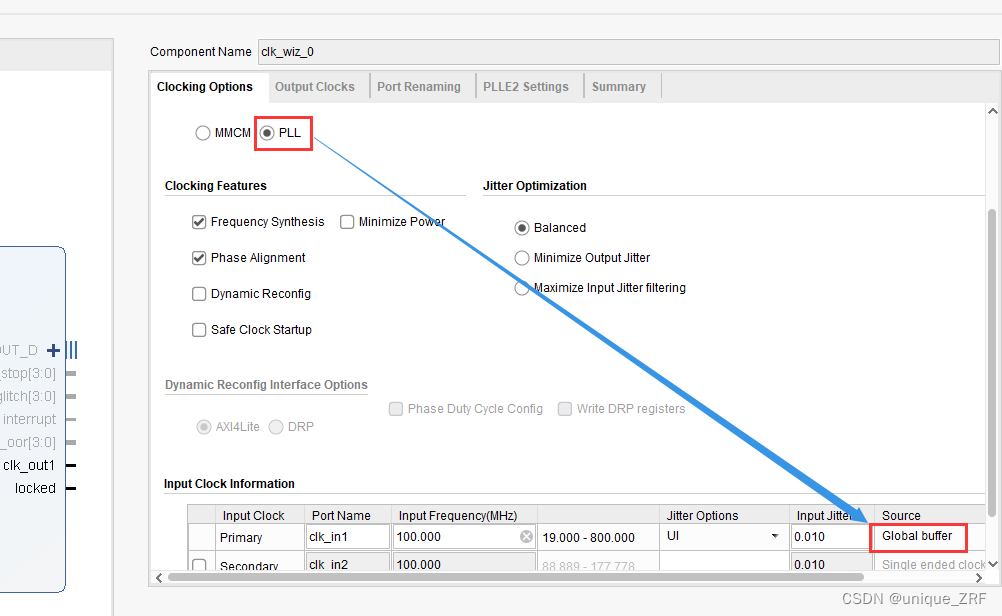

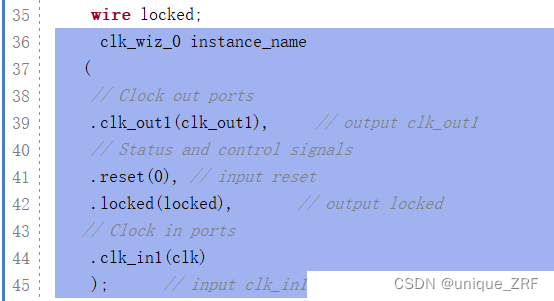

使用clk IP核,生成一个clk_out1,令其为ILA的工作时钟,查看现象,其设置如下:

IP核调用:

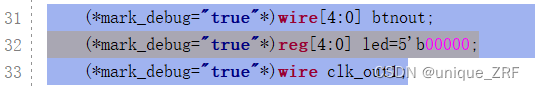

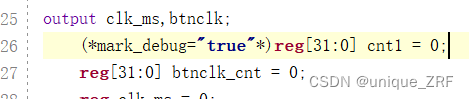

在代码中进行标记,在信号定义前面加上(mark_debug=“true”)即可进行标记,如下所示:

对工程进行保存后重新综合

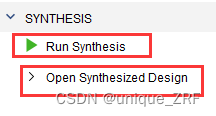

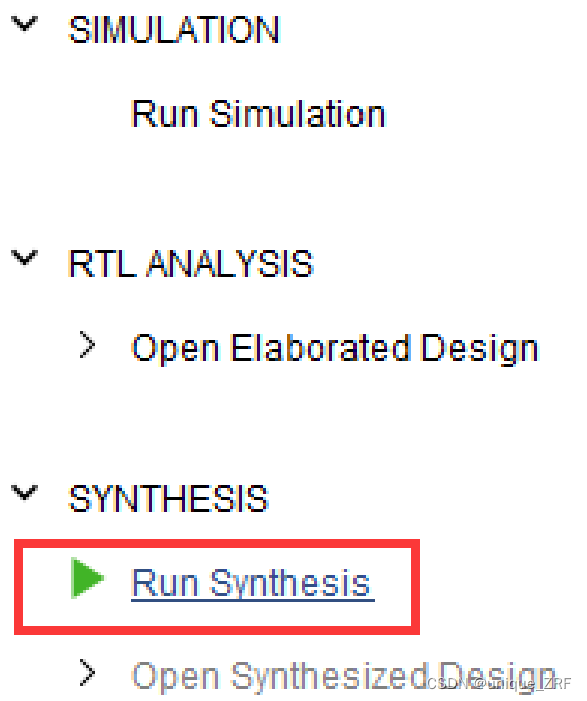

对工程进行综合,综合:

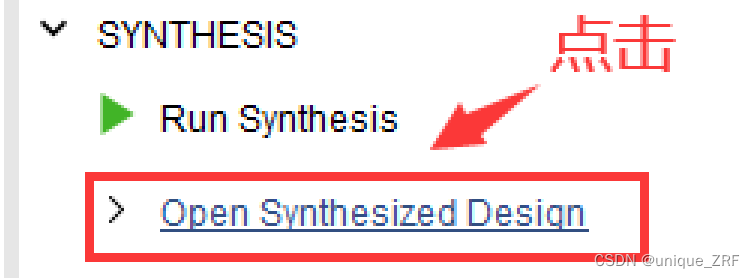

点击[Run Synthesis],综合完成之后,点击[Open Synthesized Design],然后进行Debug信号和探针进行关联。

Debug信号和探针的关联

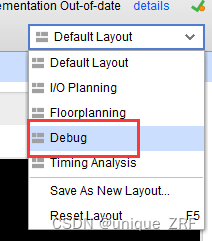

点击[Open Synthesized Design]之后,点击右上角的[Default Layout],然后选择[Debug]

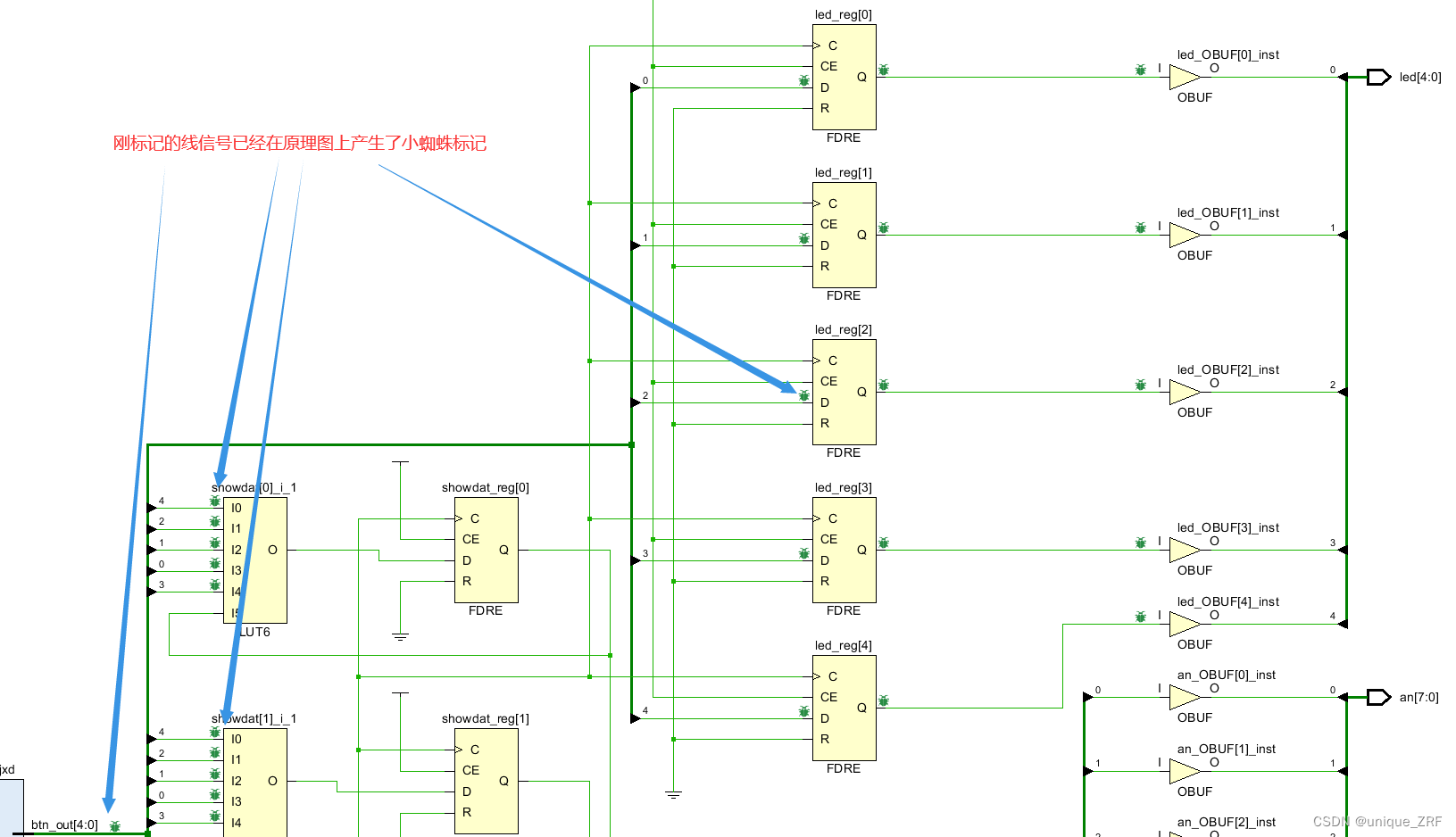

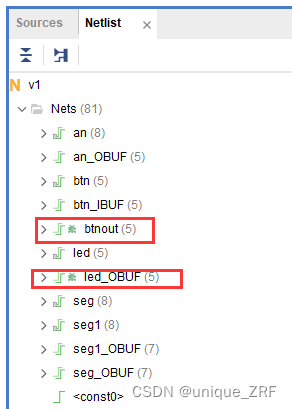

在左侧网表管理窗口,也可以看到小蜘蛛图标:

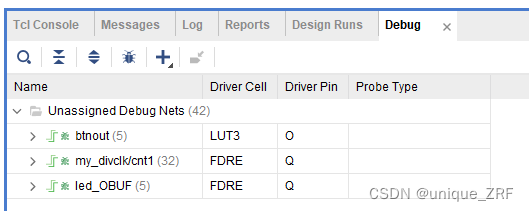

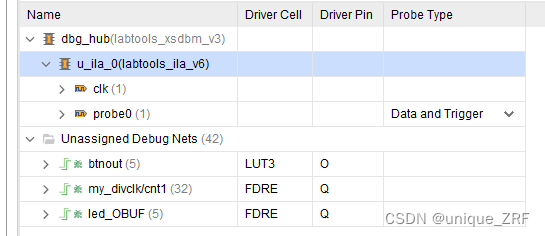

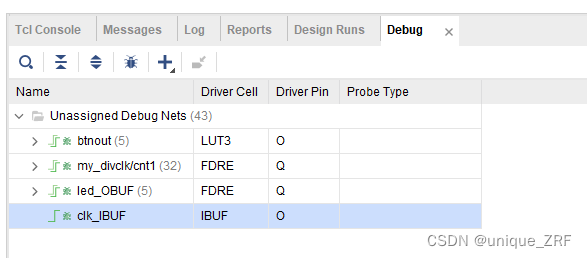

下方的[Debug]窗口,可以看到所有已经标记但是未关联ILA的信号:

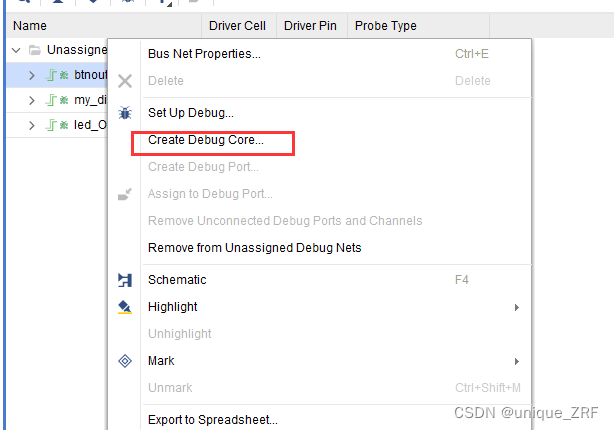

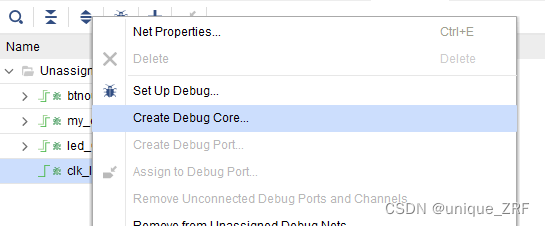

右键点击还未关联的标记信号,在菜单中选择 Create Debug

Core。

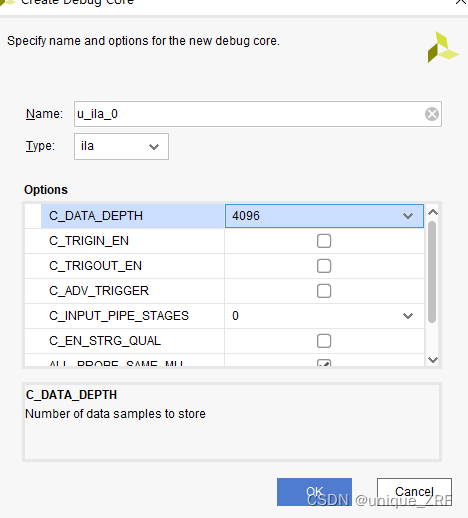

新的窗口可以设置 ILA 的名称,选择 ILA 的类型,同时也可以进行采样深度设置等操作。和我们在上一节讲解的内容进行相同的设置,我们也将采样深度设置为 4096。

完成 ILA 的设置后,呈现如下界面:

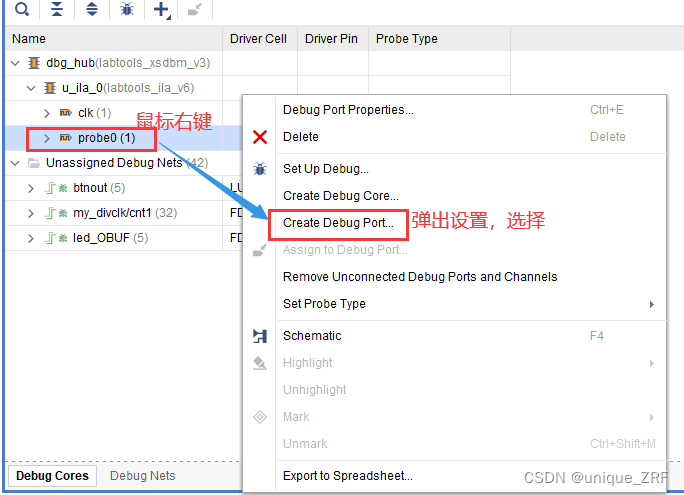

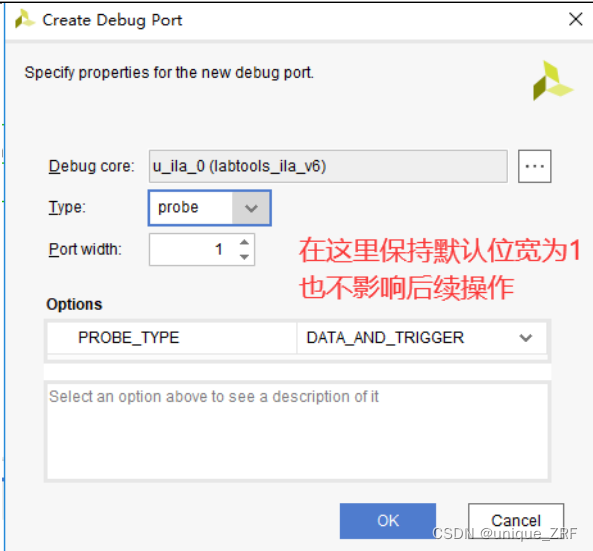

我们看到,我们需要对包括时钟信号在内的 4 个信号进行关联绑定,而刚刚创建的 ILA 工具,包括时钟绑定信号在内只有 2 组可以进行绑定的探针。这时,需要结合采样信号的实际组数,将不足的探针组数补齐。右键点击 probe0,弹出菜单后点击 Create Debug Port,如下所示:

这样,34组未绑定的信号端口,就有了 4 组 probe 探针。虽然此时的探针位宽都默认为 1,但是并不影响我们绑定探测信号后的结果。接下来,即可开始完成探针和探测信号的绑定。

绑定前,先观察点击时钟信号的下拉选项,发现时钟信号的绑定标号为灰色圆圈实心点。绑定信号名称为默认未绑定的 Ch0。

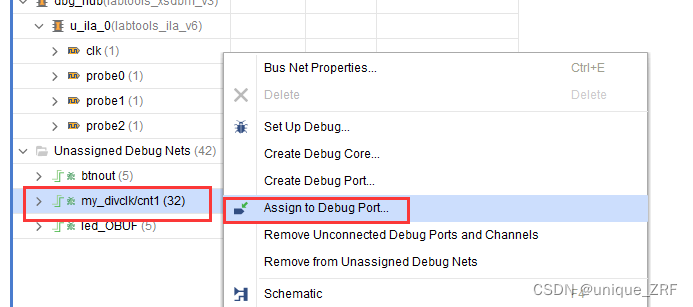

先以cnt1信号为例,右键点击 my_divclk/cnt1,在弹出的窗口菜单中选择 Assign to Debug Port。

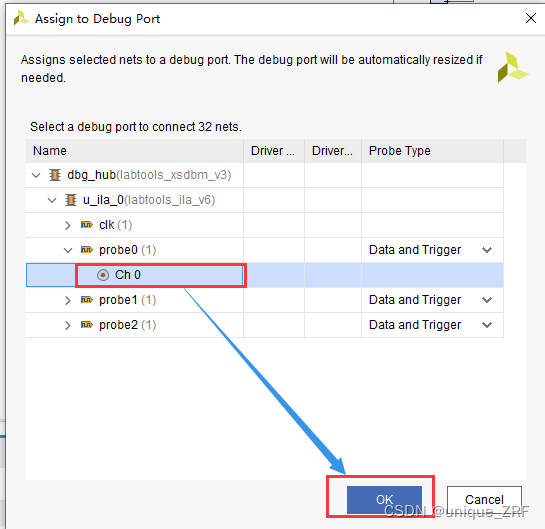

然后,选择probe0下的Ch0,点击OK即可,其他线信号也如此操作

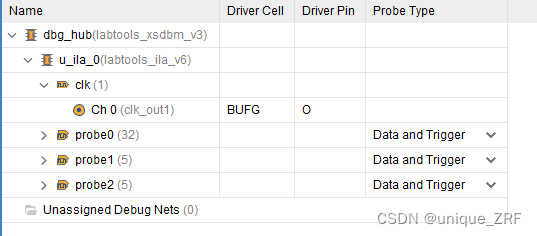

最后,[Unassigned Debug Nets]栏下的线信号数目为0。

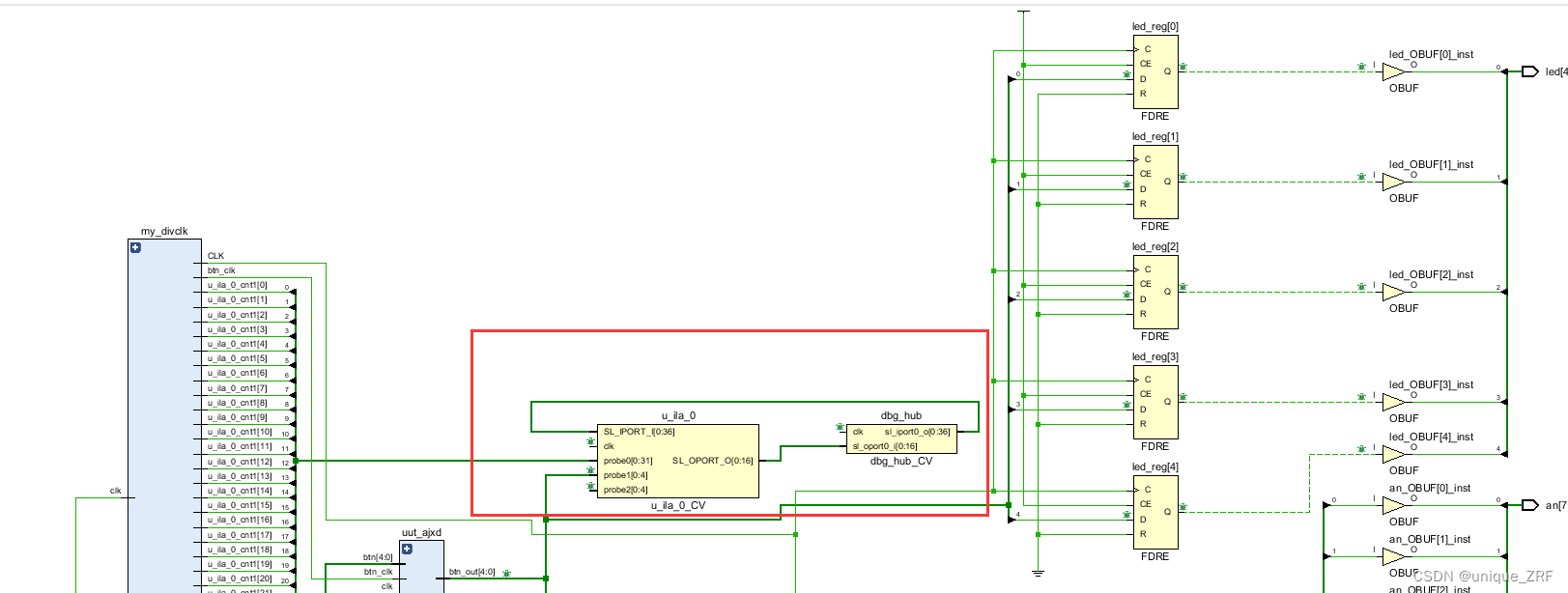

保存之后,观察原理图,发现多了ila和dbg模块:

测试

其硬件测试步骤在介绍完三种方法后一起来做~

值得注意的是,在使用 mark_debug 方法抓线完成调试工作后,要记得删除源码中的 mark_debug 标记。否则,不但代码会留下杂乱的调试痕迹,而且被标记的信号会保持占用工程的逻辑资源,导致工程的总逻辑资源使用量增大。

方法三 — 使用路径标记和Set up debug 菜单创建 ILA 调试环境

在实际使用中,我们还可以通过在综合后的原理图上直接进行调试标记,而简便的锁定需要观察的信号。这样,我们就不用在代码中进行标记,也不需要承担在调试完成后忘记在代码中删除 mark_debug 标记的风险了。

还是回到工程原本未改动的初始状态,首先对工程进行分析和综合。

分析和综合完成:

综合完成后点击[Open Synthesized Design]:

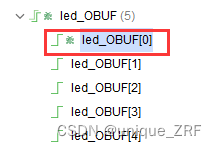

这里,我们直接从 Schematic 原理图中,寻找并标记 led、cnt1和btnout信号。仔细观察原理图,我们发现led变为了led_OBUF。由于VIVADO 会按自己的规则给编译后的信号命名,所以我们推测,led_OBUF信号就在我们当前的原理图中,只是命名方式发生了变化。

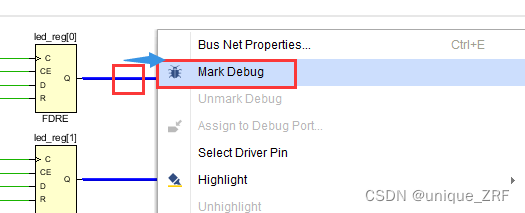

右键点击led_OBUF[0],选择[Mark Debug]:

这时,该网络即被标记为待观测信号:

其他网络类似,也可从左边Nets栏下直接鼠标右键,选择[Mark Debug]进行标记,将btnout、led_OBUF、和模块my_divclk下的cnt1进行标记即可。

所以在下面[Debug]栏中出现以下内容:

然后操作步骤与方法二中一致,鼠标右键上图中任意一个net,选择[Create Debut Core…]

然后create Debug Port,进行联结即可。然后保存、生成bit流,测试方式与方法一一致。

ILA调试及板级验证

烧录程序

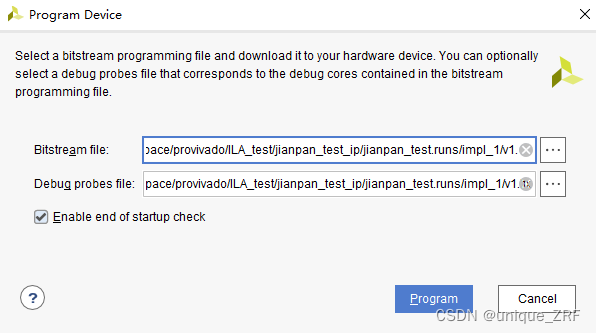

点击左侧[PROGERAM AND DEBUG]栏下的[Generate Bitstream],生成bit流文件,然后点击[Open Hardware Manager],将bit流文件和自动相关联的Debug文件一起烧录进板卡,如下所示:

基本操作

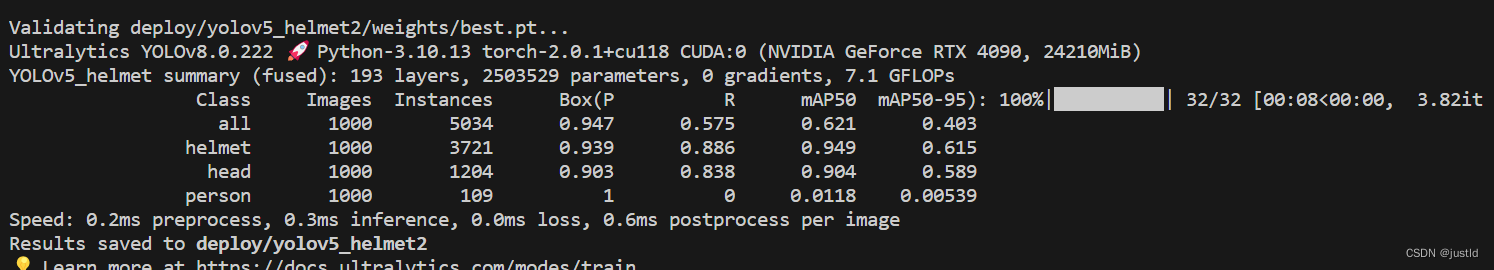

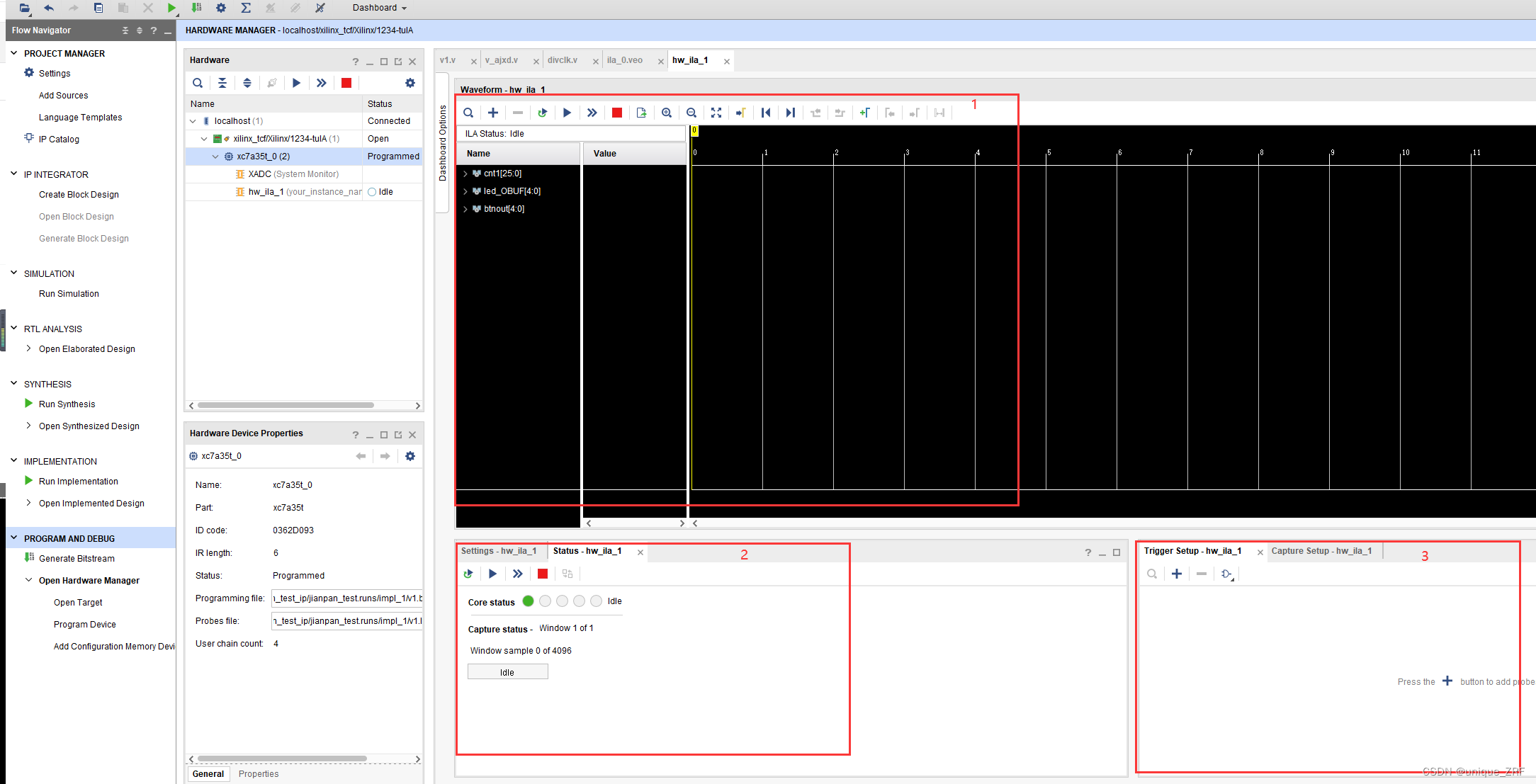

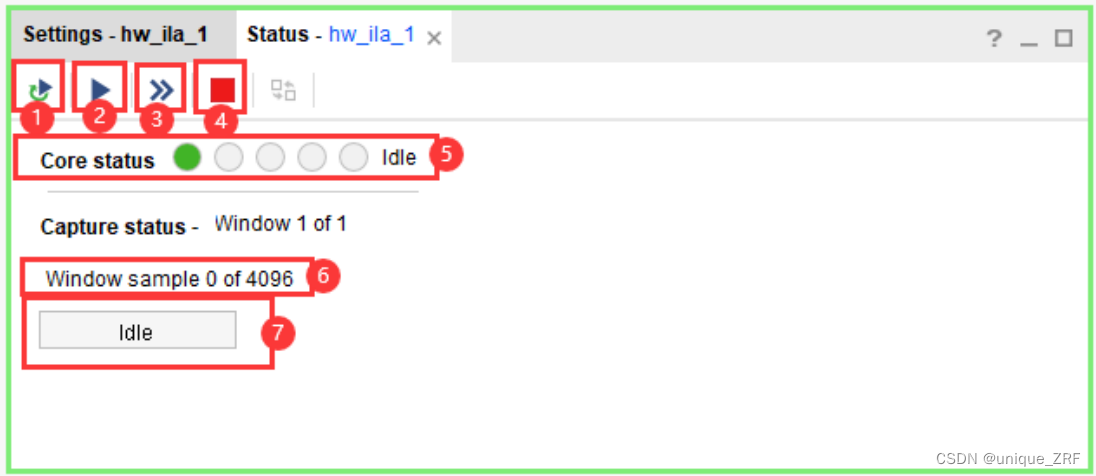

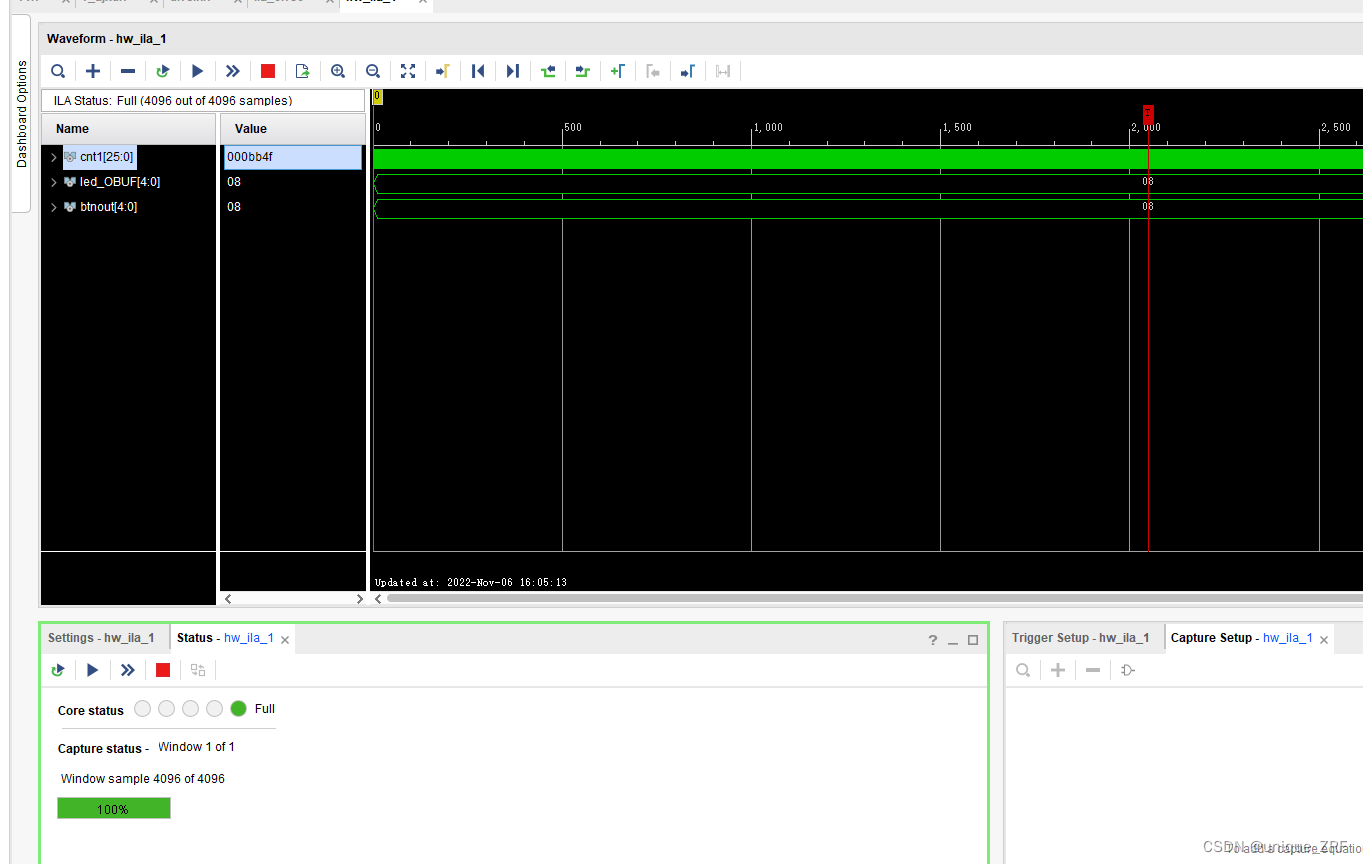

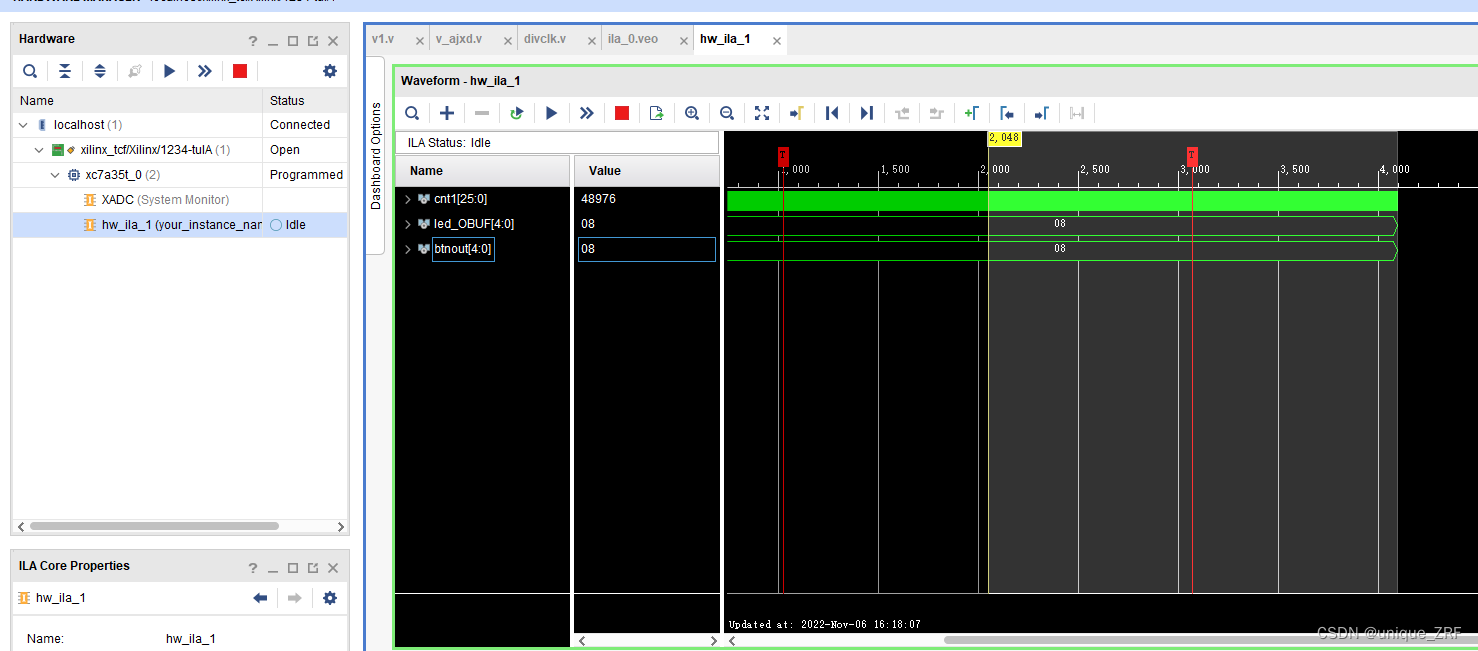

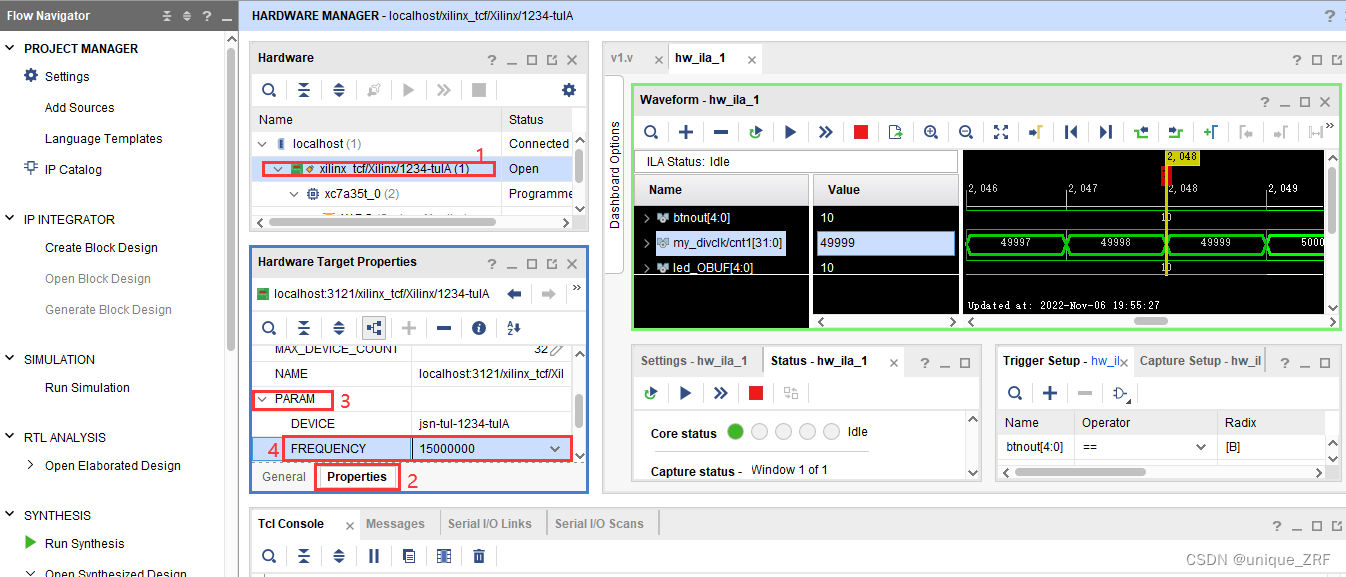

这里,我们已经按照上面三种方法其中的一种来生成了bit流文件。bit流文件和Debug文件烧录完成后会自动出现如下图所示界面。该界面即 ILA 调试界面。

窗口 1:波形显示窗口,可以通过点击➕添加想查看的波形的信号。因为在IP 设置中对探针设置的时候,cnt 和 key_state 信号的 Probe Trigger or Data 属性设置为了“DATA AND TRIGGER”,所以这里可查看的信号有 cnt1、led_OBUF和btnout。

当然,通常在下载完程序后,ILA 能够非常智能的识别出设计师期望观察的信号,同时,在右键菜单也可以找到删除观察信号的指令。这样,有限的窗口面积就可以被充分利用,自由调配和增减所需观察信号的条目。

窗口 2:ILA Croe 的状态控制和显示窗口。

按钮①:设置采样执行过程为循环采样

按钮②:启动采样按钮。按下后将启动 ILA 采样。根据是单次采样还是循环采样,根据是有条件触发还是无条件触发,启动后会呈现 ILA 状态的周期性变化或等待触发条件的到来。

按钮③:无条件执行 ILA 采样。

按钮④:停止采样按钮。

状态栏⑤:状态栏⑤由 5 个空心圈组成,唯一的实心绿色点所处的位置表征ILA 的运行状态。

状态栏⑥:已采集的点数占总采集点数的关系。

状态栏⑦:以进度条的方式结合状态名称,标明当前所处的状态以及采样过程中执行状态的百分比。

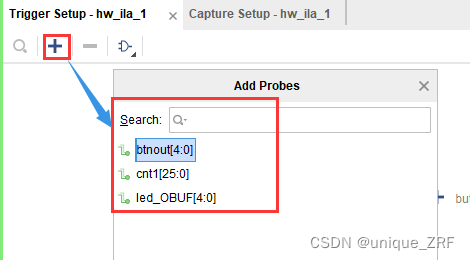

窗口 3:添加触发信号窗口,如下图所示,点击窗口内➕ 添加产生触发条件的信号(两个地方的➕ 都可以进行信号的添加)。

添加之后如下图所示,可以设置其触发条件和触发情况:

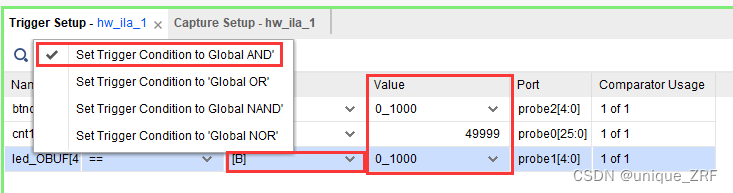

点击按钮 设置多个信号产生触发信号时的条件,与、或、同或、异或,西面还可以设置触发条件,如下图所示:

设置多个信号产生触发信号时的条件,与、或、同或、异或,西面还可以设置触发条件,如下图所示:

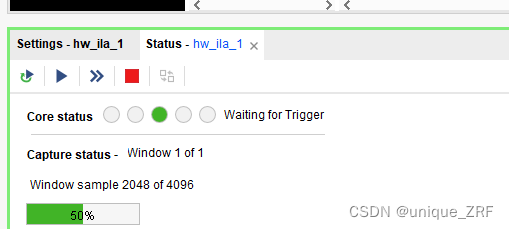

触发条件设置完成后,点击Run:

等待触发如下图所示:

然后按下板卡上的按键:

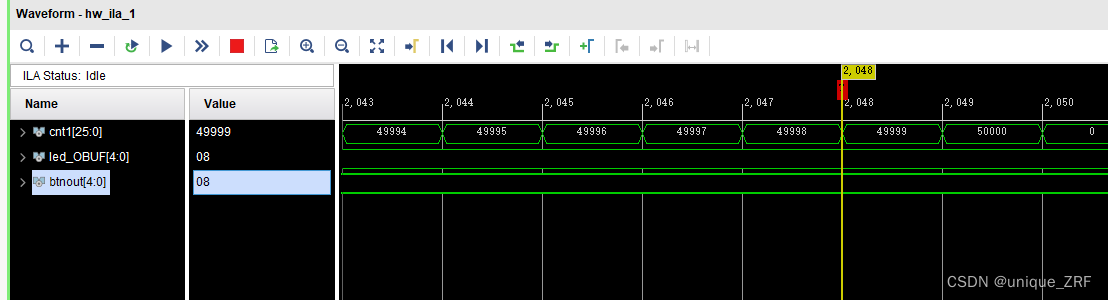

可以看到满足触发条件后的波形窗口。波形中有红色 T 标记的符号,正好处在第 2048 个采样点处,即我们预设的 4096 个采样点的中点。

将cnt1的进制数改为无符号10进制结果如下图所示,这样就完成了本次ILA抓线的任务,其结果与预定设想相同。

其他设置

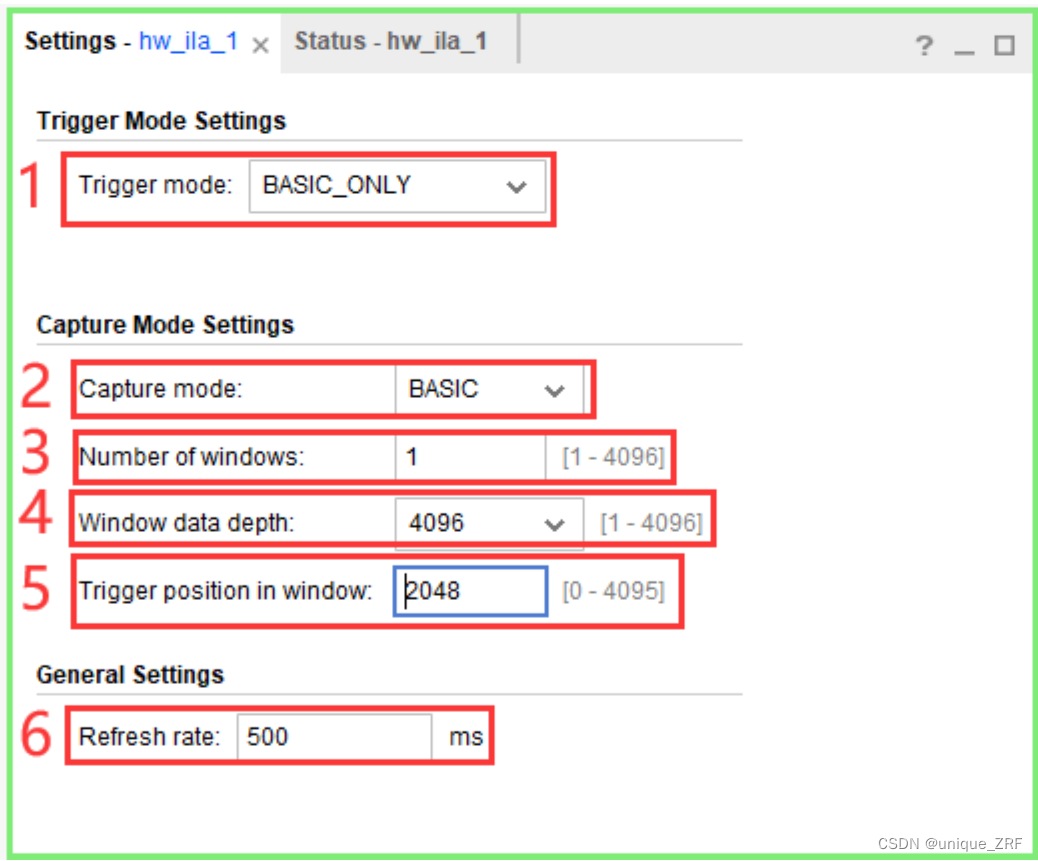

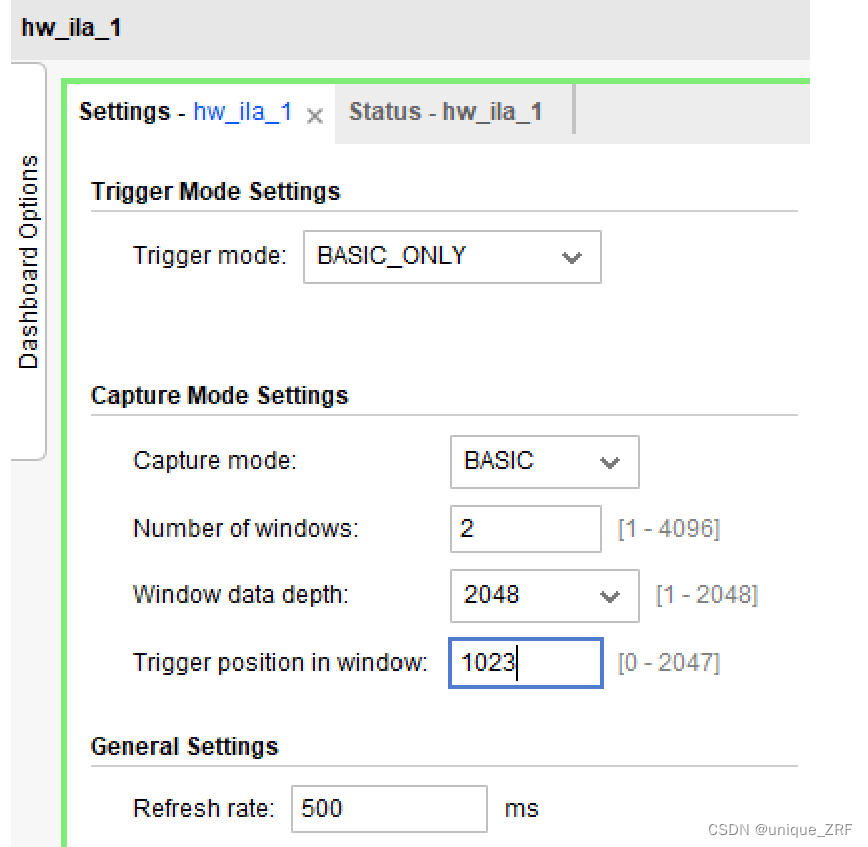

窗口 4:设置触发显示窗口,点击窗口右上角的方框放大这个窗口,可以看到这个窗口全部的设置参数。

(1)Trigger mode:触发模式设置,选择默认的 BASIC_ONLY 即可,有关ADVANCED_ONLY 模式的具体使用,可查看 IP 手册。

(2)Capture mode:捕获模式设置,选择默认的 BASIC 即可,有关 ALWAYS模式的具体使用,可查看 IP 手册。

注:有关上述(1)(2),如果在前面的 IP 创建的时候不勾选 13、14 处的选项,上述(1)(2)是不可设置的。

(3)Number of windows:显示窗口个数,默认为 1,更改这里为 2。窗口个数的设定值可以设定在同样的触发条件下,连续多次的触发显示在不同的窗口中。随着窗口数量的增加,势必会使得单个窗口的采样深度变小。所有窗口采样深度的总和不能大于总的采样深度。这里更改后下面 Windows data depth 的最大值会自动变为 2048(4096=22048=41024=……)。

(4)Windows data depth:窗口显示数据深度,上面设置为 2 后,这里最大可设置为 2048,设置 2048 即可。如果仅设置 1 次采样,则其最大值为 IP 核配置、抓线设置中采样的最大值。

(5)Trigger position in windows:设置触发位置在窗口波形中显示的位置,一般根据需求设置,这里设置波形窗口的中间位置,即设置为 1023。

(6)Refresh rate:连续触发模式下,相邻触发之间的刷新时间,这里保持默认即可。

按照上述说明进行如下设置:

按照上述设置,点击[Run],按下按键3之后的结果:

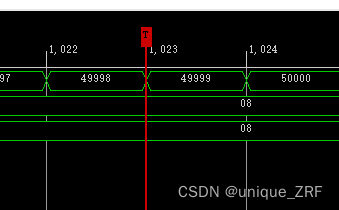

放大之后的结果

从触发的波形可以看出,与之前波形相比,现在是出现两次触发波形,与我们上面设置的窗口个数是对应的。同时,红色触发标记点,正好在第 1023 个采样点出现,和我们刚刚在Settings 中设置的触发点位置是一致的。

整个在线调试工具 ILA Croe 的使用基本就结束了,下面介绍其他方法。

总结

前面介绍了3中ILA工具的生成核使用方法,每种方法各有利弊。

第一种方法:生成IP核操作较为繁琐,要注意例化的位数与要抓取的信号线的位数一致。

第二种方法:使用Debug标记创建ILA调试环境,与第一种方法相比,能够弱化抓线信号的位宽对抓线调试的影响,但是在mark_debug方法抓线完成调试工作后,要删除源码中的 mark_debug 标记。否则,不但代码会留下杂乱的调试痕迹,而且被标记的信号会保持占用工程的逻辑资源,导致工程的总逻辑资源使用量增大。

第三种方法:在综合后的原理图上直接进行调试标记克服了第二种方法的缺点,不用再代码中进行标记,但是标记的时候,vivado会按照自己的规则给编译后的信号命名,所以要细心寻找要标记的信号线。

其他

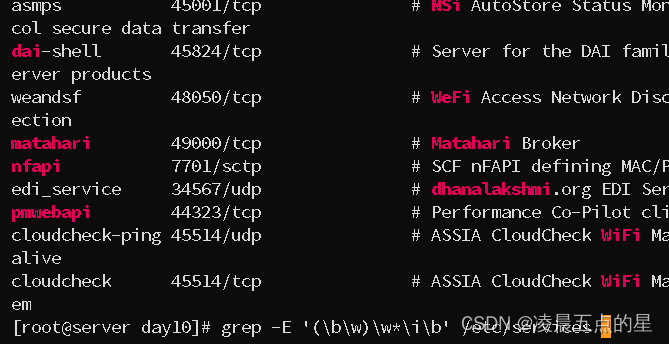

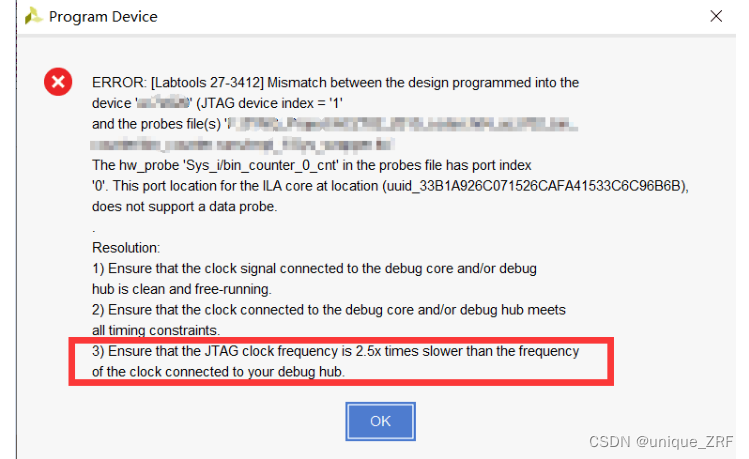

ILA 可正常运行的频率区间,大致为下载器时钟频率信号的 2.5 倍至 VIVADO 报告工程时序违例的时钟范围区间。

这条要求指出,ILA 的时钟频率,**不得低于 JTAG 下载器的时钟频率的 2.5倍。**事实证明,过低的 ILA 时钟频率,会导致 ILA 工作不正常,无法启动,状态跳转不正常或报错等非特定现象的发生。当然,ILA 的工作频率也不是无线高的,过高的频率,会导致工程时序违例,从而发生无法抓取波形或者 VIVADO 无法识别到 ILA 等问题发生。

有时候,我们需要测试的工程,其 ILA 时钟频率非常低,并且不允许调整。遇到这种问题,我们这里,提供另一种解决该问题的思路,即降低 JTAG 下载器的频率。

根据前面讲解的 JTAG 频率和 ILA 频率的倍数关系,我们选择合理的 JTAG下载器频率,上图所示JTAG频率默认为15MHz,可将其适当调小。

按前面 VIVADO 提示的频率关系,在一定程度上迁就 ILA 的工作频率,这样又可以使 ILA 达到正常工作的频率范围了。