文章目录

- Pin Connection Diagrams

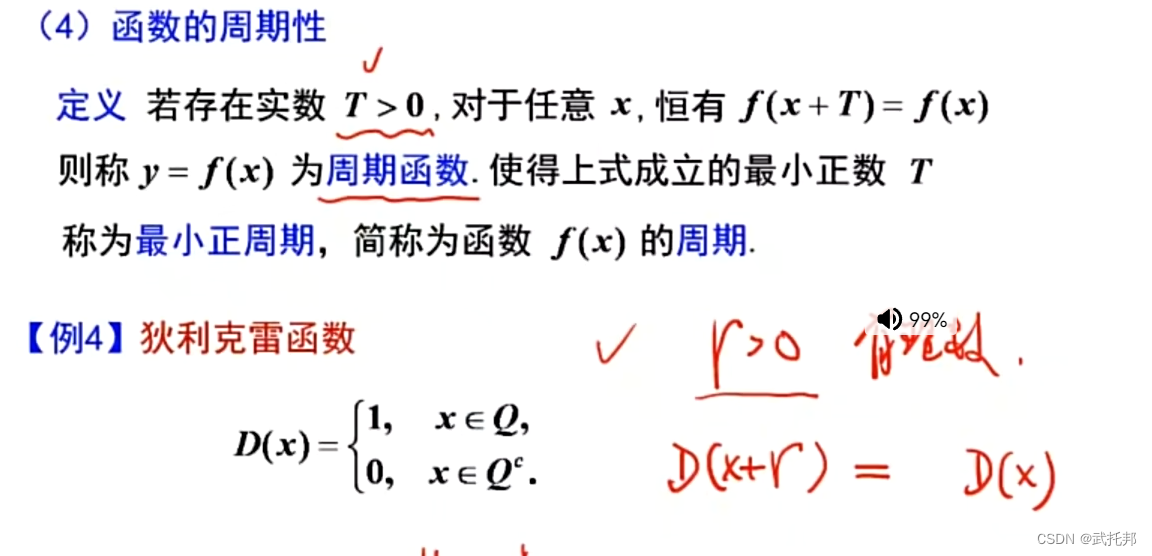

- 术语定义

- Pin List

- Port Overview

- Introduction

- Functional Overview

- Port Category

- Operation Mode运行模式

- Port Function

- 寄存器地址映射

- Port寄存器描述

- Pn/JP0 — Port Register

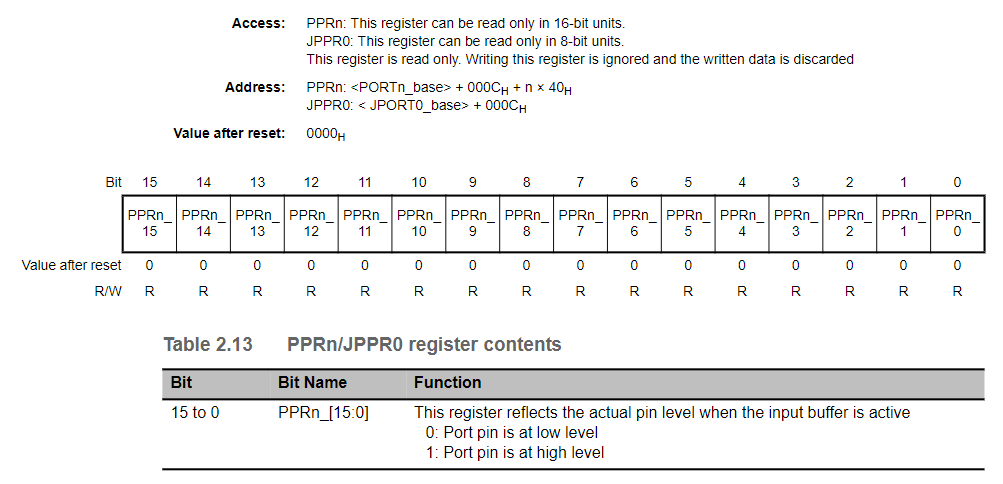

- PPRn/JPPR0 — Port Pin Read Register

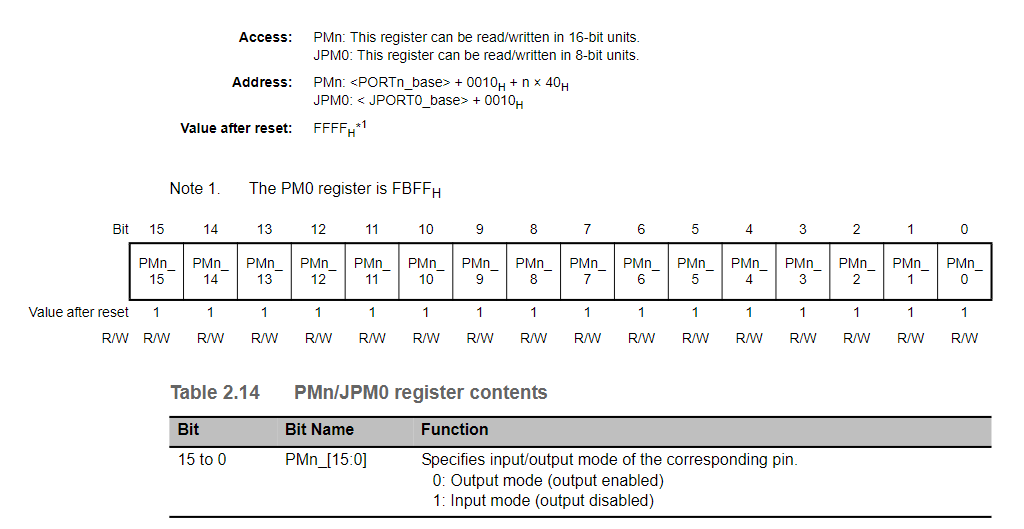

- PMn/JPM0 — Port Mode Register

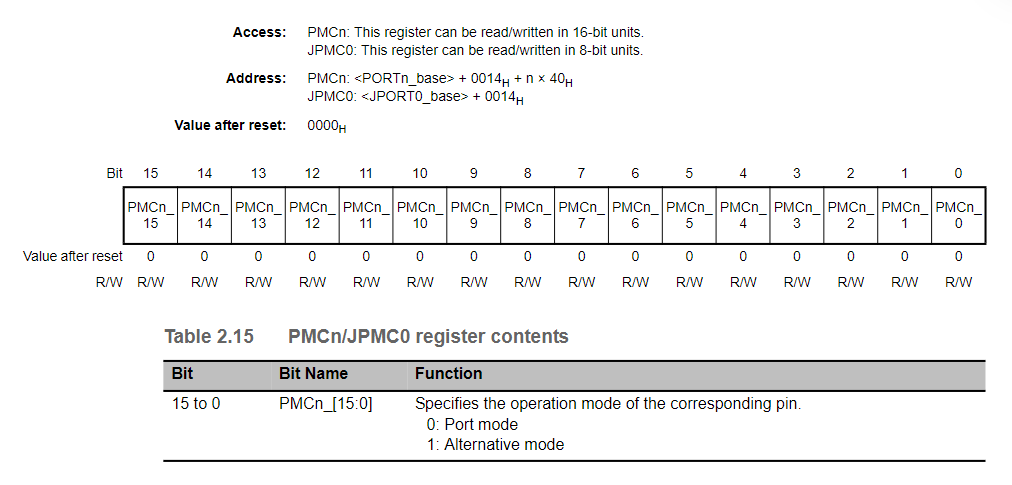

- PMCn/JPMC0 — Port Mode Control Register

- PFCn — Port Function Control Register

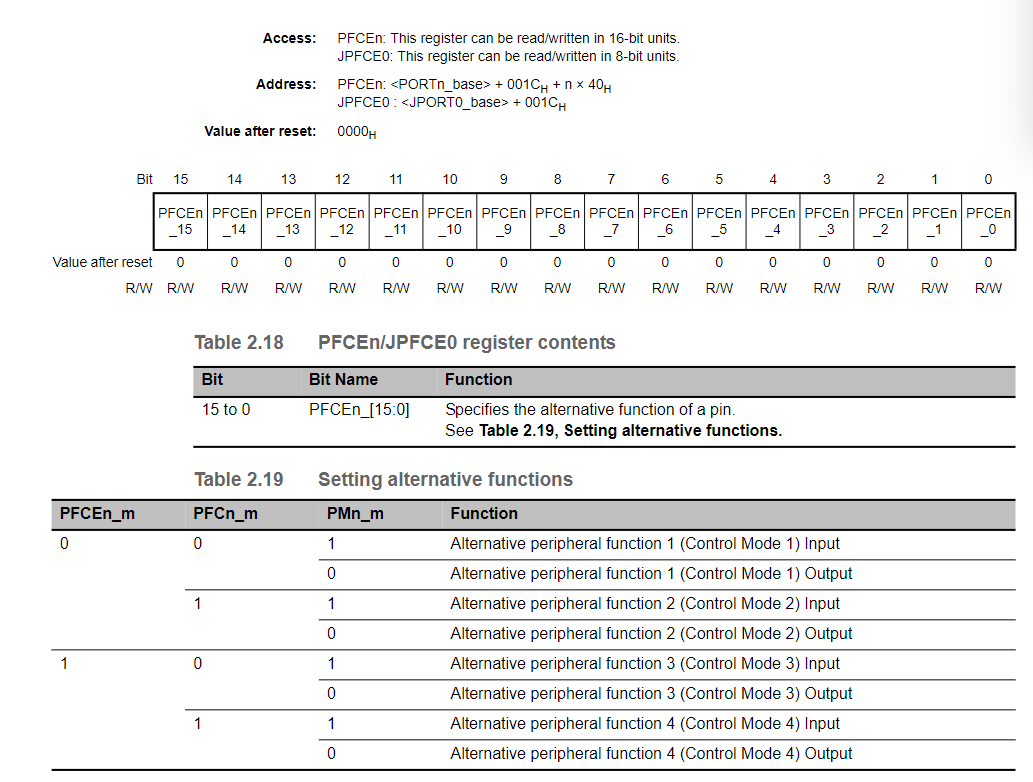

- PFCEn/JPFCE0 — Port Function Control Expansion Register

- PNOTn/JPNOT0 — Port Not Register

- PSRn/JPSR0 — Port Set/Reset Register

- PMSRn/JPMSR0 — Port Mode Set/Reset Register

- PMCSRn/JPMCSR0 — Port Mode Control Set/Reset Register

- PINVn/JPINV0 — Port output value Inversion Register

- PIBCn/JPIBC0 — Port Input Buffer Control Register

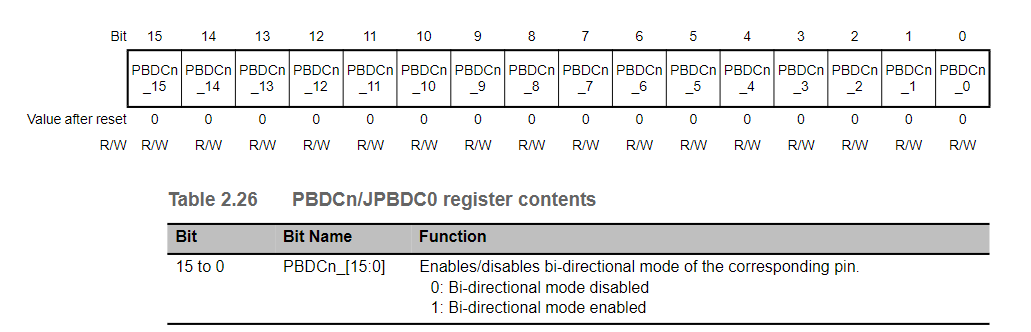

- PBDCn/JPBDC0 — Port Bi-Direction Control Register

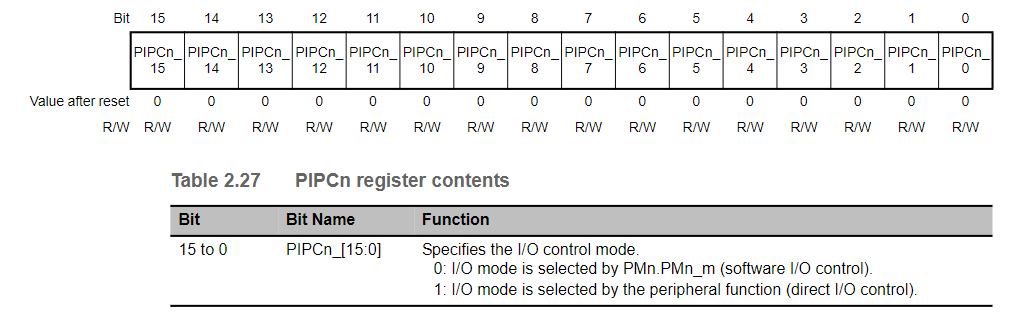

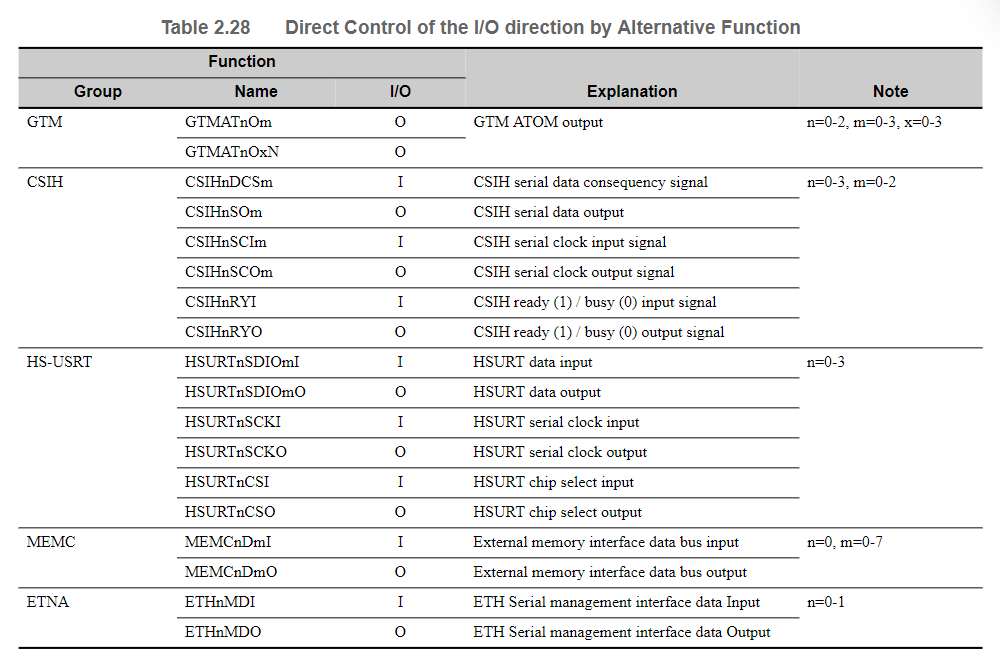

- PIPCn — Port IP Control Register

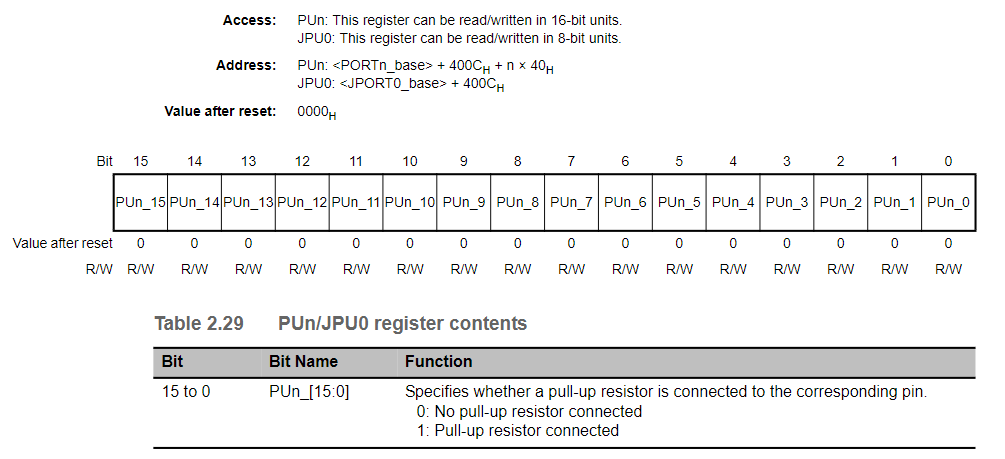

- PUn/JPU0 — Pull-Up Option Register

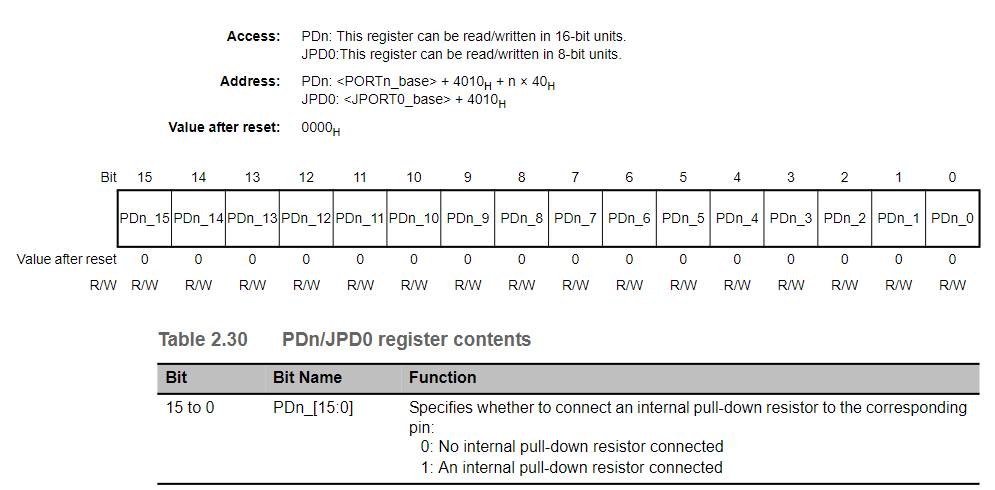

- PDn/JPD0 — Pull-down option Register

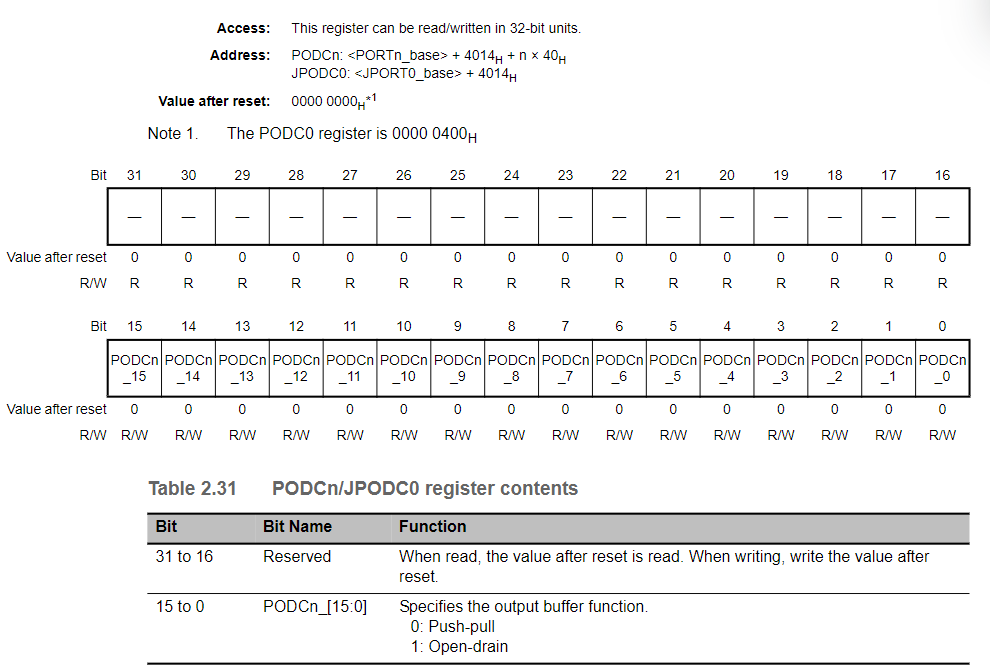

- PODCn/JPODC0 — Port Open Drain Control Register

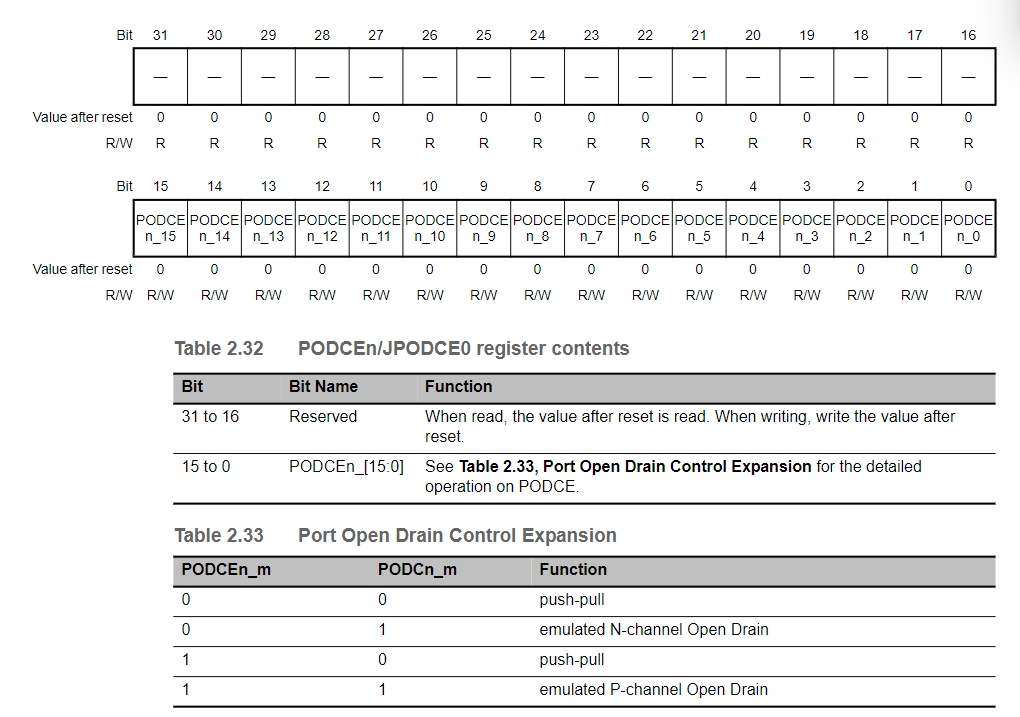

- PODCEn/JPODCE0 — Port Open Drain Control Expansion Register

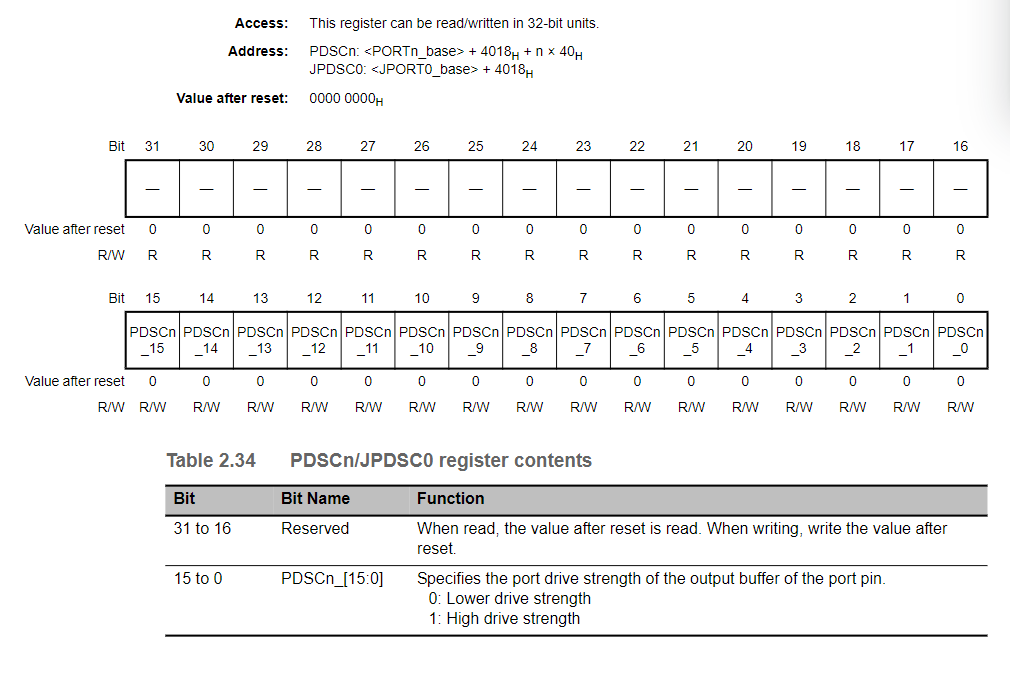

- PDSCn/JPDSC0 — Port drive strength control register

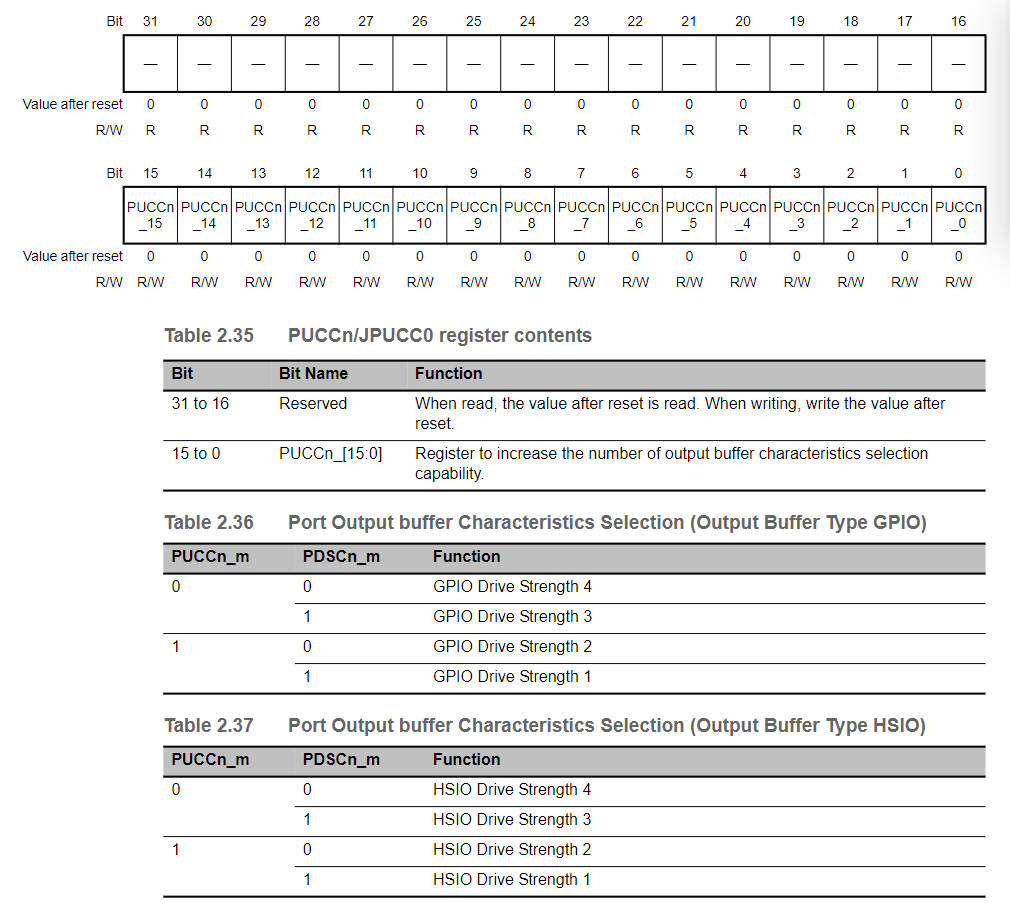

- PUCCn/JPUCC0 — Port Universal Characteristic Control Register

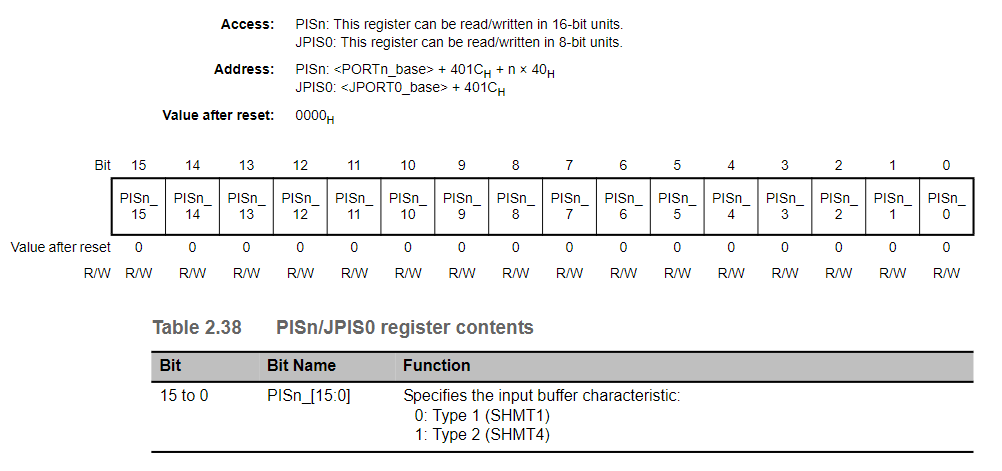

- PISn/JPIS0 — Port input buffer selection register

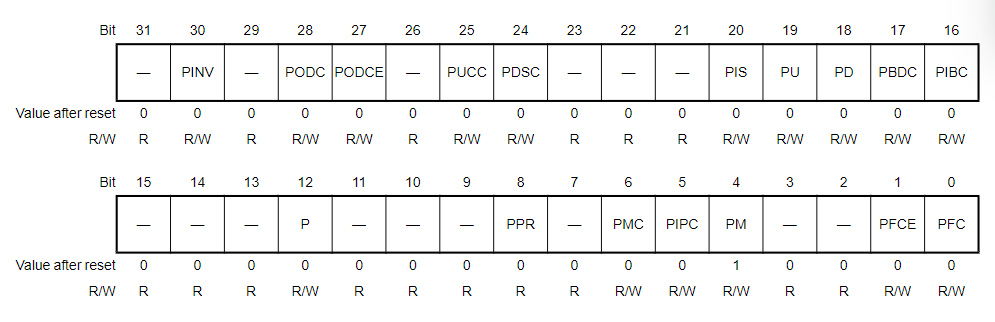

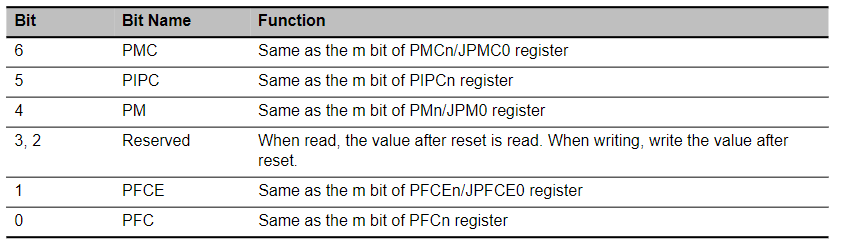

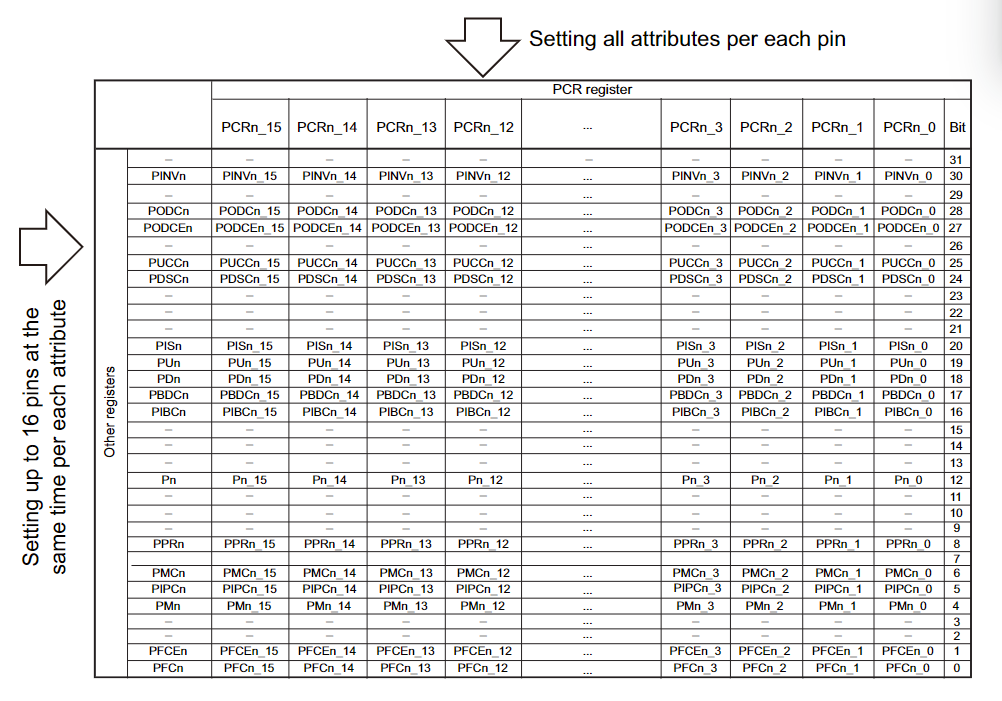

- PCRn_m/JPCR0_m — Port Control Register

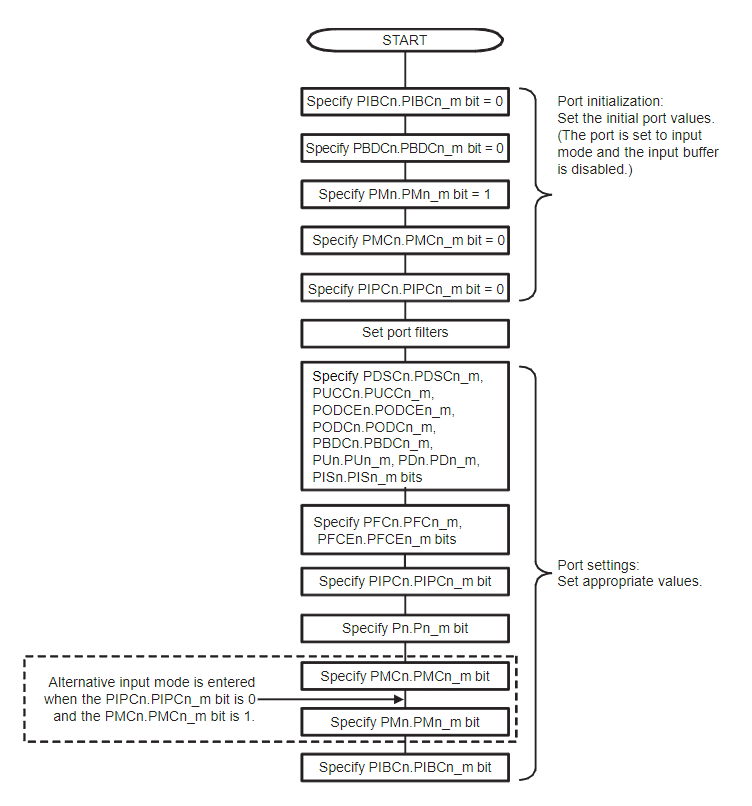

- 端口设置流程示例

- 噪声滤波与边沿检测

- A型模拟滤波器的输入引脚

- 包含B型模拟滤波器的输入引脚

- C型数字滤波器的输入引脚

- D型数字滤波器的输入引脚

- E型模拟滤波器和数字滤波器的组合输入引脚

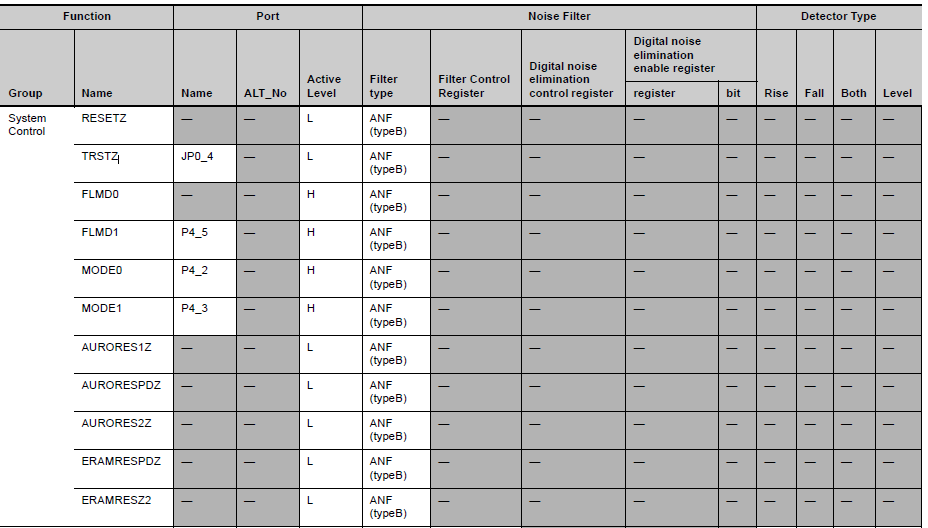

- 噪声滤波器分配

- 噪声滤波寄存器

- DNFAnEN Register List

- 端口噪声滤波和边缘/电平检测的描述

- Analog filters

- 数字滤波

- 滤波器控制寄存器

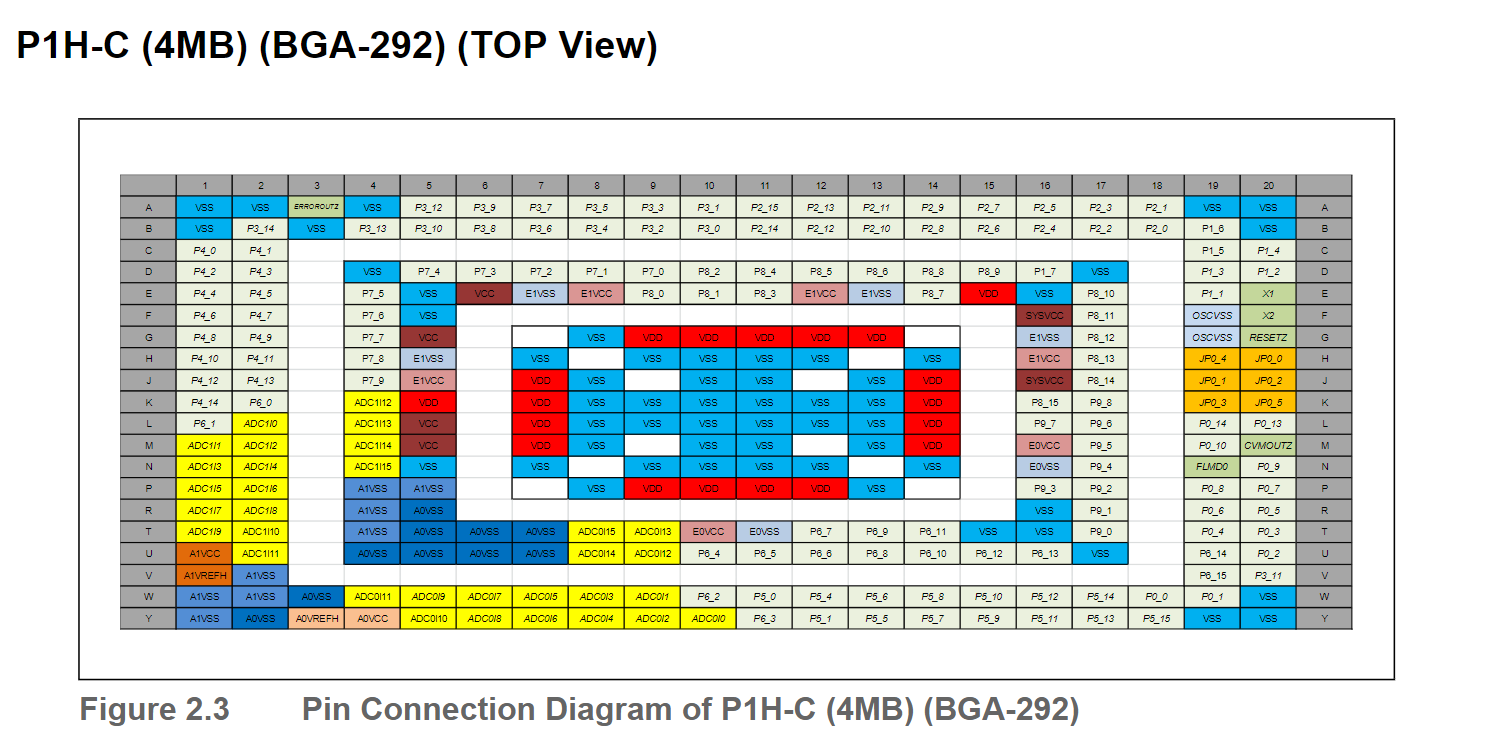

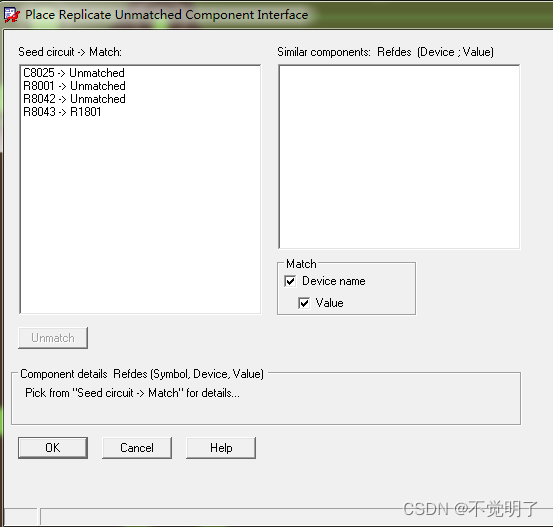

Pin Connection Diagrams

此处只截了P1H-C(4MB)的,其他的可以参考使用手册

术语定义

本节中使用了以下术语:

引脚 指的是物理引脚。每个引脚都有一个唯一的引脚编号。一个引脚可以在几种模式下使用。每个引脚都有一个反映其功能的名称,这是由所选模式决定的。PIN Num指的是A-P+1-14

端口组 表示一组引脚。一个特定端口组的所有引脚都由同一个端口控制寄存器控制。RH850/P1x-C提供以下端口组,由下表中的数字表示

P0_7表示端口组0的端口7。 它被称为 port P0_7

Pin List

见手册P64

Port Overview

本文件定义了标准的 “端口控制逻辑”,包括IO缓冲区之间的接口。作为端口号的每个参数都为RH850/P1x-C产品进行了优化。

Introduction

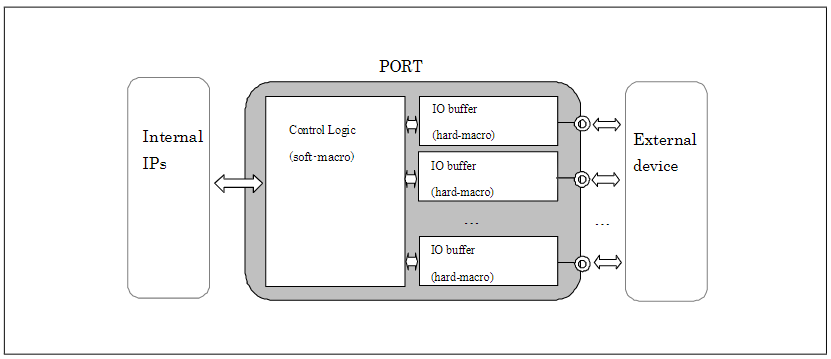

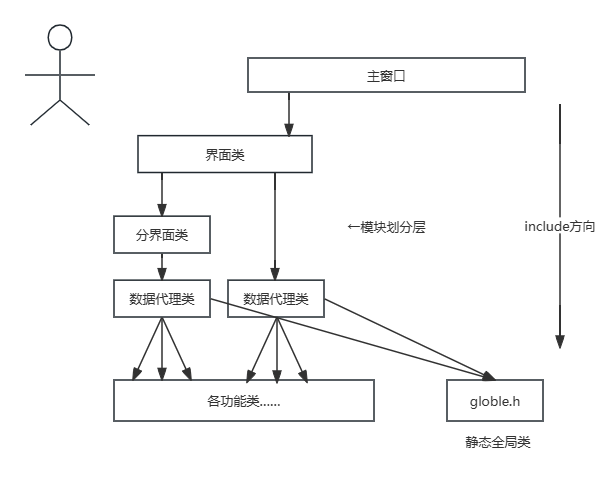

微控制器的端口是外部设备和微机内部资源(IP)之间的一个接口。从设计的角度来看,一个端口通常由IO缓冲器和控制逻辑组成,如下图所示

Functional Overview

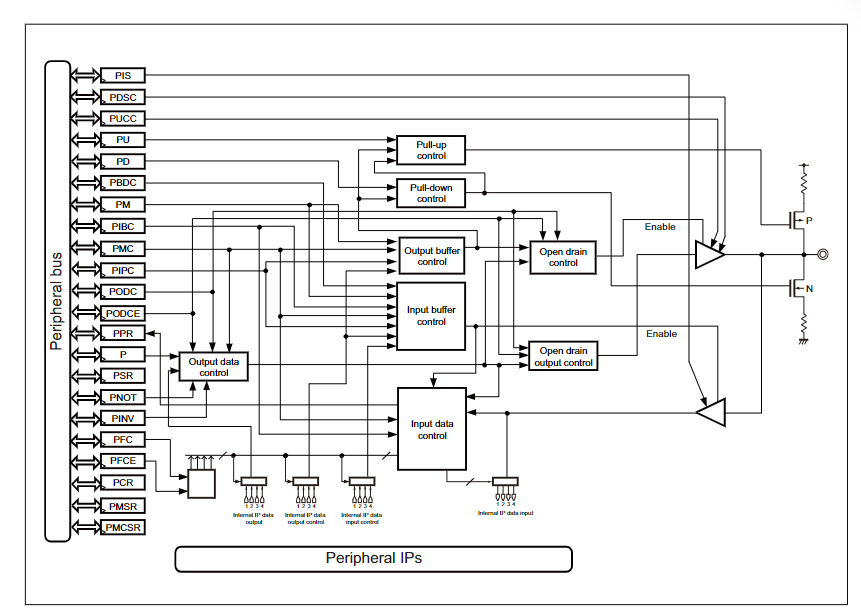

有效的微控制器复位会使几乎所有的端口引脚都处于Hi-Z状态。对于例外情况,请参考表2.2,引脚状态。在RESETZ释放后,SW可以定义不同的状态。在相关的写访问的总线周期结束后(<1us),SW的所有状态变化都会立即生效。当一个端口引脚被配置为数字输入时,可以将其配置为上拉、下拉或不上拉。通过设置上拉寄存器(PUn.PUn_m = 1)使输入引脚的内部上拉生效,通过设置下拉寄存器(PDn.PDn_m = 1)使下拉生效。如果一个引脚被配置为同时连接了内部上拉电阻(PUn.PUn_m = 1)和下拉电阻(PDn.PDn_m = 1),则自动选择下拉电阻而不连接上拉电阻。如果一个输入端口引脚不需要上拉或下拉,则取消选择上拉和下拉寄存器(PUn.PUn_m = 0,PDn.PDn_m = 0)

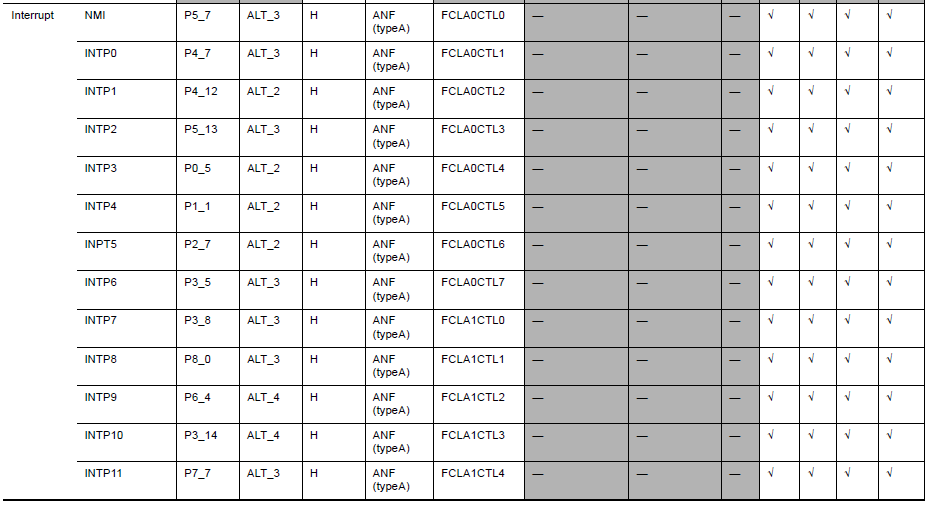

外部中断引脚: 器件中提供了可屏蔽的外部中断引脚(INTP0至INTPn)和一个不可屏蔽的中断引脚(NMI)。对于外部中断,通过设置外部中断控制寄存器中的外部中断检测方法选择位,可以为每个引脚选择下降沿、上升沿或两个边沿。此外,在中断控制寄存器(IC0到ICn)中可以为每个引脚设置中断优先级0到15。当边缘检测被选为中断检测方法时,通过INTPn引脚的变化来检测中断请求,并向INTC发送一个中断请求信号。四个外部中断可以产生DMA请求,更多细节见第6节,中断控制器(INTC)。

Port Category

(1) 数字端口

数字端口提供的功能包括数字IO和替代功能。例如,像定时器输出、串行通信等功能可以在这个端口上分配。外部总线接口也可以被分配。

(2) JTAG端口

JTAG端口提供了一些特殊功能。这个端口是标准化的,可以用作测试接口、调试接口和包括闪存编程接口的端口接口。调试接口和端口模式之间的切换是由OPBT2控制的。(见第32.12.1节,OPBT0–Option Byte 0)尽管任何端口功能都可以通过这个引脚实现,但是当这个引脚被用作调试接口时,它们不能被模拟。因此,我们建议不要把重要的用户功能分配给这个引脚

Operation Mode运行模式

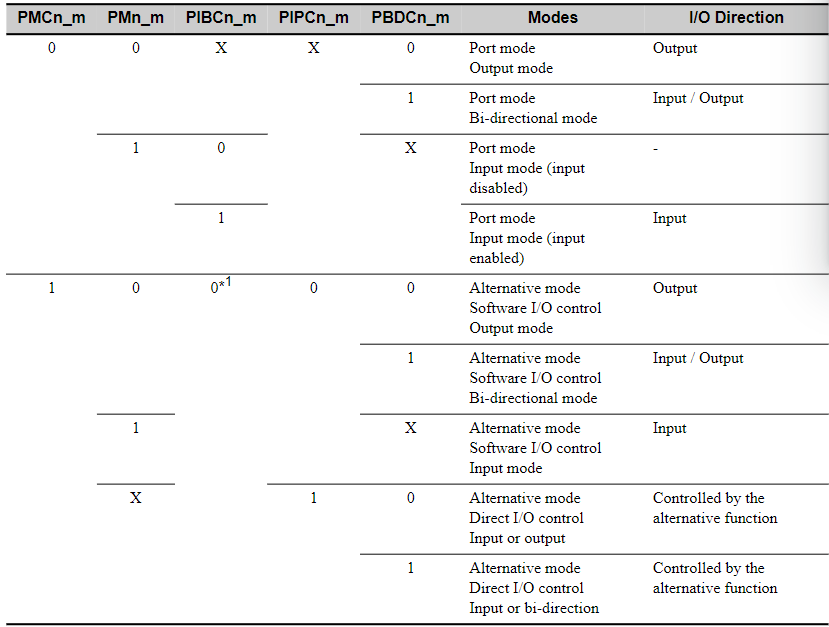

引脚可以在三种操作模式下工作。以下复用模式即表示除IO外的特殊功能。

- 端口模式(PMCn.PMCn_m位=0)

端口模式下的引脚作为通用的输入/输出引脚工作。输入/输出模式通过设置PMn.PMn_m位来选择。 - 复用模式软件I/O控制(PMCn.PMCn_m位=1,PIPCn.PIPCn_m位=0)

在这种模式下,引脚作为替代功能运行。通过设置PMn.PMn_m位来选择输入/输出模式。 - 复用模式直接I/O控制(PMCn.PMCn_m位=1,PIPCn.PIPCn_m位=1)

在这种模式下,各引脚作为复用功能运行。然而,与复用模式的软件I/O控制不同,输入/输出方向是由复用功能选择的。

以下是与操作模式和引脚I/O方向有关的寄存器效果。

- PMCn.PMCn_m bit 该位选择端口模式(PMCn_m = 0)或复用模式(PMCn_m = 1)。

- PMn.PMn_m位 当选择了端口模式(PMCn_m = 0)和复用模式软件I/O控制(PMCn_m = 1, PIPCn_m = 0)时,该位选择了输入(PMn_m = 1)或输出(PMn_m = 0) 。

- PIBCn.PIBCn_m位 该位在输入端口模式(PMCn_m = 0, PMn_m = 1)中禁用(PIBCn_m = 0)或启用(PIBCn_m = 1)输入缓冲器。如果是复用模式,该位必须始终设置为0。

- PIPCn.PIPCn_m位 该位选择复用模式的软件I/O控制或复用模式的直接I/O控制。

- PBDCn.PBDCn_m 位 在输出模式或复用功能启用的输出中,当该位被设置为 1 时,引脚进入双向模式

复用功能选择

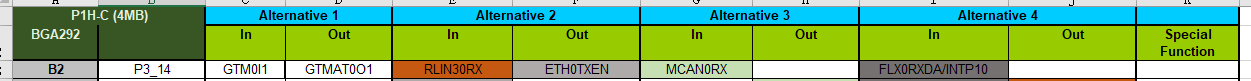

以P3_14为例:

如果我们想选择为MCAN0RX功能,则需要将PFCEn_[15:0]配置为1,PFCn_[15-0]配置为0,PMn_[15:0]配置为1

Port Function

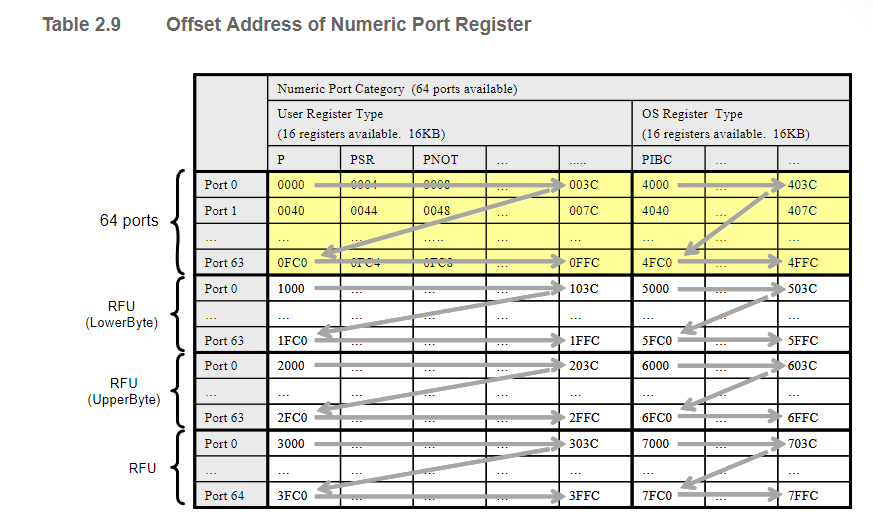

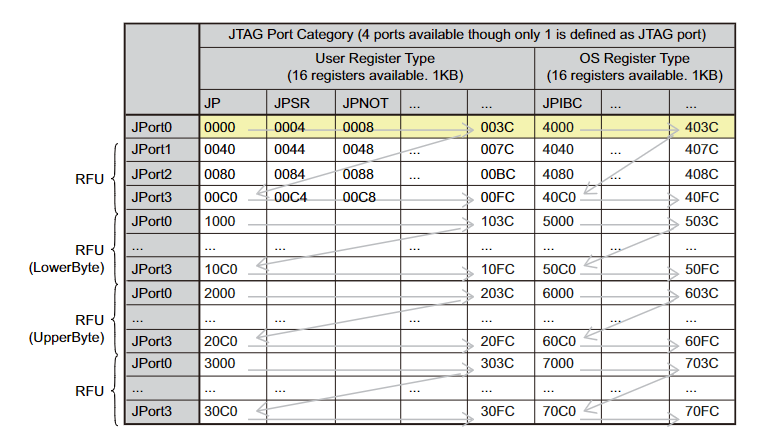

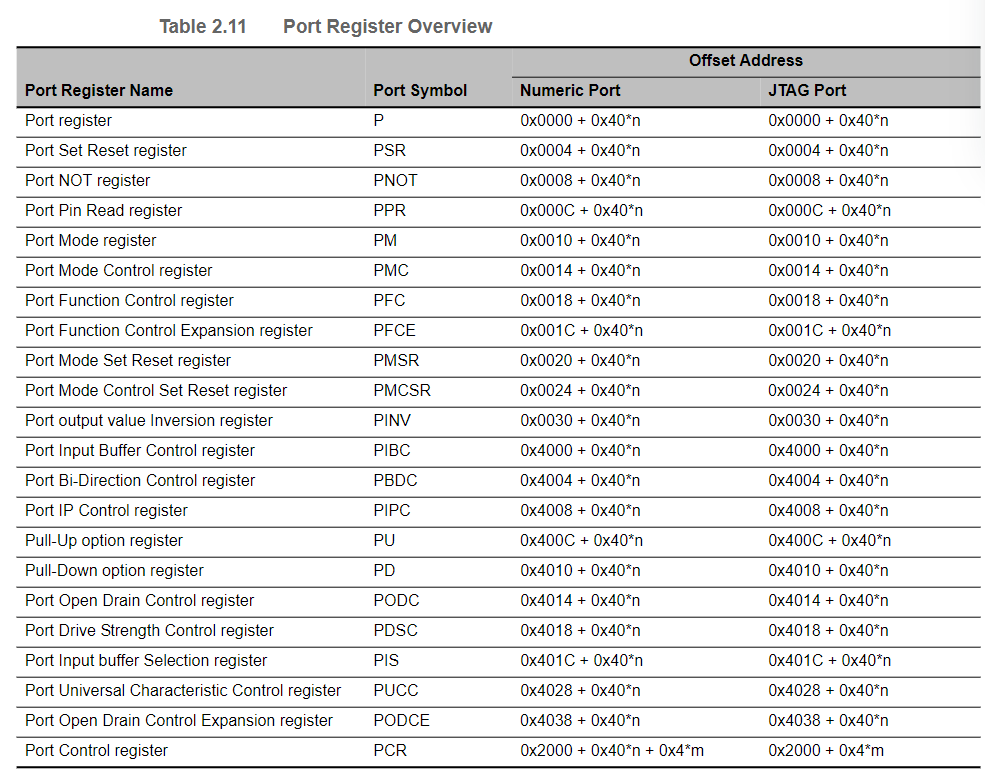

寄存器地址映射

Numeric Port Register

JTAG Port Register

Port寄存器描述

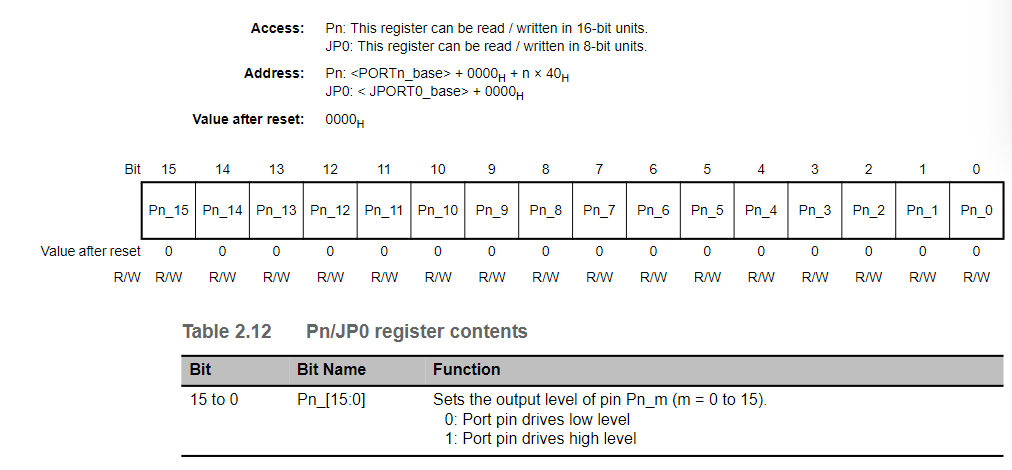

Pn/JP0 — Port Register

该寄存器定义了端口输出模式的端口引脚输出电平

- 读取Pn返回的寄存器值与其他寄存器设置无关。

- 在下列情况下,该寄存器位上的值会反映到引脚电平上。情况:端口模式(PMCn_m = 0)和输出模式(PMn_m = 0)

PPRn/JPPR0 — Port Pin Read Register

该寄存器反映了输入缓冲器处于激活状态时的实际引脚电平

PMn/JPM0 — Port Mode Register

该寄存器选择引脚方向为输入或输出。

PMCn/JPMC0 — Port Mode Control Register

这个寄存器指定端口组n的各个引脚是在端口模式还是在复用模式

为0时为端口模式

PFCn — Port Function Control Register

该寄存器在控制模式下与PMn一起选择复用的外设功能(PMCn = 1)

PFCEn/JPFCE0 — Port Function Control Expansion Register

复用模式扩展寄存器

注1. 输出功能可能被分配到一个以上的端口,以便平行使用。各个端口的输出时间可能不同,因为它取决于缓冲器的选择和引脚的连接。

注2. 只激活一个单一的引脚到一个给定的复用输入功能。不要同时在多个引脚上激活一个输入功能。[例如]MTTCAN0RX被分配到该设备的以下引脚。当选择P5_15的第2个输入复用功能时,禁止使用P2_6的第3个输入复用功能和P4_5的第3个输入复用功能。

- P2_6(第3个输入复用功能)

- P4_5(第3个输入复用功能)

- P5_15(第2个输入复用功能)

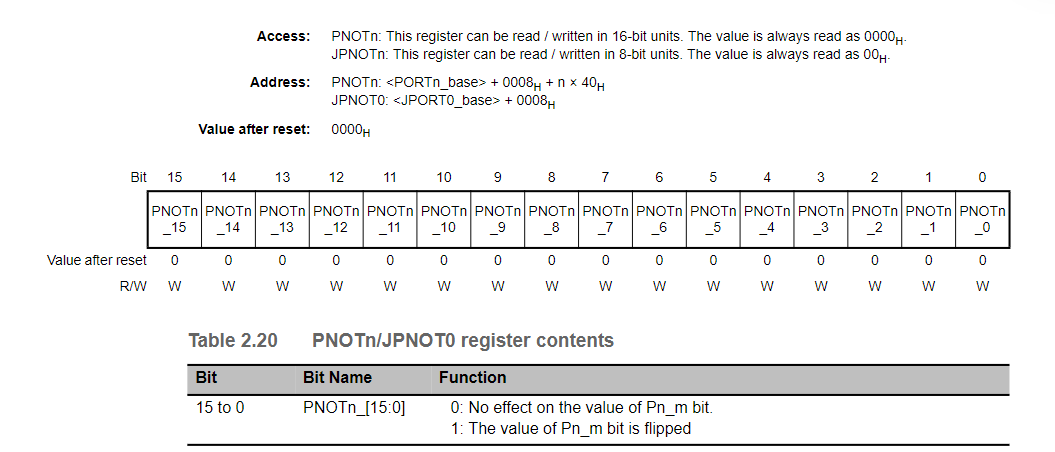

PNOTn/JPNOT0 — Port Not Register

该寄存器提供了一种翻转Pn寄存器位值的方法。如果PNOTn寄存器被写入相应的位值为1,则Pn寄存器的位被翻转

只有对该寄存器的写操作是有用的。读取PNOTn寄存器总是返回0。

PSRn/JPSR0 — Port Set/Reset Register

该寄存器提供了一种在Pn寄存器上写/读数据的替代方法

PSRn的高16位作为一个掩码,指定Pn.Pn_m的值是否被PSRn的低16位中的相应位设置。

读取 PSRn_[31:16] 位的值总为0

读取 PSRn_[15:0] 位的值时返回Pn_[15:0]的值

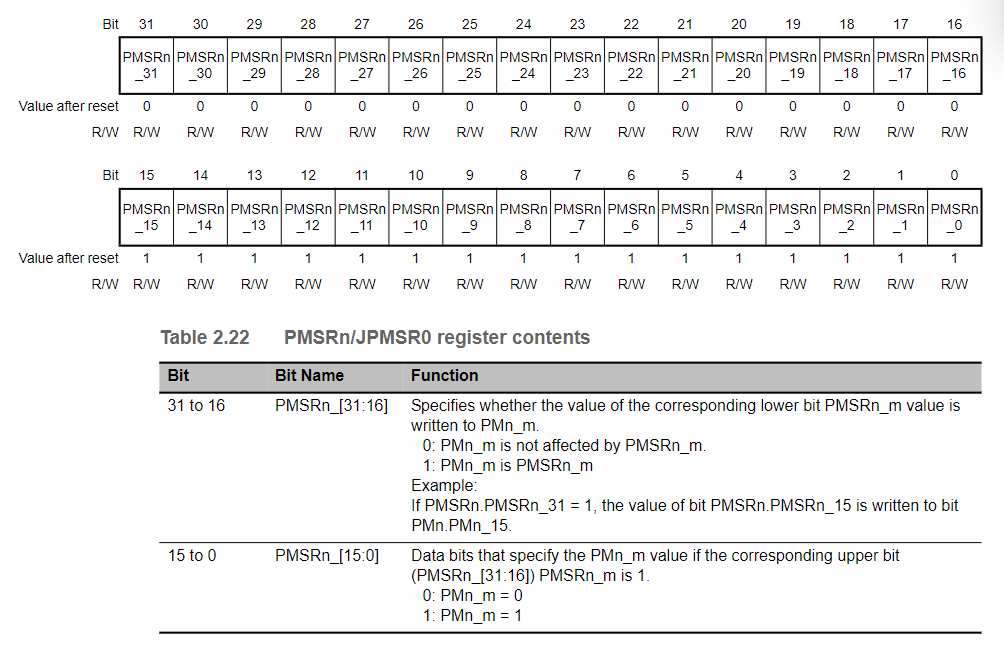

PMSRn/JPMSR0 — Port Mode Set/Reset Register

跟上面的类似,只是控制的是PMn寄存器的位

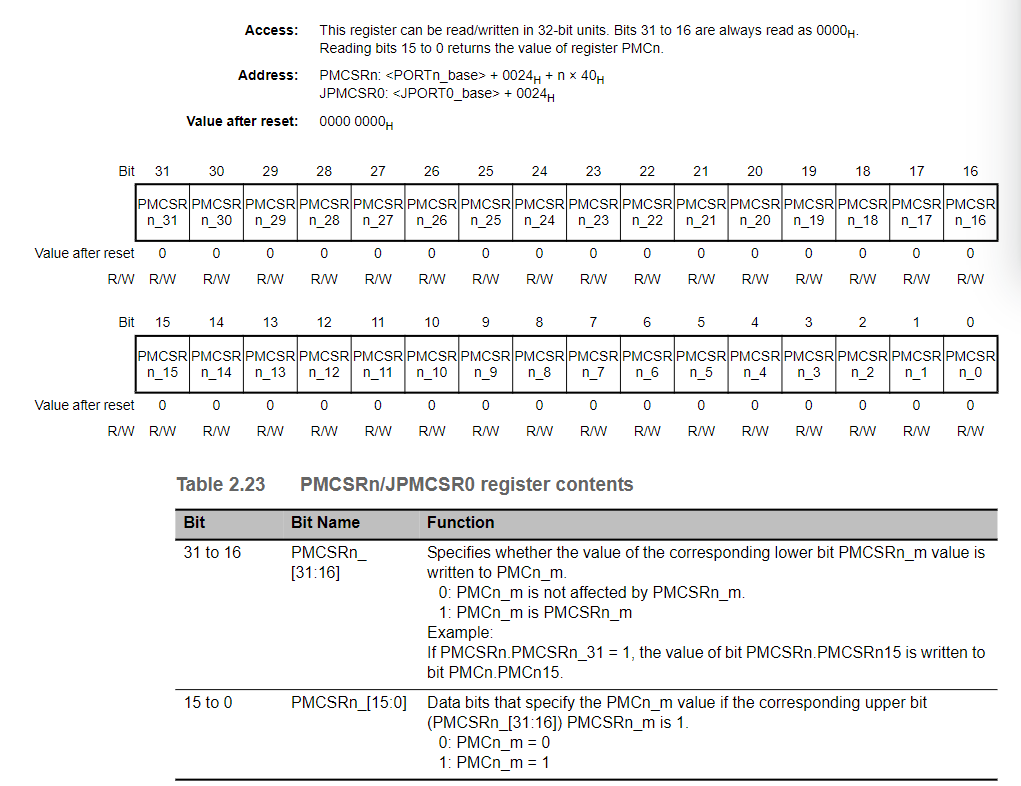

PMCSRn/JPMCSR0 — Port Mode Control Set/Reset Register

跟上面的类似,只是控制的是PMCn寄存器的位

PINVn/JPINV0 — Port output value Inversion Register

将输出值反转

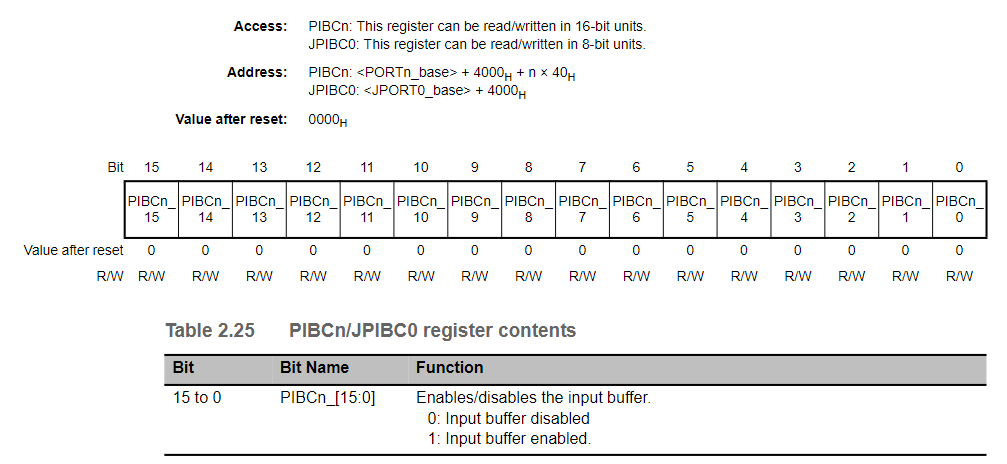

PIBCn/JPIBC0 — Port Input Buffer Control Register

该寄存器作为端口模式下启用/禁用端口引脚输入缓冲器的因素之一(PMC=0)

- 要启用端口引脚的输入缓冲器,必须在端口模式下通过PM=1将IO方向设置为输入模式(PMC=0)。

- 通过保持该寄存器的复位值为0,即使引脚处于中间电压,端口引脚的输入缓冲器也不会消耗电流。当输入缓冲器被禁用时,在端口模式下,即使引脚的电平为Hi-Z,也不会有通电电流。因此,该引脚不需要从外部固定为高或低电平。

- 在这个寄存器设置为1的端口模式(PMC=0)下,外围宏的值是固定的。

- 在 "软件I/O控制终止功能输入 "模式(PMC=1,PM=1,PIPC=0)下,这个寄存器的位必须被设置为0。

PBDCn/JPBDC0 — Port Bi-Direction Control Register

该寄存器启用输入缓冲器,并将端口设置为双向模式。在双向模式下,PPRn.PPRn_m可以读取Pn_m引脚的电平

PIPCn — Port IP Control Register

该寄存器指定引脚Pn_m的I/O方向是由端口模式寄存器PMn.PMn_m控制还是由复用功能控制。如果引脚Pn_m工作在复用模式(PMCn.PMCn_m = 1),并且复用功能需要直接控制I/O方向,那么PIPCn.PIPCn_m也必须被设置为1。这就把I/O控制权转移给了复用功能,并覆盖了PMn.PMn_m的设置。需要直接控制I/O方向的替代功能列表见表2.28。当选择这些复用功能时,PIPC必须被设置为1

PUn/JPU0 — Pull-Up Option Register

该寄存器指定上拉电阻是否连接到输入引脚上。

- 如果一个引脚被配置为同时连接了内部上拉电阻(PUn.PUn_m = 1)和下拉电阻(PDn.PDn_m = 1),则自动选择下拉电阻而不连接上拉电阻。

- 当引脚工作在输出模式时,上拉电阻没有作用。

- JTAG 上拉选项寄存器(JPU0)的控制位是 JPU0_ [7:0]

PDn/JPD0 — Pull-down option Register

该寄存器指定是否将一个内部下拉电阻连接到输入引脚

- 如果一个引脚被配置为同时连接了内部上拉电阻(PUn.PUn_m = 1)和下拉电阻(PDn.PDn_m = 1),则自动选择下拉电阻而不连接上拉电阻。

- 当引脚工作在输出模式时,内部下拉电阻没有作用。

- JTAG 下拉选项寄存器(JPD0)的控制位是** JPD0**_[7:0]

PODCn/JPODC0 — Port Open Drain Control Register

该寄存器选择推挽式或开漏式作为输出缓冲功能

PODCEn/JPODCE0 — Port Open Drain Control Expansion Register

该寄存器与PODCn一起选择模拟的P通道开漏的模式

PDSCn/JPDSC0 — Port drive strength control register

这个寄存器指定了端口引脚的输出驱动强度。这个功能也与输出缓冲器的快速模式(高驱动强度)和慢速模式(低驱动强度)有关

PUCCn/JPUCC0 — Port Universal Characteristic Control Register

端口通用特性控制寄存器

该寄存器扩展了输出缓冲器的特性选择能力。如果它与PDSC寄存器一起使用,最多可以有4个特性选择

PISn/JPIS0 — Port input buffer selection register

该寄存器定义了输入缓存区的特性

PCRn_m/JPCR0_m — Port Control Register

通过该寄存器,可以访问每个端口组的寄存器,并通过1个PCR寄存器的设置指定各个引脚的功能

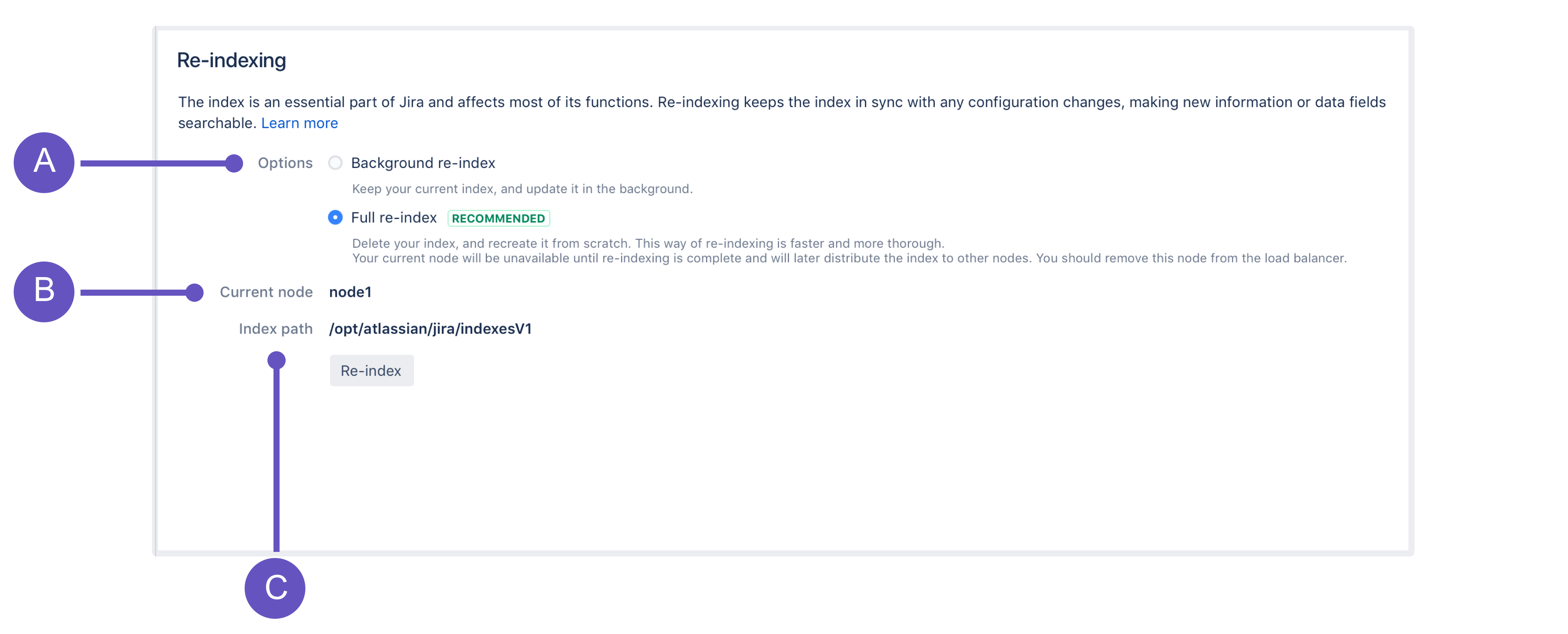

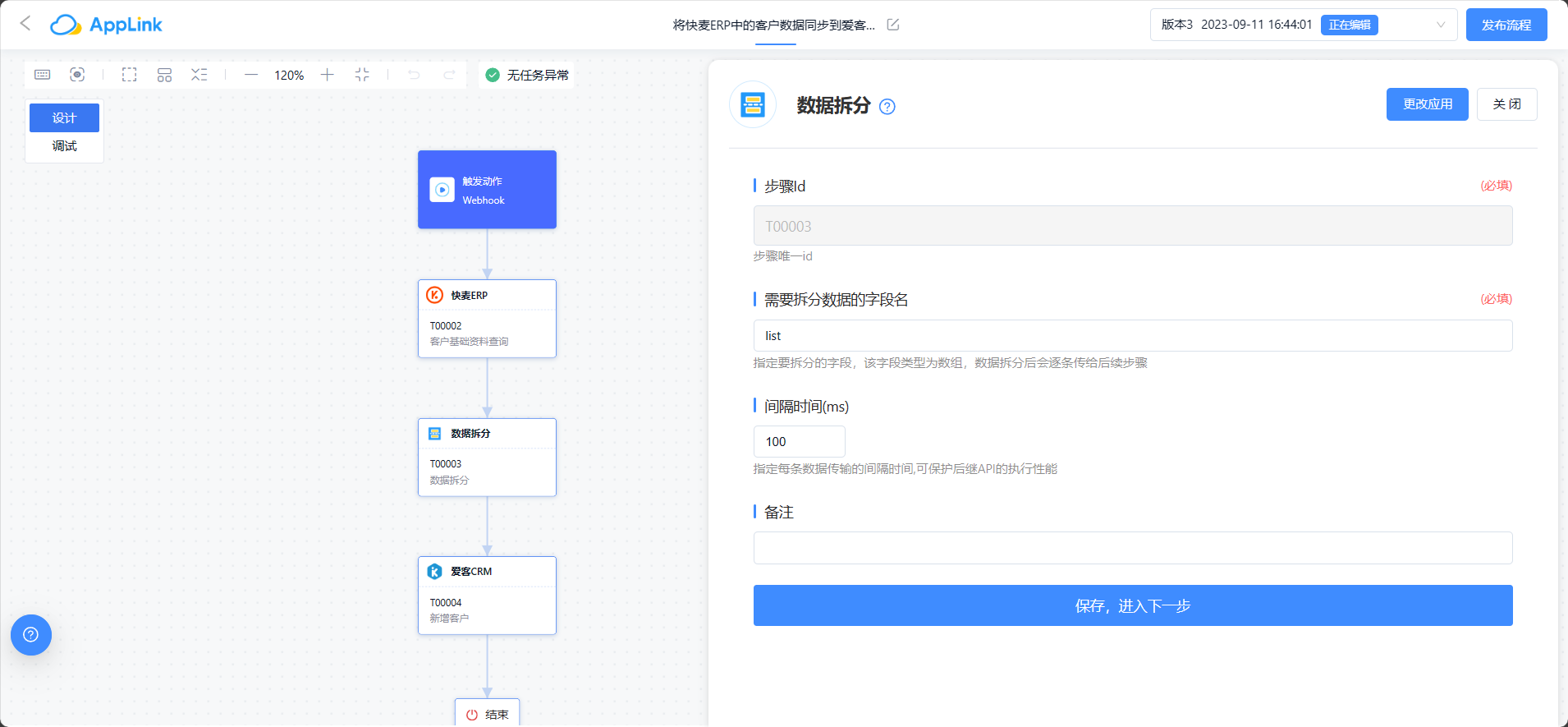

端口设置流程示例

噪声滤波与边沿检测

一些引脚的输入信号通过滤波器来消除噪声和小故障。该设备支持模拟和数字滤波器。它还支持在信号通过滤波器后进行边缘和电平检测的功能。本节的第一部分概述了配备滤波器和滤波器类型的端口输入信号,噪声滤波器和边缘检测控制寄存器和位,以及寄存器地址。

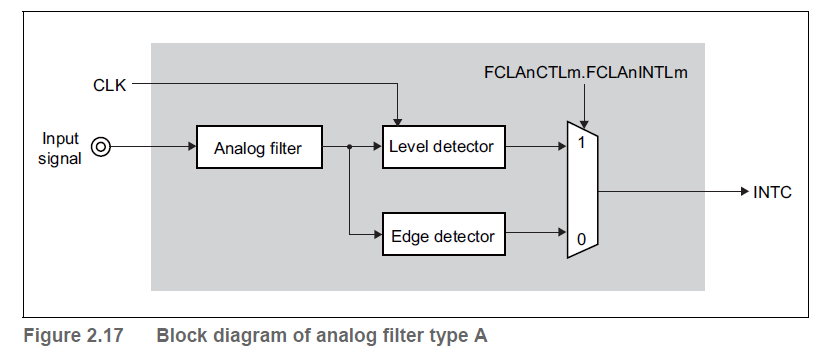

A型模拟滤波器的输入引脚

A型模拟滤波器的输入引脚包含模拟滤波器和边缘/电平检测功能。

边缘/电平检测由以下寄存器控制。

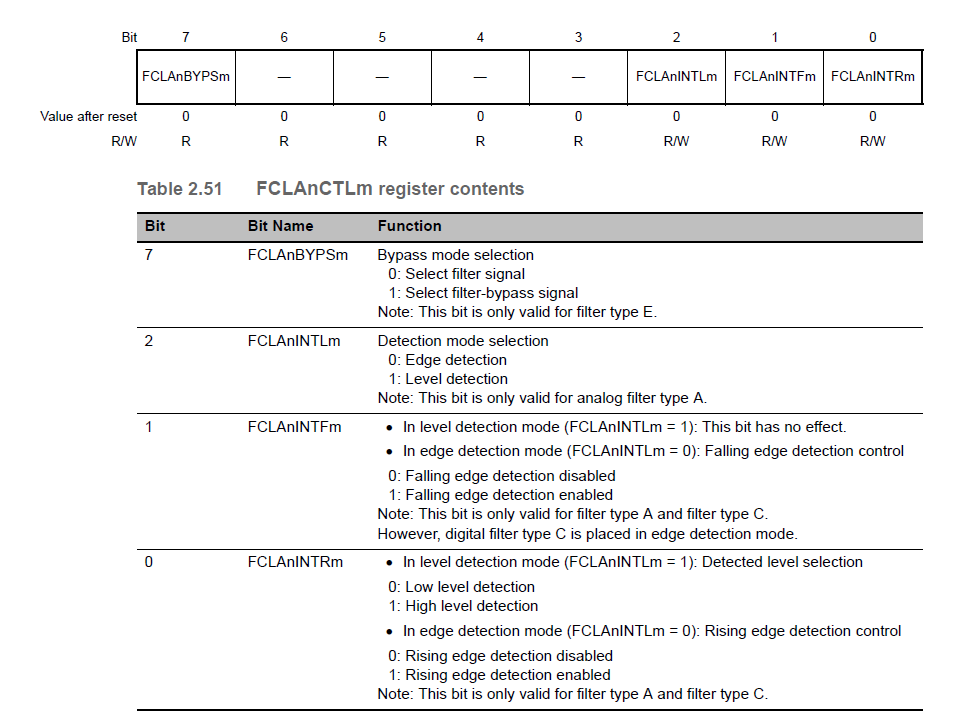

•滤波器控制寄存器FCLAnCTLm (n = 0至6,m = 0至7)

为包含模拟滤波器的端口中的每个引脚提供专用FCLAnCTLm寄存器

包含B型模拟滤波器的输入引脚

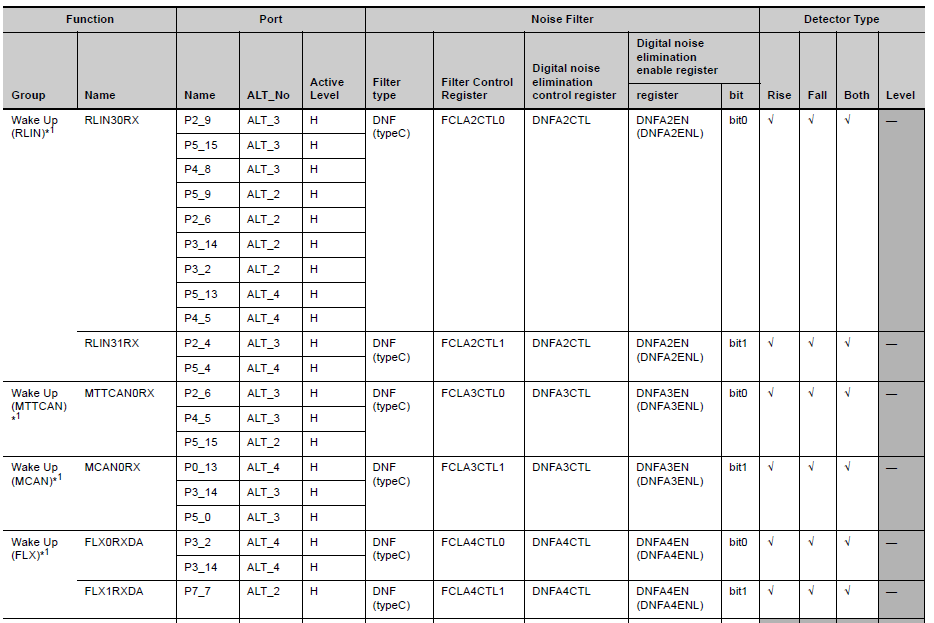

C型数字滤波器的输入引脚

C型数字滤波器的输入引脚包含数字滤波器和边缘检测功能。数字滤波器和边缘检测由以下寄存器控制。

•滤波器控制寄存器FCLAnCTLm (m = 0)

每个带数字滤波器的端口都有一个特殊的FCLAnCTLm寄存器。

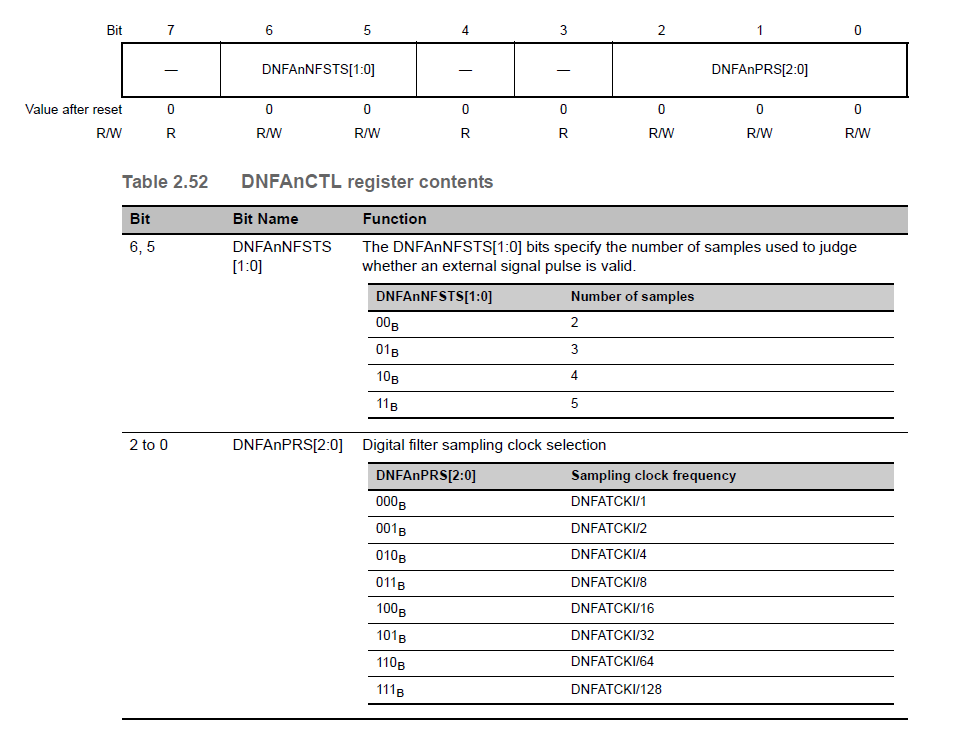

•数字消噪控制寄存器DNFAnCTL

每个DNFAnCTL控制寄存器控制每组三个输入信号的数字滤波器处理。

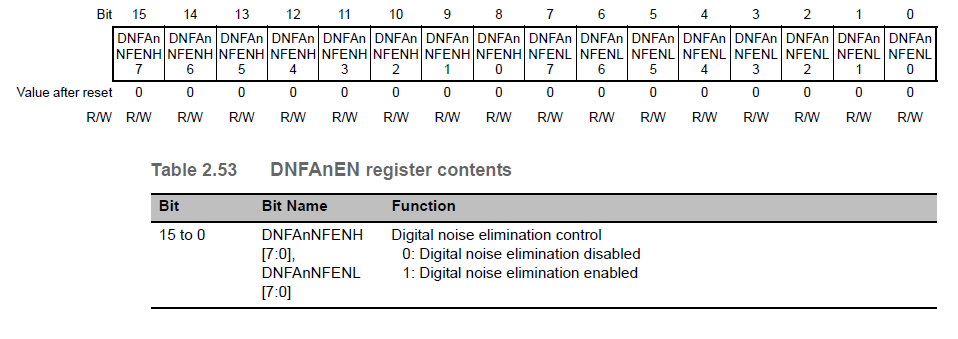

•数字噪声消除使能寄存器DNFAnEN

DNFAnEN中DNFAnNFENL[2:0]位的设置使能或使能数字噪声消除

采用C型数字滤波器的输入引脚尚未确定

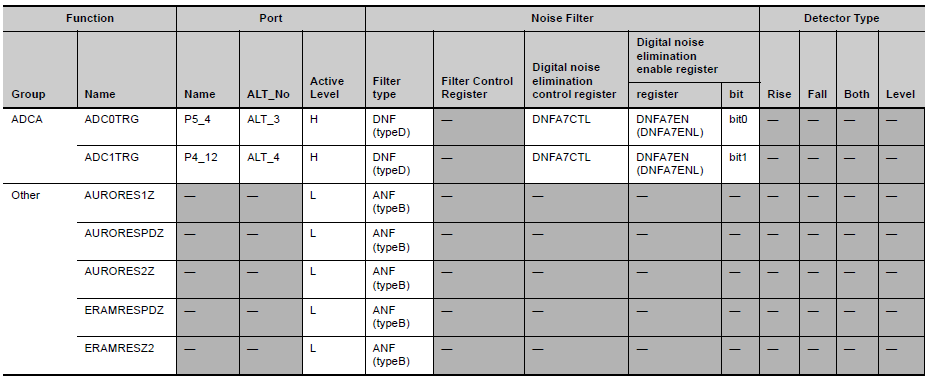

D型数字滤波器的输入引脚

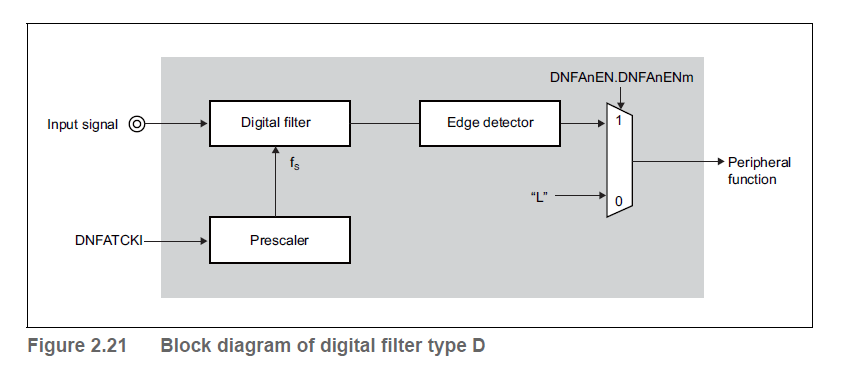

D型数字滤波器的输入引脚包含一个数字滤波器,没有边缘检测功能。

数字滤波器由与C型相同的寄存器控制。

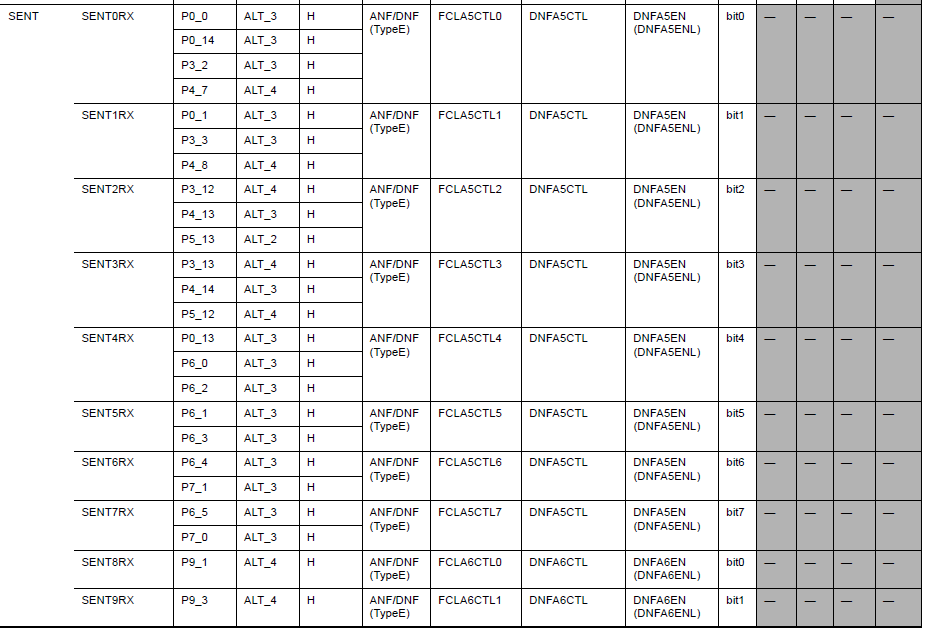

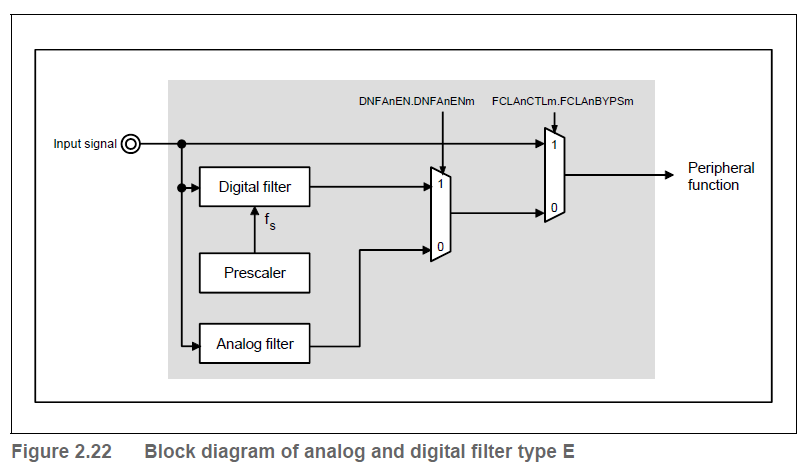

E型模拟滤波器和数字滤波器的组合输入引脚

E型滤波器的输入引脚包含一个数字滤波器和一个没有边缘检测功能的模拟滤波器。模拟滤波器和数字滤波器由与A型和C型相同的寄存器控制。

噪声滤波器分配

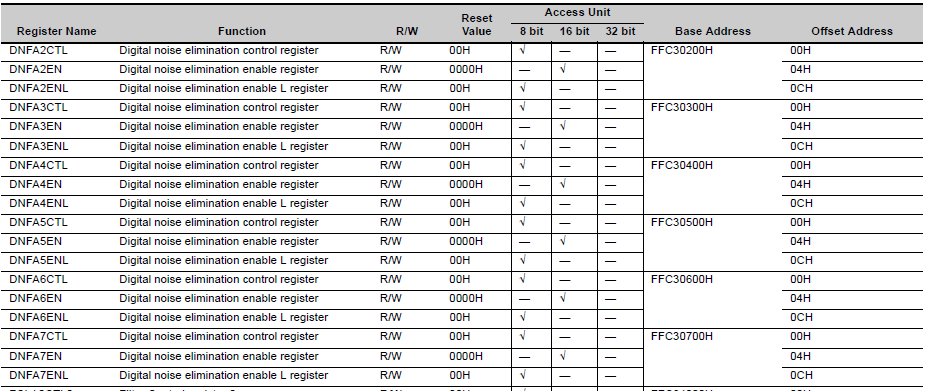

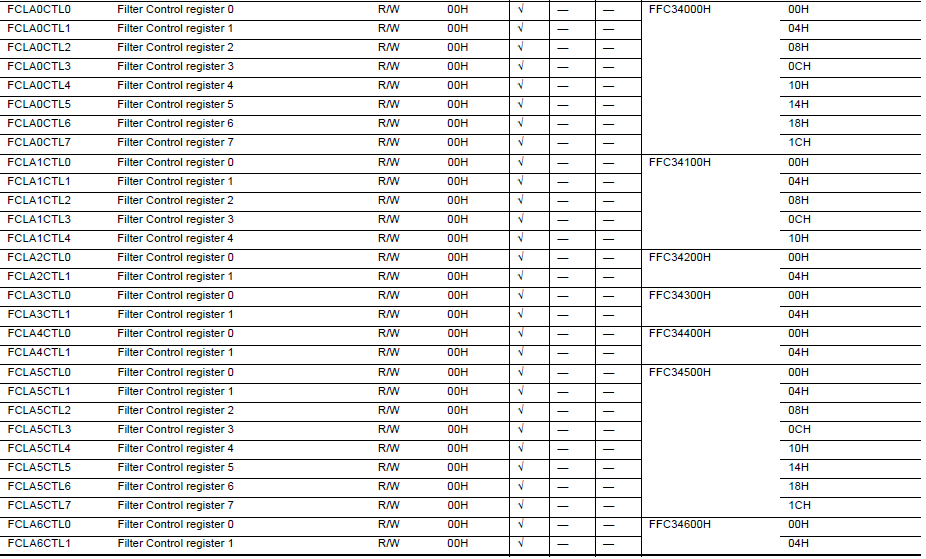

噪声滤波寄存器

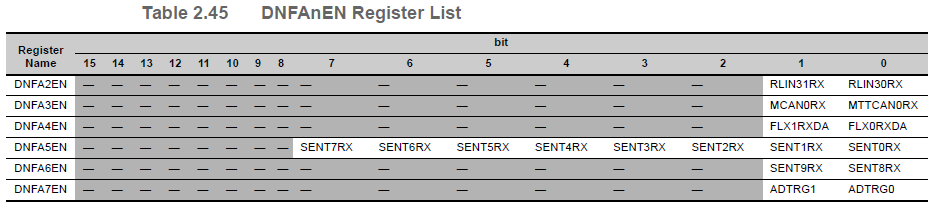

DNFAnEN Register List

端口噪声滤波和边缘/电平检测的描述

根据待滤波信号的应用,外部输入信号通过不同类型的滤波器。

(1)模拟滤波器

模拟滤波器具有固定的特性。

•A型:具有边缘检测或电平检测的模拟滤波器。

用于外部中断信号。

•B型:模拟滤波器。

用于外部RESETZ输入和模式信号。

(2)数字滤波器

数字滤波器的特性可以调整,以适应应用。

•C型:带边缘检测的数字滤波器。

用于唤醒信号。

•D型:无边缘检测的数字滤波器。

用于ADC触发输入信号。

(3)数字和模拟滤波器

•E型:具有边缘检测的模拟和数字滤波器。

用于Sent接收信号。

Analog filters

模拟滤波器特性

模拟滤波器的特性以及电平和边缘检测器的特性在第35节,电气规范。

模拟滤波器控制寄存器

对于每个输入信号,配备一个模拟滤波器,一个专用的控制寄存器FCLAnCTLm和一个控制寄存器在每个外设宏。

(1) A型模拟滤波器

A型模拟滤波器的框图如下所示。

将外部信号通过滤波器消除噪声和尖峰后,滤波器根据是否检测到事件产生输出信号;即是否检测到指定的电平,或者是否发生电平(边缘)的更改。

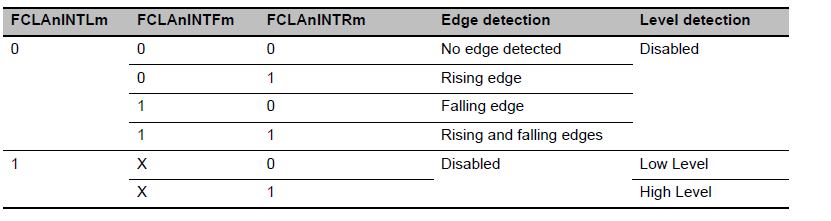

是否检测电平或边缘是由控制位FCLAnCTLm.FCLAnINTLm选择的。

•FCLAnCTLm = 0:边缘检测

FCLAnCTLm.FCLAnINTRm和FCLAnCTLm.FCLAnINTFm bits参数来指定是检测上升沿还是下降沿

•FCLAnINTLm = 1:电平检测

检测高电平或低电平可以通过设置FCLAnCTLm.FCLAnINTRm来指定。

对应关系见下表:

(2) B型模拟滤波器

B型模拟滤波器的框图如下所示

发生的信号总是经过模拟滤波器的信号

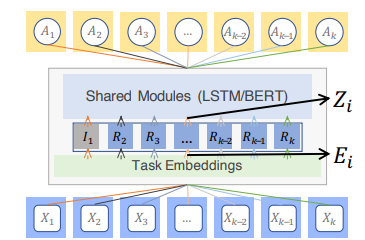

数字滤波

数字滤波器特性

数字滤波器允许调整滤波器特性,以满足应用的需要。

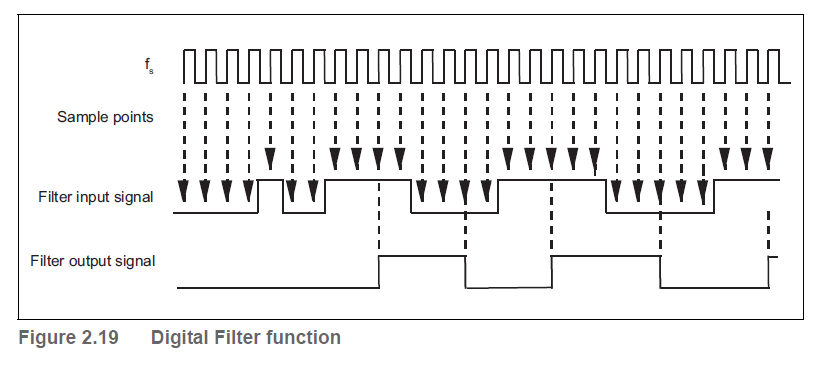

以采样频率fs对输入信号进行采样。

如果指定数量的连续采样产生相同的(高或低)电平,则判断信号电平有效,并相应地设置滤波器输出信号。

如果在指定的采样数(相同电平的采样s)内检测到外部信号电平变化,则判断信号电平为噪声-或尖峰-并且滤波器输出信号不改变。

这两个参数都可以指定:

•DNFAnCTL。DNFAnPRS[2:0]允许选择采样频率为fs = fDNFATCKI / 2^DNFAnPRS[2:0],其中fDNFATCKI为DNFATCKI时钟的频率。

•DNFAnCTL。DNFAnNFSTS[1:0]决定同电平样本(2 ~ 5)的个数s:

外部信号脉冲,短于

DNFAnNFSTS[1:0] × 1/ fs总是被抑制。

外部信号脉冲,长于

(DNFAnNFSTS[1:0] + 1) × 1/ fs总是被判断为有效,并被传递到滤波器输出。

因此,外部信号脉冲的范围

DNFAnNFSTS[1:0] × 1/ fs到(DNFAnNFSTS[1:0] + 1) × 1/ fs可能被抑制或判断为有效。

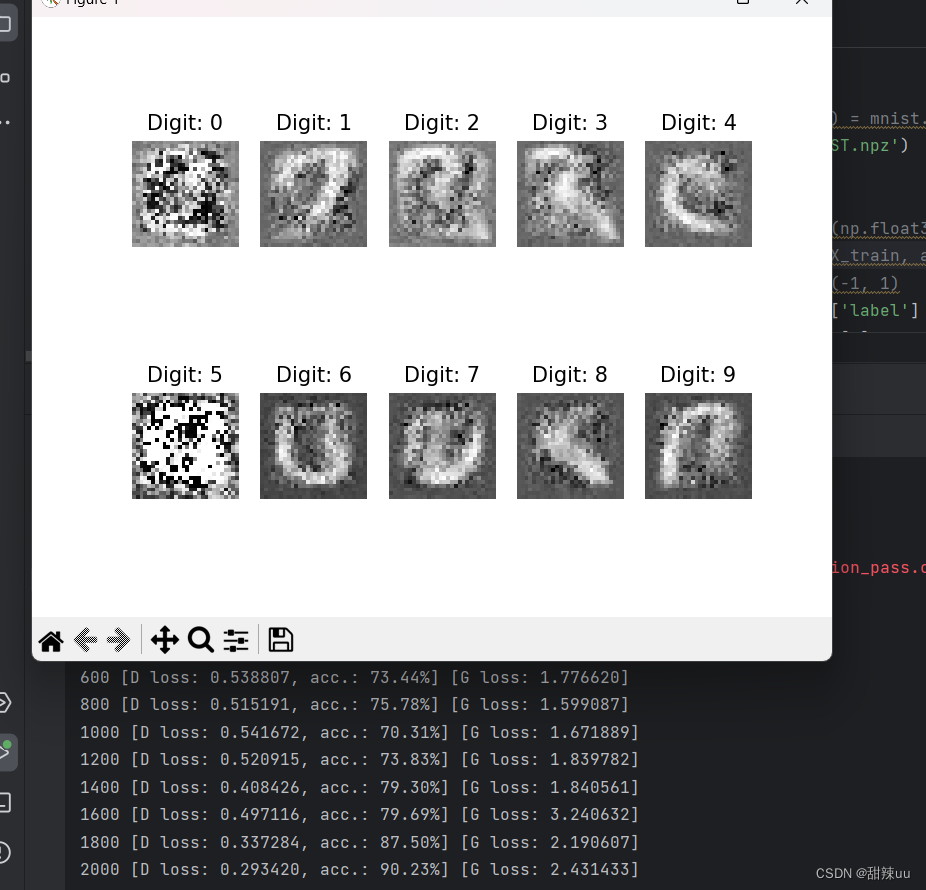

如下图所示,DNFAnNFSTS[1:0] = 01B,即s = 3个相同电平的样本。

数字滤波即只有在变化超过设定的次数之后才认为改变。

数字滤波器组

带数字滤波器的输入信号以多达16个信号的组排列。数字滤波器特性适用于整个组的滤波器。但是,可以为每个信号单独启用/禁用滤波器。

数字滤波器特性,DNFAnCTL.DNFAnPRS[2:0]和DNFAnNFSTS[1:0]适用于整个组的过滤器。

然而,每个信号的数字滤波器可以分别启用或禁用,通过DNFAnEN.DNFAnNFENm。

(1) C型数字滤波器

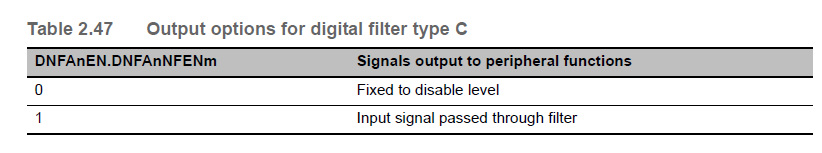

生成的信号取决于寄存器设置,如下表所示。

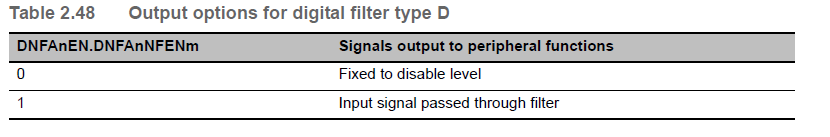

(2) D型数字滤波器

生成的信号取决于寄存器设置,如下表所示

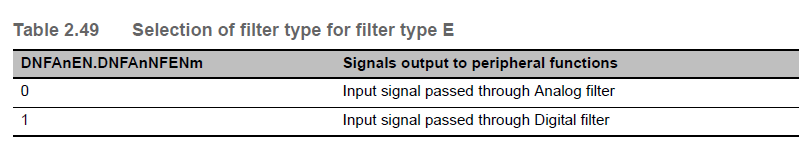

(3) E型模拟和数字滤波器

生成的信号取决于寄存器设置,如下表所示

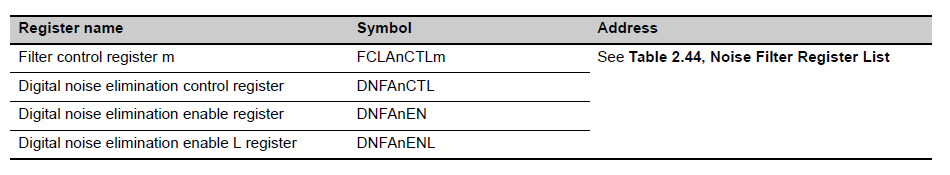

滤波器控制寄存器

模拟和数字滤波器由以下寄存器控制和操作:

(1) FCLAnCTLm — Filter Control Register

这个寄存器控制模拟和数字滤波器的操作。

由于模拟滤波器和数字滤波器的控制选项部分不同,因此分别提供寄存器描述。

FCLAnINTRm:在电平模式下,选择电平高低。在边沿模式下,选择上升沿检测是否使能。该位只在type A和type C下有效

FCLAnINTFm:在电平检测模式下,该位没有影响。在边沿检测模式下,选择下降沿检测是否使能。该位只在type A和type C下有效

FCLAnINTLm:选择检测模式。边沿检测或电平检测。只在type A下有效

FCLAnBYPSm:屏蔽滤波,为1时选择原始信号输出。只在type E下有效

注意:A型模拟滤波器:确保将第7位设置为0。

C型数字滤波器:确保将第7位和第2位设置为0。

(2) DNFAnCTL — Digital noise elimination control register

数字噪声消除控制寄存器

该寄存器用于指定数字消噪滤波器的滤波特性

DNFAnNFSTS[1:0]:配置连续采样的个数

DNFAnPRS[2:0]:配置采样时钟的分频因子

(3) DNFAnEN — Digital noise elimination enable register

控制数字滤波器使能寄存器

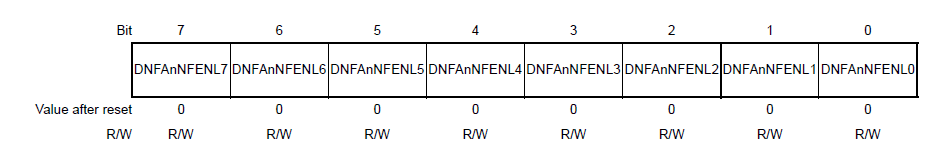

(4) DNFAnENL — Digital noise elimination enable L register

这个寄存器中的设置对应于DNFAnEN寄存器的8个低位的设置。

![合并两个有序链表[简单]](https://img-blog.csdnimg.cn/direct/c0753a9444ad47d1a1f9af1ce85ab8f7.png)

![[EndNote学习笔记] 导出库中文献的作者、标题、年份到Excel](https://img-blog.csdnimg.cn/1112a31e6ea040dd9ad83da0467cd684.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBAT25lQ2hlc3RudXQ=,size_11,color_FFFFFF,t_70,g_se,x_16)