目录

- 1 概述

- 2 示例平台

- 3 操作说明

- 4 注意事项

xilinx系列FPGA基于VIVADO的pin delay列表生成说明

1 概述

本文用于讲诉xilinx系列FPGA基于VIVADO的pin delay列表生成说明,以及一些注意事项,为FPGA设计人员探明道路。

Pin delay 即FPGA内部die到pin的延时数据。

2 示例平台

FPGA型号:xczu47dr-ffvg1517-2-i

Vivado版本:VIVADO 2022.2

3 操作说明

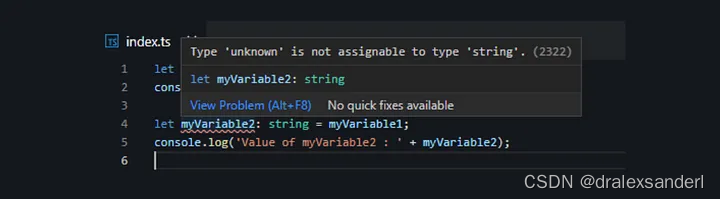

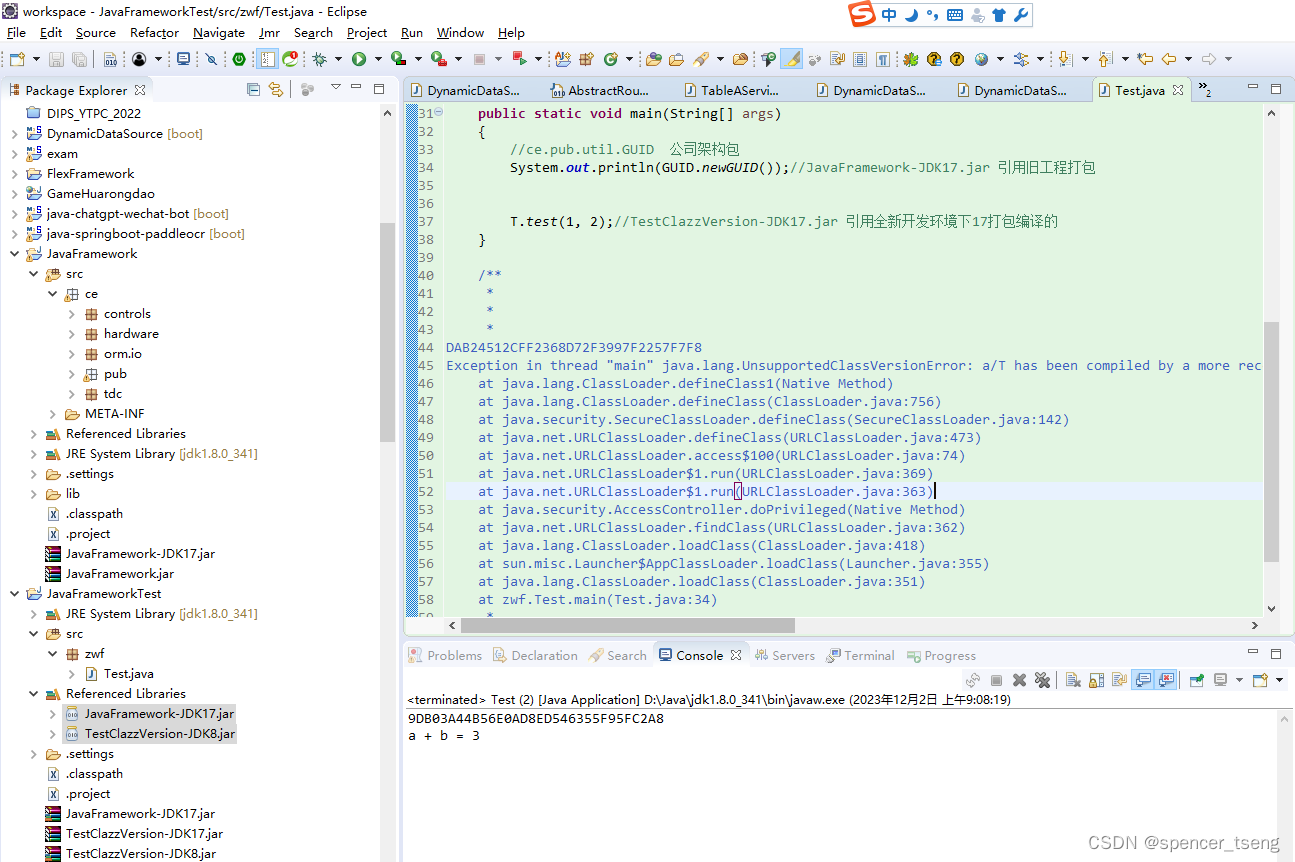

1)打开vivado 找到tcl console输入命令窗口,输入命令:

(link_design -part xczu47dr-ffvg1517-2-i)

回车进入下一步;

2)再次输入命令(write_csv fpga_pin_delay)回车进入下一步

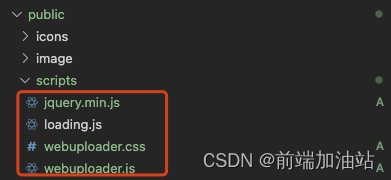

3)之后在vivado给出的路径下找到pin delay 文件,如下图所示:

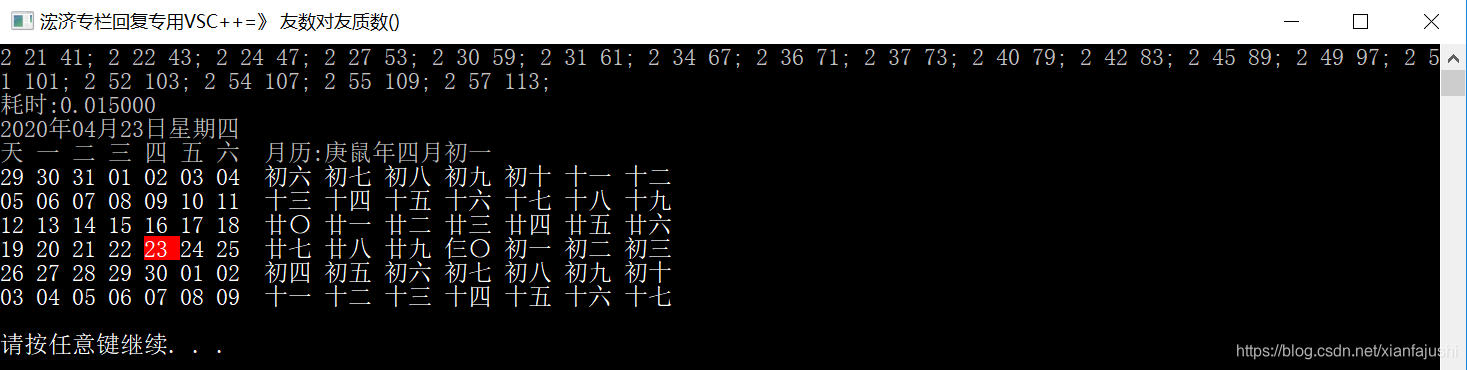

4)用excel打开pin delay 文件可以看到其格式如下所示:

4 注意事项

1) 命令(link_design –part FPGA型号)中的FPGA型号一定要对应vivado可以选择器件的型号,是全称;

2) 命令(write_csv 表格命名)中的表格命名随意,根据自己的需要即可;

3) 第一步打开的vivado界面一定要是一个空白的界面,不能在已有工程下打开;

4) 使用的vivado版本一定要能支持所生成FPGA型号,例如本例中的xczu47dr-ffvg1517-2-i在vivado2018.3及以下版本就不支持。