专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

题目要求检测a的序列,a为单bit输入,每个时刻可能具有不同的值,且并不是每一个数据都是有效的,需要根据data_valid信号进行判断。在状态转化过程中,当data_valid为0,表示该时刻是输入数据无效,应保持在当前状态。当data_valid为1,再根据输入数据是否匹配进行下一个状态的值。

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

input data_valid,

output reg match

);

reg [3:0] pstate, nstate ;

parameter idle = 4'd0,

s1_d0 = 4'd1,

s2_d01 = 4'd2,

s3_d011 = 4'd3,

s4_d0110 = 4'd4 ;

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) pstate <= idle ;

else pstate <= nstate ;

end

always @ (pstate or data or data_valid) begin

case (pstate)

idle :

if (data_valid && !data) nstate = s1_d0 ;

else nstate = idle ;

s1_d0 :

if (data_valid)

if (data) nstate = s2_d01 ;

else nstate = s1_d0 ;

else nstate = s1_d0 ;

s2_d01 :

if (data_valid)

if (data) nstate = s3_d011 ;

else nstate = s1_d0 ;

else

nstate = s2_d01 ;

s3_d011 :

if (data_valid)

if (!data) nstate = s4_d0110 ;

else nstate = idle ;

else

nstate = s3_d011 ;

s4_d0110 :

if (data_valid)

if (data) nstate = idle ;

else nstate = s1_d0 ;

else

nstate = idle ;

default :

nstate = idle ;

endcase

end

always @ (pstate or rst_n) begin

if (~rst_n) match <= 1'b0 ;

else if (pstate == s4_d0110)

match <= 1'b1 ;

else match <= 1'b0 ;

end

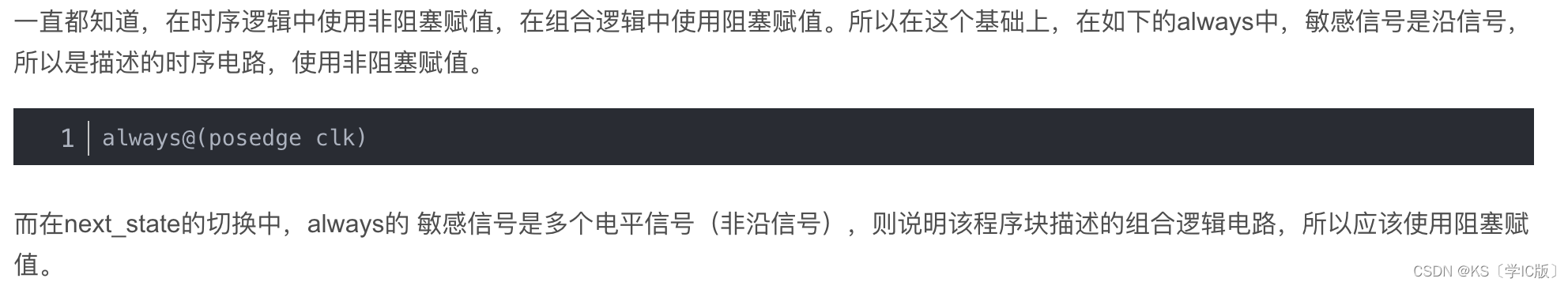

endmodule至于为什么要使用阻塞赋值原因: