利用有限状态机进行时序逻辑的设计

- 1,任务目的:

- 2,RTL代码,及原理框图

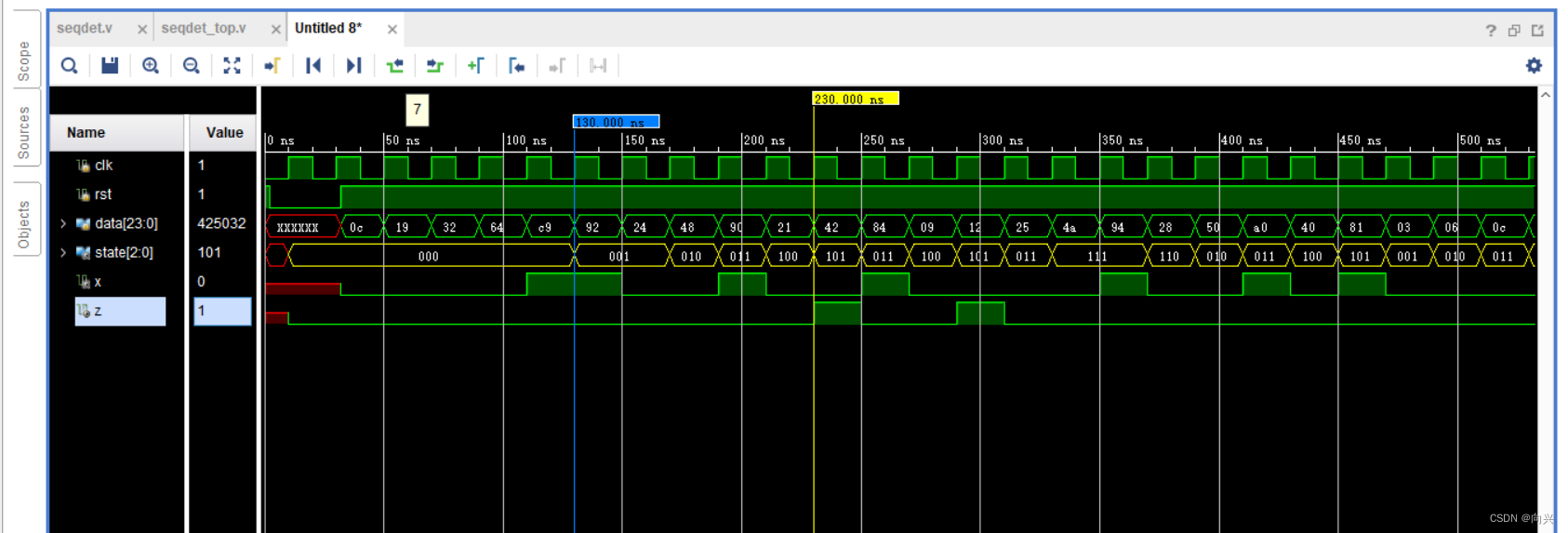

- 3,测试代码,输出波形

1,任务目的:

(1)掌握利用有限状态机实现一般时序逻辑分析的方法;

(2)掌握用Verilog编写可综合的有限状态机的模板;

(3)掌握用Verilog编写状态机模板的测试文件的一般方法。

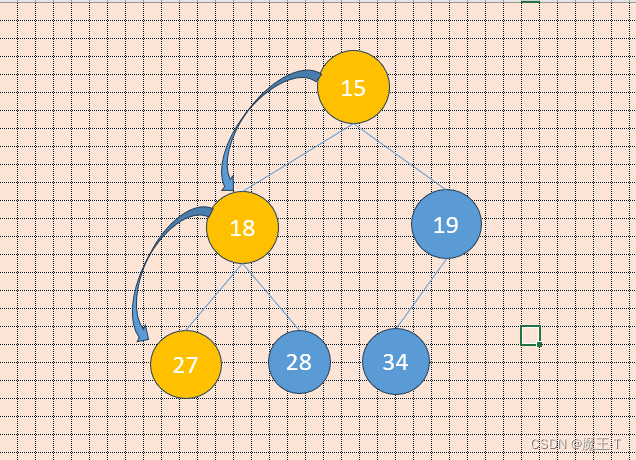

案例:重复检测序列,实现检测功能是:5进制“10010。考虑到序列重叠的可能,有限状态机共提供8个状态(包括初始状态IDLE)。”

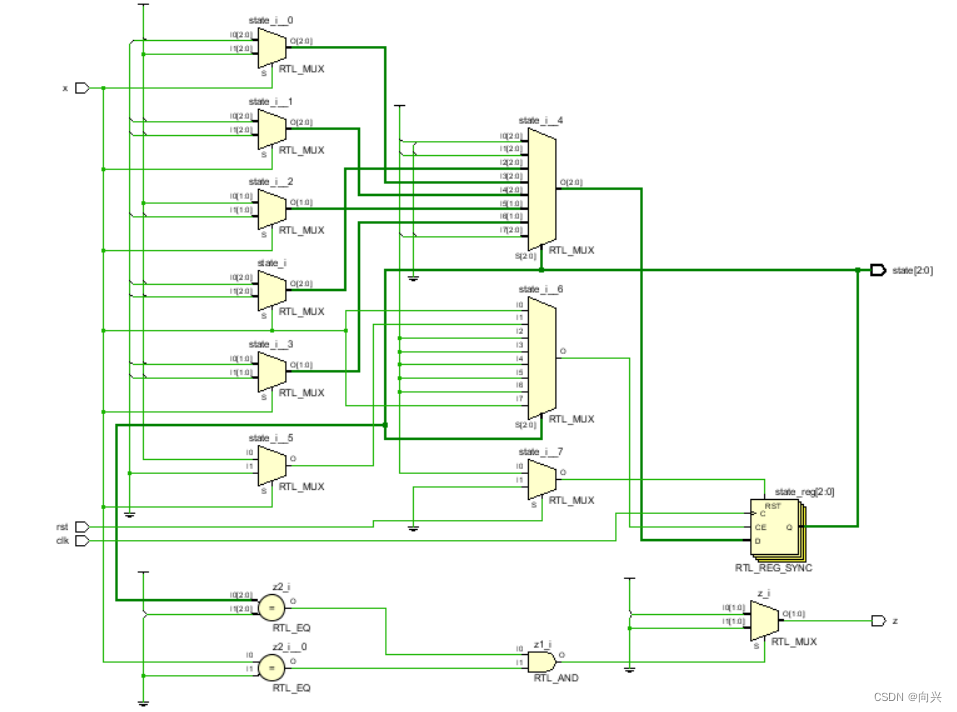

2,RTL代码,及原理框图

module seqdet(

input clk,

input x,

input rst,

output z,

output reg [2:0] state

);

// 独热码来做参数

parameter IDLE = 3'd0;

parameter A = 3'd1;

parameter B = 3'd2;

parameter C = 3'd3;

parameter D = 3'd4;

parameter E = 3'd5;

parameter F = 3'd6;

parameter G = 3'd7;

// `define IDLE 0

// `define A 1

// `define B 2

// `define C 3

// `define D 4

// `define E 5

// `define F 6

// `define G 7

assign z = ((state == E) && (x==0)) ? 1 : 0;

// 当x序列 10010 最后一个 0刚到时刻,时钟沿立刻将状态变为E,此时z应该变为高

always@(posedge clk)

if(!rst)

state <= IDLE;

else

casex(state)

IDLE: if(x == 1) // 第一个码位对,记状态A

state <= A;

A: if(x == 0) // 记状态B

state <= B;

B: if(x == 0) // C

state <= C;

else

state <= F; // 前功尽弃,到 F

C: if(x == 1)

state <= D;

else

state <= G; // 前功尽弃,到 G

D: if(x == 0)

state <= E; // 全对,此时有输出

else

state <= A;

// 第五个码位不对时,前功尽弃,只有刚进入的1位有用,回到第一个码位对状态,记状态A

E: if(x == 0)

state <= C;

else

state <= A; // 前功尽弃,只有刚输入的1码位对,记状态A

F: if(x == 1)

state <= A;

else

state <= B; // 又有一个码对,记状态B

G: if(x == 1)

state <= F; // 只有刚输入的1码位对,记状态A

default:

state <= IDLE; // 默认初始状态

endcase

// `undef IDLE

// `undef A

// `undef B

// `undef C

// `undef D

// `undef E

// `undef F

// `undef G

endmodule

3,测试代码,输出波形

// 测试模块

module seqdet_top;

reg clk, rst;

reg [23:0] data;

wire [2:0] state;

wire z, x;

assign x = data[23];

always #10 clk = ~clk;

always@(posedge clk)

data = {data[22:0], data[23]};

// 形成数据向左移环形流,最高位与x连接

initial begin

clk = 0; rst = 1;

#2; rst = 0;

#30; rst = 1;

data = 24'b0000_1100_1001_0000_1001_0100;

#500; $stop;

end

seqdet u_seqdet(

.clk (clk ),

.rst (rst ),

.x (x ),

.z (z ),

.state (state )

);

endmodule