微信公众号上线,搜索公众号小灰灰的FPGA,关注可获取相关源码,定期更新有关FPGA的项目以及开源项目源码,包括但不限于各类检测芯片驱动、低速接口驱动、高速接口驱动、数据信号处理、图像处理以及AXI总线等

1、奇偶监督码(parity check)

奇偶监督码分为奇数监督码和偶数监督码,两者原理相同。

利用“⊕模2和”进行检错,适用于检测随机错码。

(1)偶数监督码

在偶数监督码中,无论信息位多少,监督位只有1位,使码组中“1”的数目为偶数,即满足:

an-1⊕an-2⊕……⊕a0=0

a0为监督位,其他位为信息位

在接收端,按照上述公式求“模2和”

若计算结果为“1”表示存在错码

若计算结果为“0”表示无错码

(2)奇数监督码

在奇数监督码中,无论信息位多少,监督位只有1位,使码组中“1”的数目为偶数,即满足:

an-1⊕an-2⊕……⊕a0=1

a0为监督位,其他位为信息位

在接收端,按照上述公式求“模2和”

若计算结果为“0”表示存在错码

若计算结果为“1”表示无错码

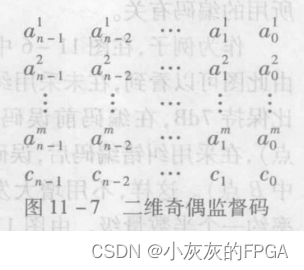

2、二维奇偶监督码(two dimensional)

二维奇偶监督码又称为方阵码。

把奇偶监督码的若干码组,每个写成一行,然后再按照列的方向增加第二维监督位。

每一行的最后一位代表该行的监督位,每一列的最底下一位代表该列进行第二次编码所增加的监督位。

方阵码适用于检测突发错码。突发错码常常成串出现,随后有较长一段无措区间,在某一行中出现多个奇数或偶数错码的机会较多。

由于方阵码只对构成矩形四角的错码无法检测,检错能力较强,可使误码率降至原误码率的1/100到1/10000。

3、恒比码

在恒比码中,每个码组均含有相同数目的“1”和“0”。由于“1”的数目和“0”的数目之比保持恒定,故称为恒比码。

检测过程中,只要计算接收码组中“1”的数目是否对,即可判断有无错码。

恒比码的主要优点在于简单,适用于来传输电传机或其他键盘设备产生的字母和符号。

4、正反码

正反码是一种简单的能够纠正错误的编码,其中的监督位数目和信息位数目相同,监督码元与信息码元相同或者相反,由信息码中“1”的个数来确定。

若码长n=10,其中信息位k=5,监督位r=5,其编码规则为:

①当信息位中奇数个“1”时,监督位是信息位的简单重复;

②当信息位中偶数个“1”时,监督位是信息位的反码。

例如:

信息位为11001,码组为1100111001;

信息位为10001,码组为1000101110。

接收端解码规则:

①现将接收码组中信息位和监督位按“模2”相加,得到一个5位的合成码组;

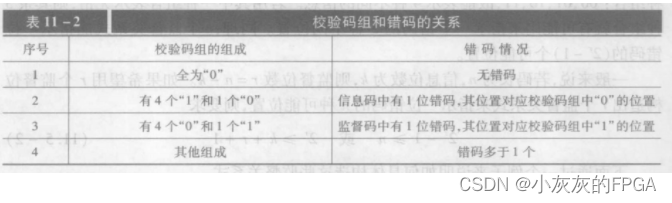

②由合成码组产生一个校验码组。若接收码组的信息位中有奇数个“1”,则合成码组就是校验码组;若接收码组的信息位中有偶数个“1”,则取合成码组的反码作为校验码组;

③观察校验码组中“1”的个数,按照规则进行判决和纠正可能发现的错码。

一个编码示例:

①发送码组为1100111001,接收码组中无错码,则合成码组为11001⊕11001=00000。由于接收码组信息位中有奇数个“1”,校验码组为00000,按判决规则可知:无错码。

②若传输过程中发送差错,接收码组变成1000111001,则合成码组为10001⊕11001=01000。由于接收码组信息位中有偶数个“1”,校验码组为10111。按判决规则,校验码组有4个“1”和1个“0”,确定:信息码中有1位错码,其位置对应校验码组“0”的位置,也就是信息码左边第二位为错码,可对其进行取反纠错。

③若传输过程中发送差错,接收码组变成1100101001,则合成码组为11001⊕01001=10000。由于接收码组信息位中有奇数个“1”,校验码组为10000。按判决规则,校验码组有4个“0”和1个“1”,确定:监督码中有1位错码,其位置对应校验码组“1”的位置,也就是监督码左边第一位为错码,可对其进行取反纠错。

④若传输过程中发送差错,接收码组变成1001111001,则合成码组为10011⊕11001=01010。按判决规则,可知错码多余一个。

通信原理板块——奇偶监督码、方阵码、恒比码、正反码

news2026/2/11 0:47:08

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/1223367.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

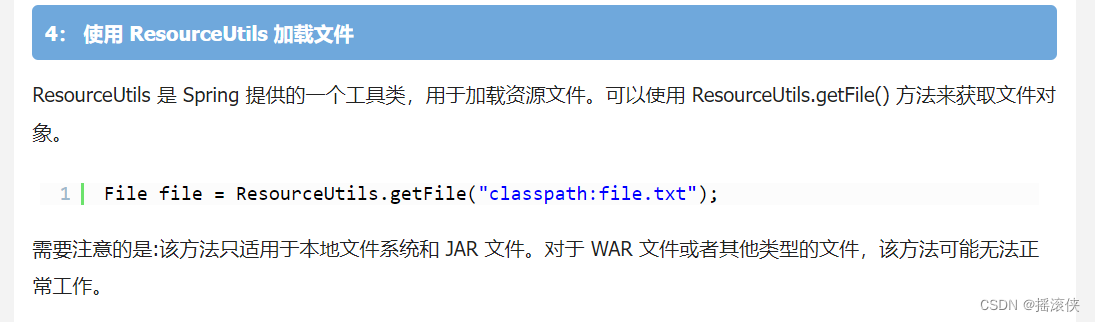

springboot jar包 无法读取静态资源文件

springboot jar包 无法读取静态资源文件

参考 springboot项目读取resources目录下的文件的9种方式 Resource resource resourceLoader.getResource("classpath:static/jkbw/jkbw4.txt");try{InputStream inputStream resource.getInputStream();BufferedReader r…

【广州华锐互动VRAR】VR元宇宙技术在气象卫星知识科普中的应用

随着科技的不断发展,虚拟现实(VR)和元宇宙等技术正逐渐走进我们的生活。这些技术为我们提供了一个全新的互动平台,使我们能够以更加直观和生动的方式了解和学习各种知识。在气象天文领域,VR元宇宙技术的应用也日益显现…

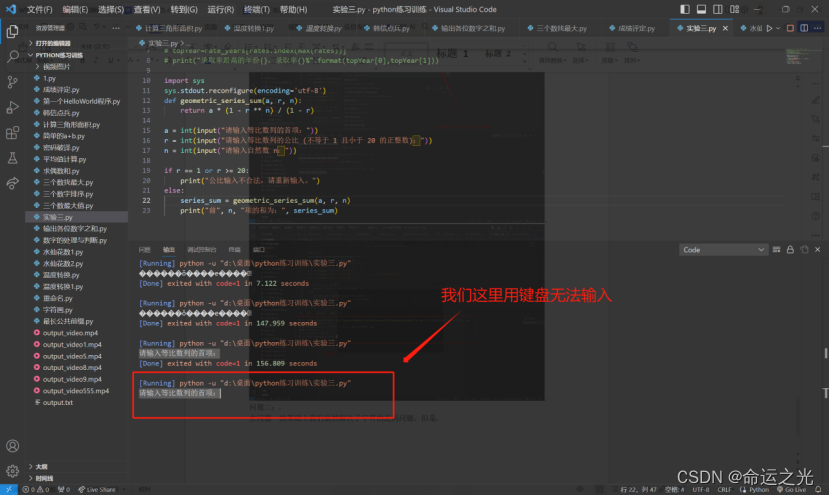

实验二 运算符和内置函数使用(Python程序设计实验报告)

实验二 运算符和内置函数使用 实验环境

Python集成开发环境IDLE/Anaconda

实验目的

1.熟练掌握常用运算符的使用。

2. 熟练掌握常用内置函数的使用。

三、实验内容

1. 输入三角形的3个边长a、b、c,求三角形的面积area。利用如下海伦公式求三角形的…

毅速丨金属3D打印将为模具制造企业带来变革

金属3D打印技术的发展给模具制造带来了巨大的创新价值,包括重塑产品、重组制造、重构业务。 首先,3D打印技术可以大幅度缩短模具制造的生产周期,提高生产效率。传统的模具制造需要经过多个工序和加工过程,而3D打印技术通过打印完成…

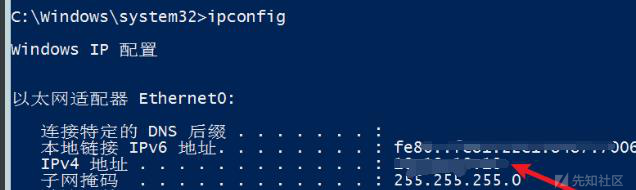

CVE-2021-42287CVE-2021-42278 域内提权

倘见玉皇先跪奏:他生永不落红尘

本文首发于先知社区,原创作者即是本人

前言

网络安全技术学习,承认⾃⼰的弱点不是丑事。只有对原理了然于⼼,才能突破更多的限制。拥有快速学习能力的白帽子,是不能有短板的…

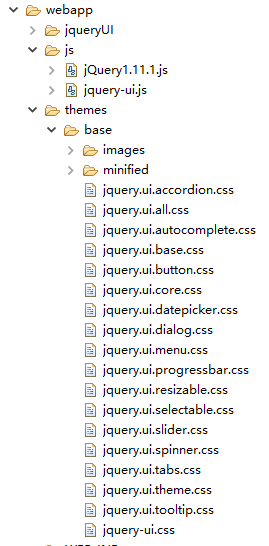

jQuery UI简单的讲解

我们先进入一下问答时间,你都知道多少呢?

(1)什么是jQuery UI 呢? 解答:jQuery UI 是以 jQuery 为基础的开源 JavaScript 网页用户界面代码库。包含底层用户交互、动画、特效和可更换主题的可视控件。我们…

【广州华锐互动】消防安全宣传知识3D交互展示提升公众学习沉浸感

随着科技的快速发展,我们的生活与工作环境愈发复杂,火灾风险也随之提高。为了提高公众的消防灭火能力,普及消防安全知识,广州华锐互动开发了消防安全宣传知识3D交互展示系统。 这是一种全新的教育方式,它利用3D技术&am…

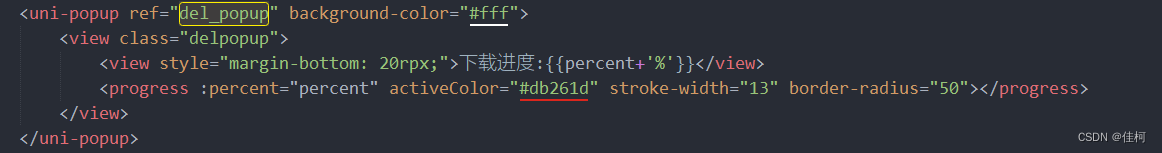

uniapp App 端 版本更新检测

function checkVersion() { var req { //升级检测数据 appid: plus.runtime.appid, version: plus.runtime.version }; const timestamp Date.parse(new Date()); config.server.query_news uni.reque…

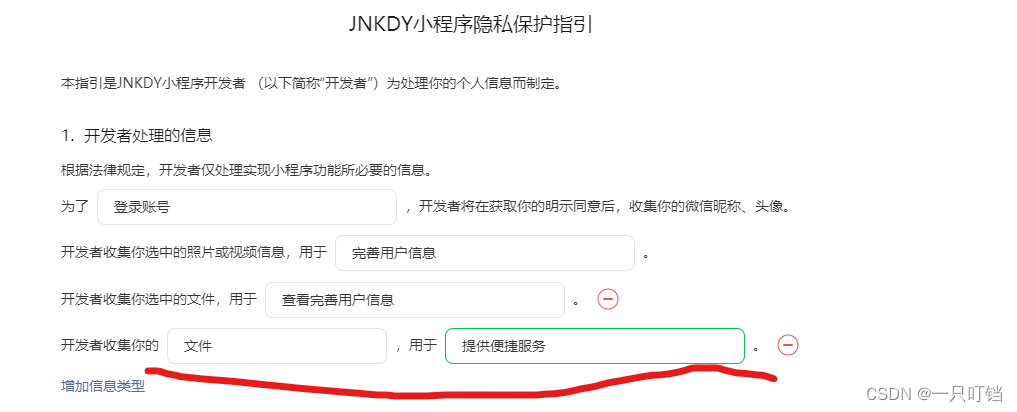

微信小程序开发---实现文件上传和下载

在开发小程序的过程中,我们难免会遇到使用小程序对后端发送文件;或者接收后端的文件,本文章将手把手带你简单高效实现微信小程序的文件上传下载功能 前期准备

由于目前小程序保护用户个人隐私力度加大 ,因此我们要想实现文件上传…

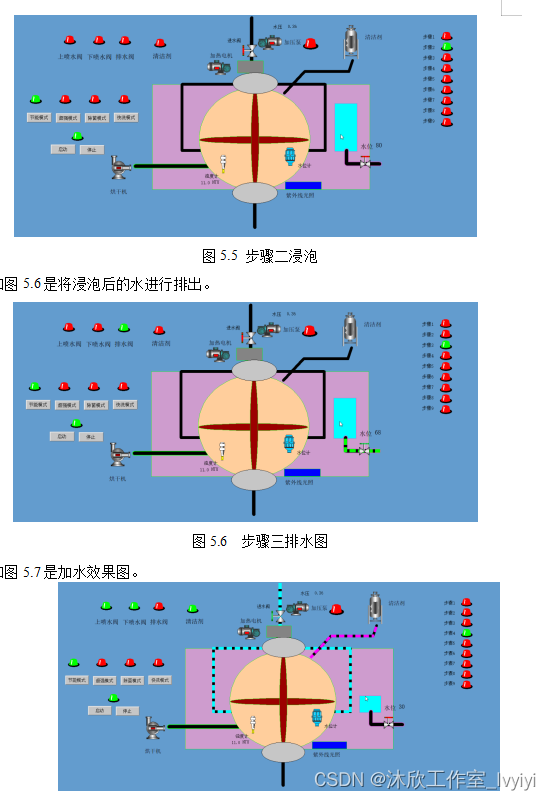

基于PLC的自动洗碗机控制系统(论文+源码)

1.系统设计

本课题基于PLC的自动洗碗机控制系统,在此将主要功能设定如下:

通过上下喷头旋转喷水湿润餐具;添加洗涤剂(洗碗液);上下喷头喷水洗涤餐具;排出污水;往碗碟上喷洒更多的水…

在c#中如何将多个点位(Point)转换为多边形(Polygon)并装换为shp图层

👻如图,我现在有一组经纬度点位Point,接下来我们将他装换为多边形Polygon格式 👻使用QGIS > 图层 > 添加图层 > 添加分隔文本图层 > 打开这个csv点位文件 👻打开后如左下图,csv文件中的四个点位…

突发!“ChatGPT 之父”奥特曼被 OpenAI 开除!!乔布斯故事重演了?

重磅消息!

OpenAI刚刚官宣领导层换届,SamAltman辞任CEO并离开董事会,原CTO Mira Murati 任命为临时CEO,并正在进行寻找永久继任CE0。

大模型研究测试传送门

GPT-4传送门(免墙,可直接测试,遇浏…

代码随想录算法训练营第25天|216.组合总和III 17.电话号码的字母组合

JAVA代码编写

216. 组合总和III 找出所有相加之和为 n 的 k 个数的组合,且满足下列条件: 只使用数字1到9每个数字 最多使用一次 返回 所有可能的有效组合的列表 。该列表不能包含相同的组合两次,组合可以以任何顺序返回。 示例 1: 输入: k …

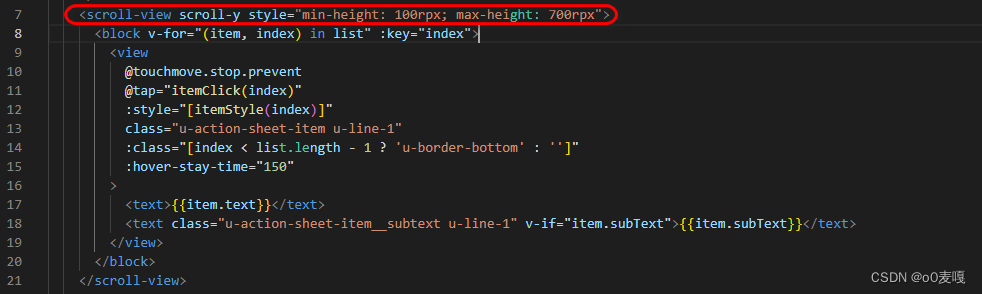

uview使用u-action-sheet添加滚动条

0 效果 1 修改uview源码

node_modules/uview-ui/u-action-sheet/u-action-sheet.vue

vb.net U盘或移动硬盘 插入 自动(静默)复制指定格式文件

U盘或移动硬盘 插入 自动复制指定格式文件至系统盘符

开发语言:vb.net

重要申明:该程序只是防止本人不在电脑旁时,别人偷偷copy你的电脑文件,让他偷鸡成了也要蚀把米。严禁从事黑客或违反道德等不良行为,故而不发布程…

4月2日-3日·上海 | 3DCC 第二届3D细胞培养与类器官研发峰会携手CGT Asia 重磅来袭

类器官(Organoids)作为干细胞研究领域最重要的成果之一,在基础医学研究、转化医学及药物研发领域展现出巨大的应用潜力,特别是在精准医疗以及药物安全性和有效性评价等方向凭借其先天优势引起了极大的市场关注,成为各大…

asp.net心理健康管理系统VS开发sqlserver数据库web结构c#编程计算机网页项目

一、源码特点 asp.net 心理健康管理系统 是一套完善的web设计管理系统,系统具有完整的源代码和数据库,系统主要采用B/S模式开发。

系统视频链接 https://www.bilibili.com/video/BV19w411H7P4/ 二、功能介绍 本系统使用Microsoft Visual Studio…

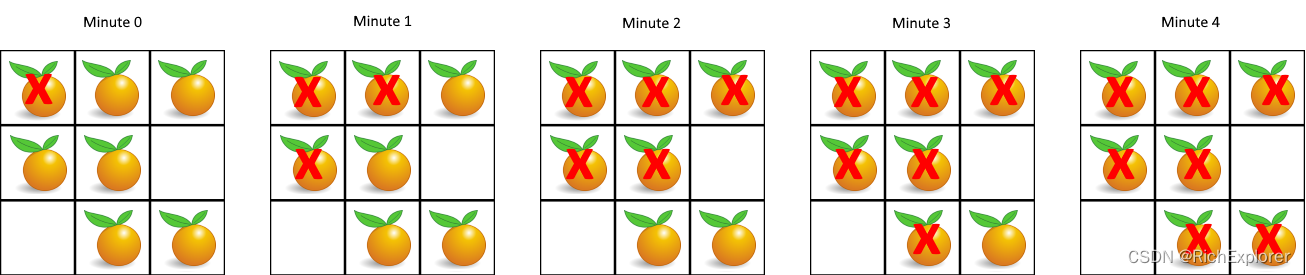

LeetCode热题100——图论

图论 1. 岛屿的数量2. 腐烂的橘子 1. 岛屿的数量

给你一个由 ‘1’(陆地)和 ‘0’(水)组成的的二维网格,请你计算网格中岛屿的数量。岛屿总是被水包围,并且每座岛屿只能由水平方向和/或竖直方向上相邻的陆…