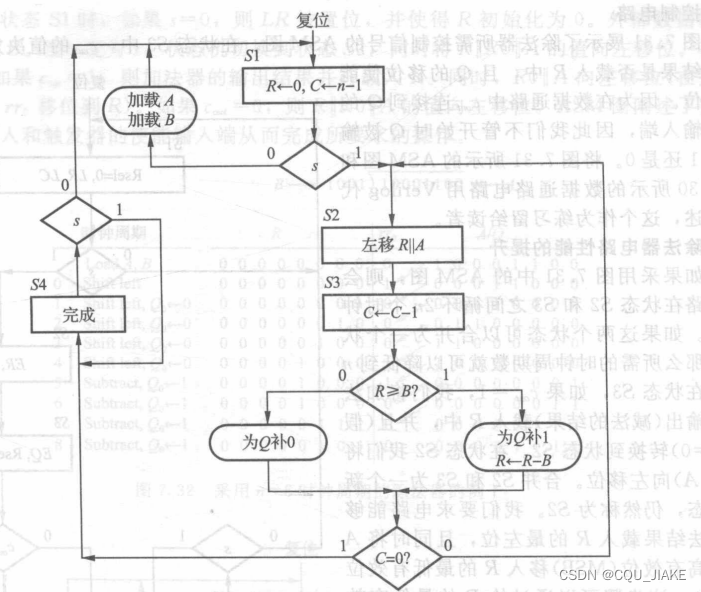

ASM图

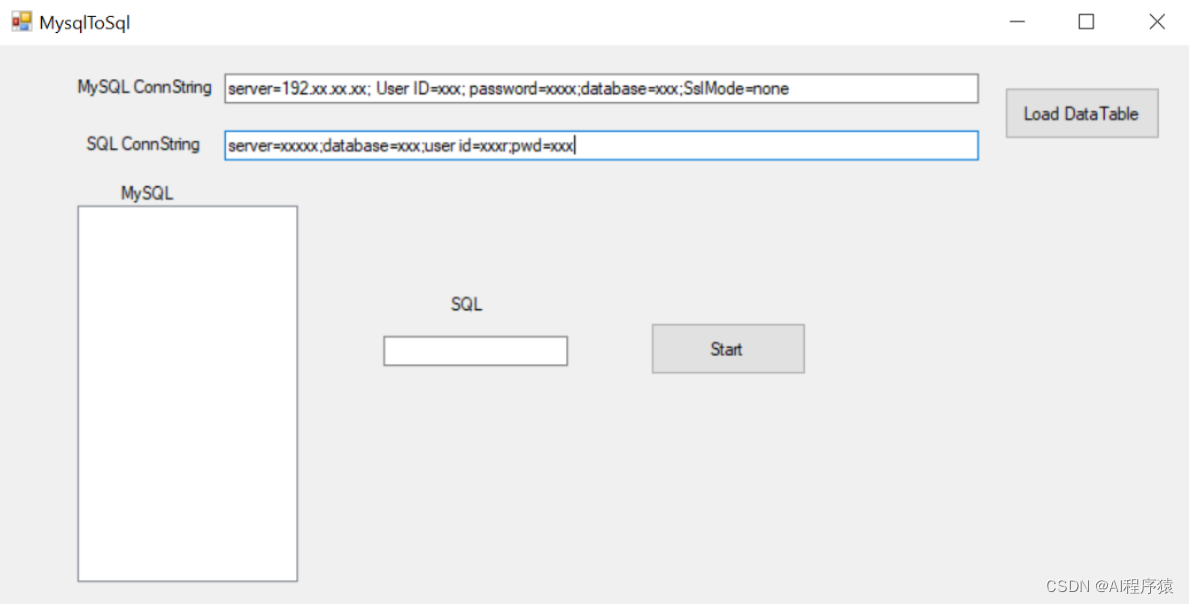

除法器

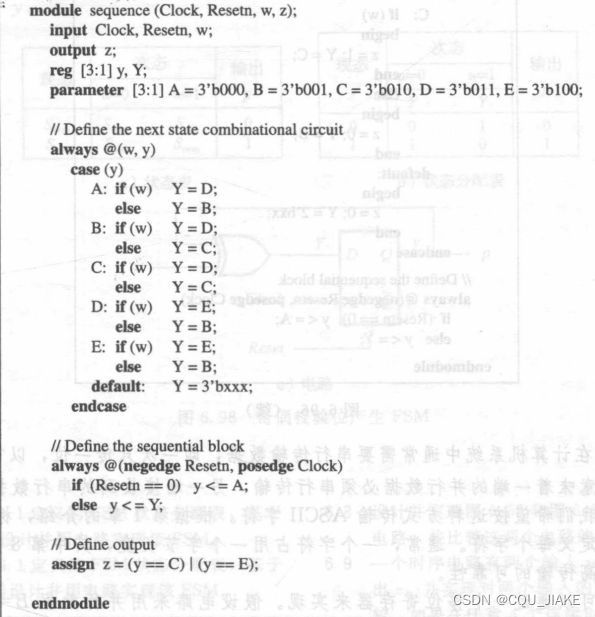

FSM的verilog实现

状态机的状态就不用编码,而是用参数的定义进行转换

1.

![]()

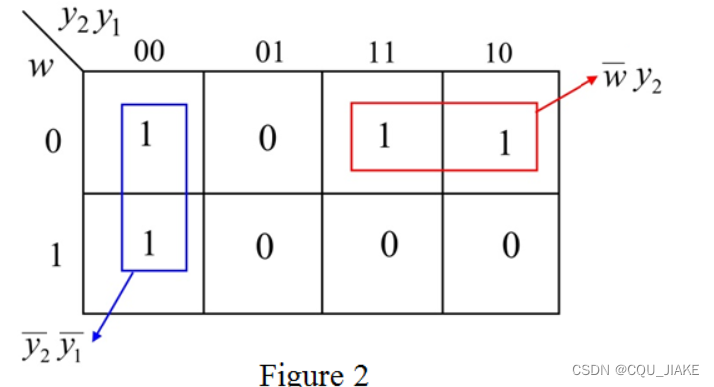

在次态确定当中,只要w和y发生变化,就进行操作

![]()

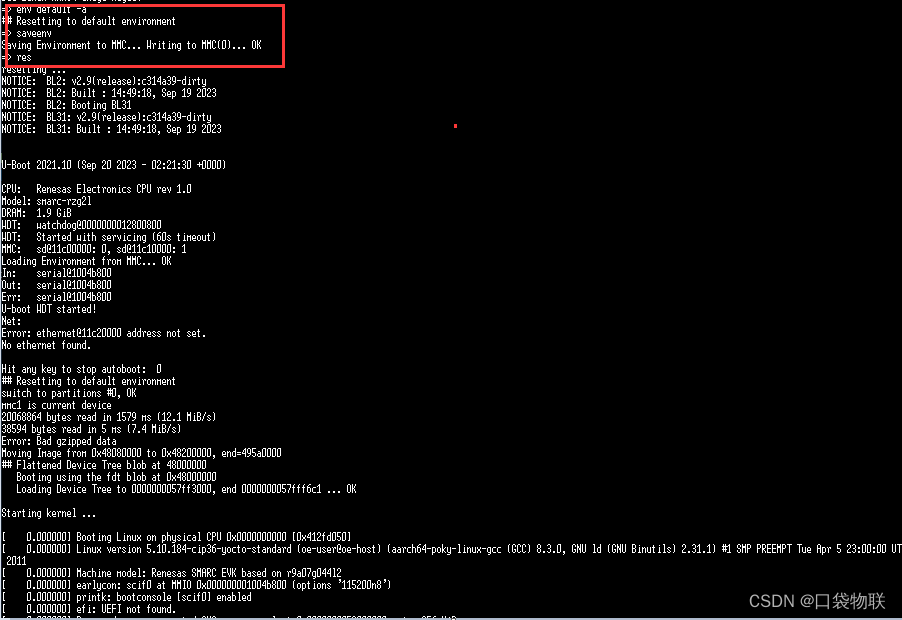

在次态当中,只要时钟上升沿来临或者复位信号,就进行操作

2

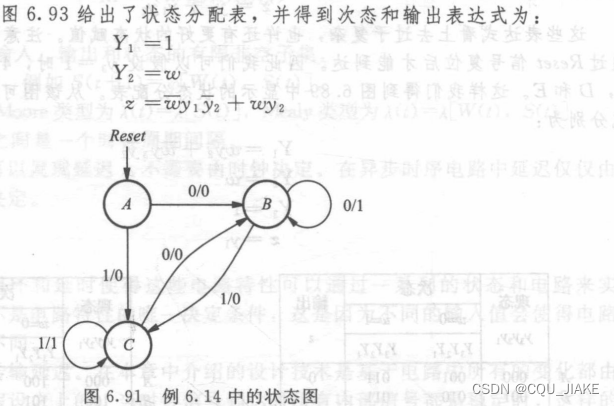

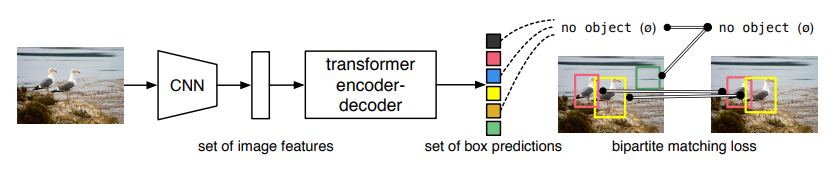

Mealy型状态机

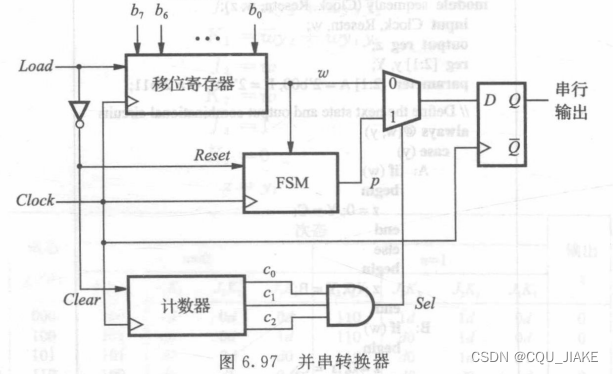

串并转换与奇偶检验

这一部分就是将多位信号一位一位输出,通过移位寄存器

这里FSM存储两个状态,一个状态是说前面有奇数个1,一个是偶数个;然后不断接收移位寄存器传过来的一位信号,从而不断更新状态,并根据现在状态给出输出P

这里就是统计当前移位寄存器已经输出了几个信号,输出一个sel表示是否输出FSM的p信号,即要保证p信号是多位信号的最后一位信号

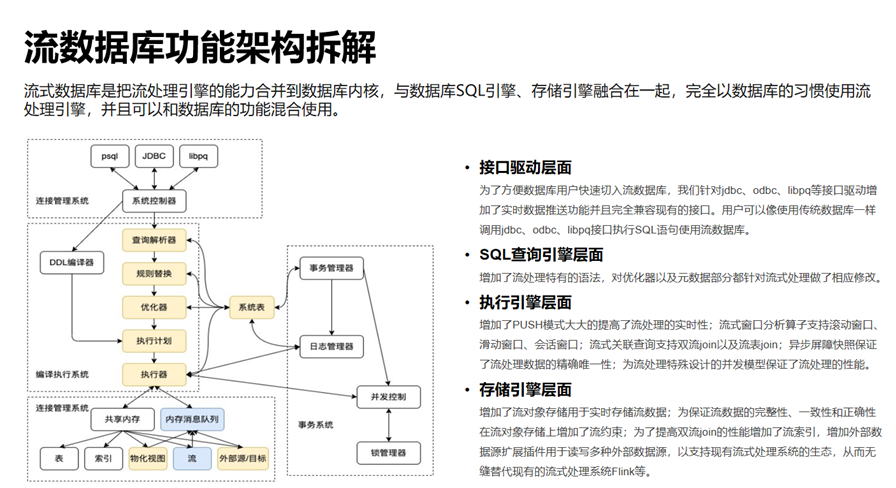

6.1

不变的才是最后的项,对于变的,即不影响输出,输出与其无关

![[Linux]NFS文件共享服务](https://img-blog.csdnimg.cn/e7e469b114154e57aa0f6dc97ecc38a1.png)