目录

一、实验目的

二、实验原理

三、实验内容

四、实验步骤

五、注意事项

六、思考题

七、实验过程

分频器的基本原理

什么是分频器?

如何去分频?

1.创建新项目

2.创建Verilog文件,写入代码

3.连接电路

编辑 锁相环的创建

4.烧录文件

一、实验目的

- 学习数控分频器的设计、分析和测试方法。

- 了解和掌握分频电路实现的方法。

- 掌握EDA技术的层次化设计方法。

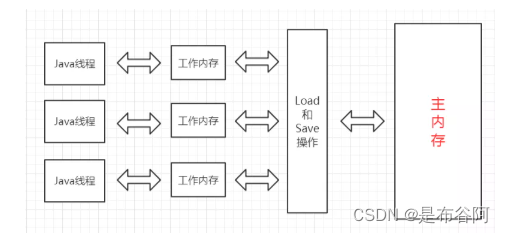

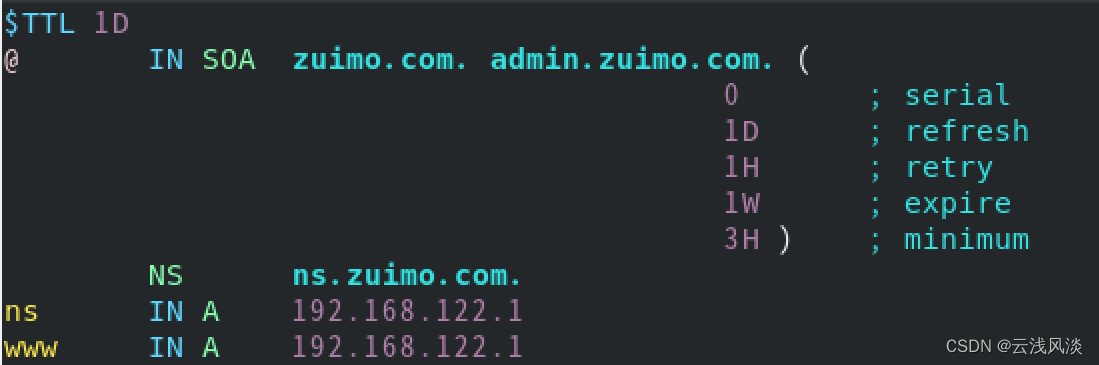

二、实验原理

数控分频器的功能就是当输入端给定不同的输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器来设计完成的,方法是将计数溢出位与预置数加载输入信号相接得到。

三、实验内容

本实验要求完成的任务是在时钟信号的作用下,通过输入四位的拨码开关输入不同的数据,改变分频比,使输出端口输出不同频率的时钟信号,达到数控分频的效果。在实验中时,数控分频器的数字时钟输入2HZ作为输入的时钟信号(所以事先要先通过编程得到这个时钟信号),用四位拨码开关做为数据的输入,当拨码开关置为一个二进制数时,在输出端口输出对应频率的时钟信号,用输出端口接LED灯来观察频率的变化。

四、实验步骤

图示如下:

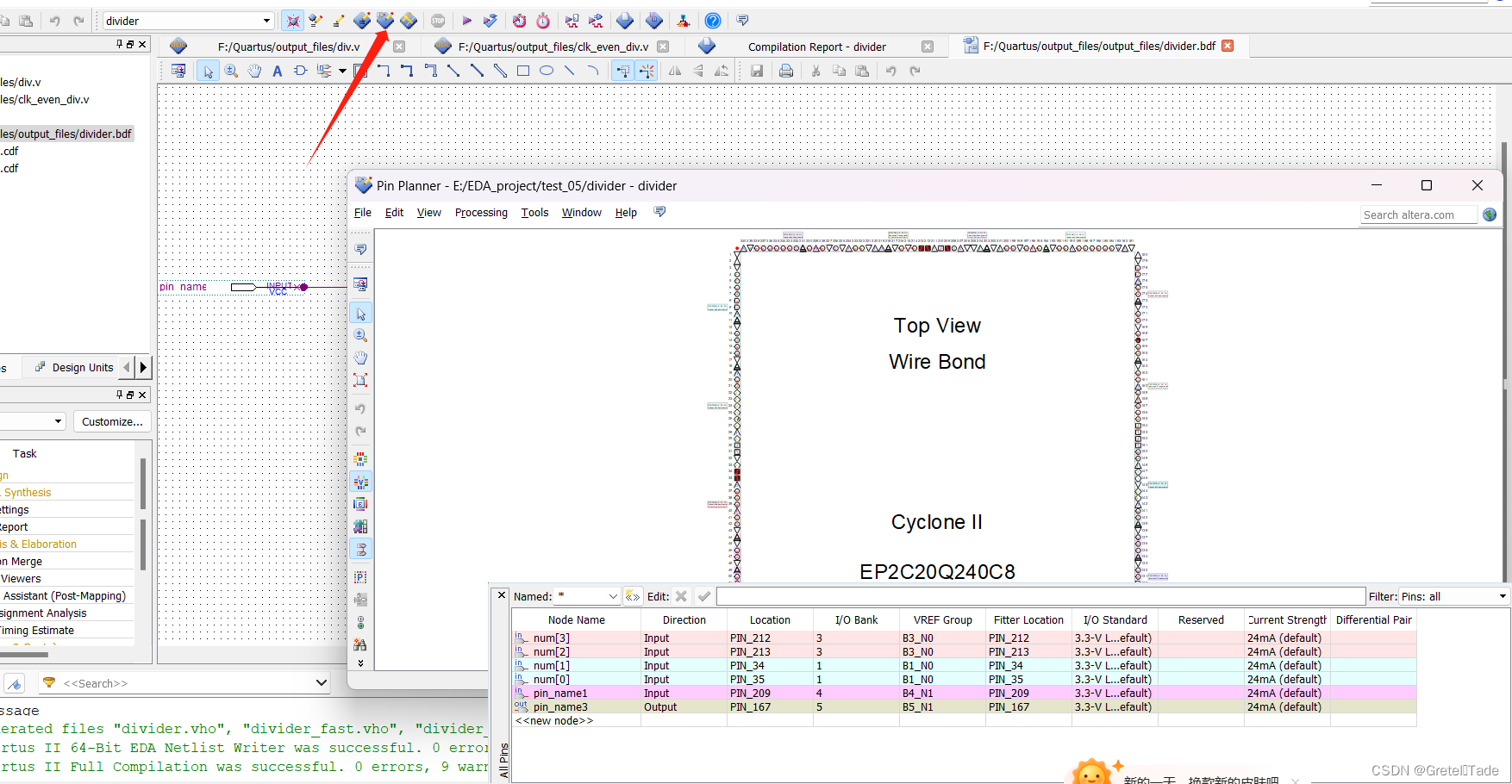

表4-1 端口管脚分配表

| 端口名 | 对应FPGA管脚 | 说 明 |

| CLK | 209 | 时钟为10KHZ |

| DIN | 212、213、34、35 | 输入数据 |

| LED | 167 | 分频输出 |

| LED_CS | 174 |

- 打开QUARTUSII软件,新建一个工程。

- 新建一个Schematic File 文件。

- 新建一个锁相环将输入的50MHz的时钟分频成10MHz。

- 新建两个Verilog File,打开Verilog编辑器对话框,第一个文件的功能是将10MHz分频成2Hz。第二个文件的功能是实现数控分频器设计。

- 按照实验原理和自己的想法,在Verilog编辑窗口编写Verilog程序。

- 编写完Verilog程序后,保存起来。

- 从设计文件创建模块。

- 对自己编写的Verilog程序进行编译并仿真,对程序的错误进行修改。

- 在 Schematic File文件中,在空白处双击鼠标左键,在 Symbol 对话框左上角的libraries 中,分别将 创建的模块放在图形文件 Schematic File中,加入输入、输出引脚,双击每个引脚,进行引脚命名,并锁定管脚,将未使用的引脚设置为三态输入(一定要设置,否则可能会损坏芯片)

- 编译仿真无误后,依照拨码开关、LED与FPGA的管脚连接表(表1-1、表1-2)或参照附录进行管脚分配。表4-1是示例程序的管脚分配表。分配完成后,再进行全编译一次,以使管脚分配生效。

- 用下载电缆通过JTAG口将对应的sof文件加载到FPGA中。观察实验结果是否与自己的编程思想一致。

五、注意事项

- 注意观察当输入数据改变是输出的反应。

- 一定要把没用的管教设置成三态输入。

- 对实验现象进行分析总结。

六、思考题

- 简述锁相环的基本原理及应用。

- 总结本次实验的心得体会。

七、实验过程

分频器的基本原理

什么是分频器?

分频就是生成一个新时钟,该新时钟的频率是原有时钟频率的整数分之一倍,新周期是原有周期的整数倍。再简单来说,让你手撕一个四分频电路,就是写代码生成一个周期是原来四倍的时钟,如果手撕一个三分频电路,就是写代码生成一个周期是原来三倍的时钟。但是奇数分频会比偶数分频复杂一些。

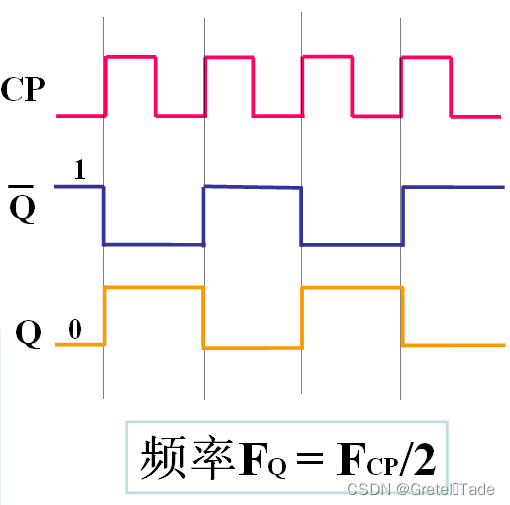

如图所示,这就是一个二分频的结果图,堆输入信号CP进行二分频。

如何去分频?

很简单,我们只需要去进行数数就可以了,对输入信号进行周期数数,比如要进行4分频的话,那么我们对输入信号周期数到2,就进行一次翻转,然后再数到2又一次进行翻转,那么输出信号的一个周期就等于输入信号的4个周期。(如下图所示)

分频分为奇数分频和偶数分频,上面的例子是对于偶数分频的,偶数分频是比较简单的,只需要去对半开就行了,一半是低电平另一半就是高电平。但是对于奇数分频的话会比较麻烦,奇数分频我们可以把奇数分频转换为偶数分频去实现,也就是说其中有一段是为空电平的,比如5分频,对输入信号进行周期数数,把输入信号其中一个周期设置为空电平即可,然后剩下4个周期数到其中一半为低电平,另一半为高电平就行了。下面项目我就以偶数分频为示例,如果你们对奇数分频感兴趣的话可以去自己试试。

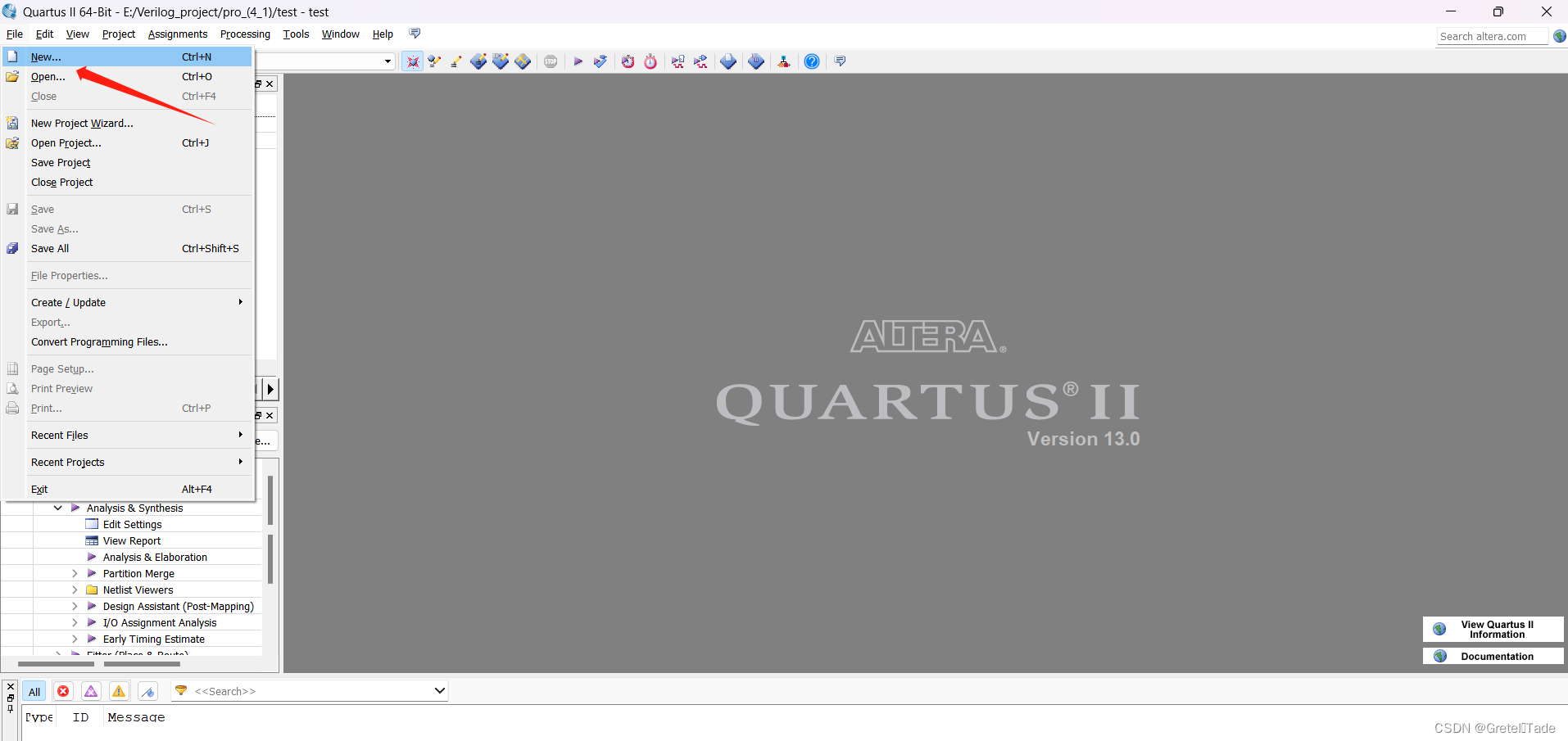

1.创建新项目

打开你的QuartusII,然后点击New project,就去创建新项目。

然后设置项目的路径和名称(自己设置就好了)

选择相对应的芯片类型(看自己情况选择)

创建完成!

创建完成!

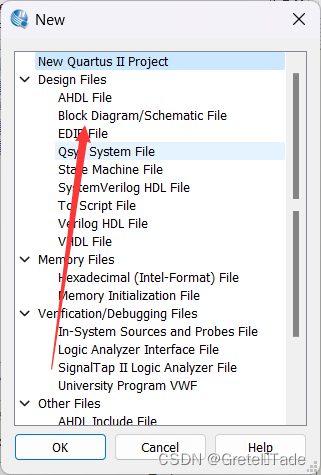

2.创建Verilog文件,写入代码

点击New,创建文件

选择Verilog文件,创建

选择Verilog文件,创建

然后就是写代码,写完之后就进行保持文件,把文件的名称跟模块的名称改成一样。(必须一致)

根据实验要求我们要去创建两个Verilog文件,如下所示:

第一个文件 div.v 文件,此文件目的是把输入信号的10MHz频率转换为2Hz频率。代码如下。

module div(clk,out_clk);

input wire clk;

output out_clk;

reg out_clk;

reg [26:0] cnt;

always@(posedge clk )

begin

if(cnt == 2500000)

begin

out_clk = out_clk +1;

cnt = 0;

end

else

begin

cnt = cnt +1;

end

end

endmodule 第二个文件就是去实现数控分频,也就是前面一个文件分频后的2Hz输入信号进行分频。代码如下:

module clk_even_div(

input clk,//输入信号

input [3:0] num,//输入要进行的分频数,偶数

output reg clk_div//输出信号频率

);

reg [3:0] cnt=4'd0;//临时数据,进行数数统计

always @(posedge clk)

begin

if(cnt==num/2-1)//如果数到一半,输出信号就进行翻转

begin

cnt<=cnt+4'd1;

clk_div<=1'b1;

end

else if(cnt==num-1)//如果数完了之后,再次翻转

begin

cnt<=4'd0;

clk_div<=1'b0;

end

else //其他情况的话就进行继续数数

begin

cnt<=cnt+4'd1;

end

end

endmodule

然后写完之后保存,注意代码模块的名称必须与文件的名称一致!!

最后就是点击编译运行,运行无误。代码完成之后就进入到下一步,连接电路。

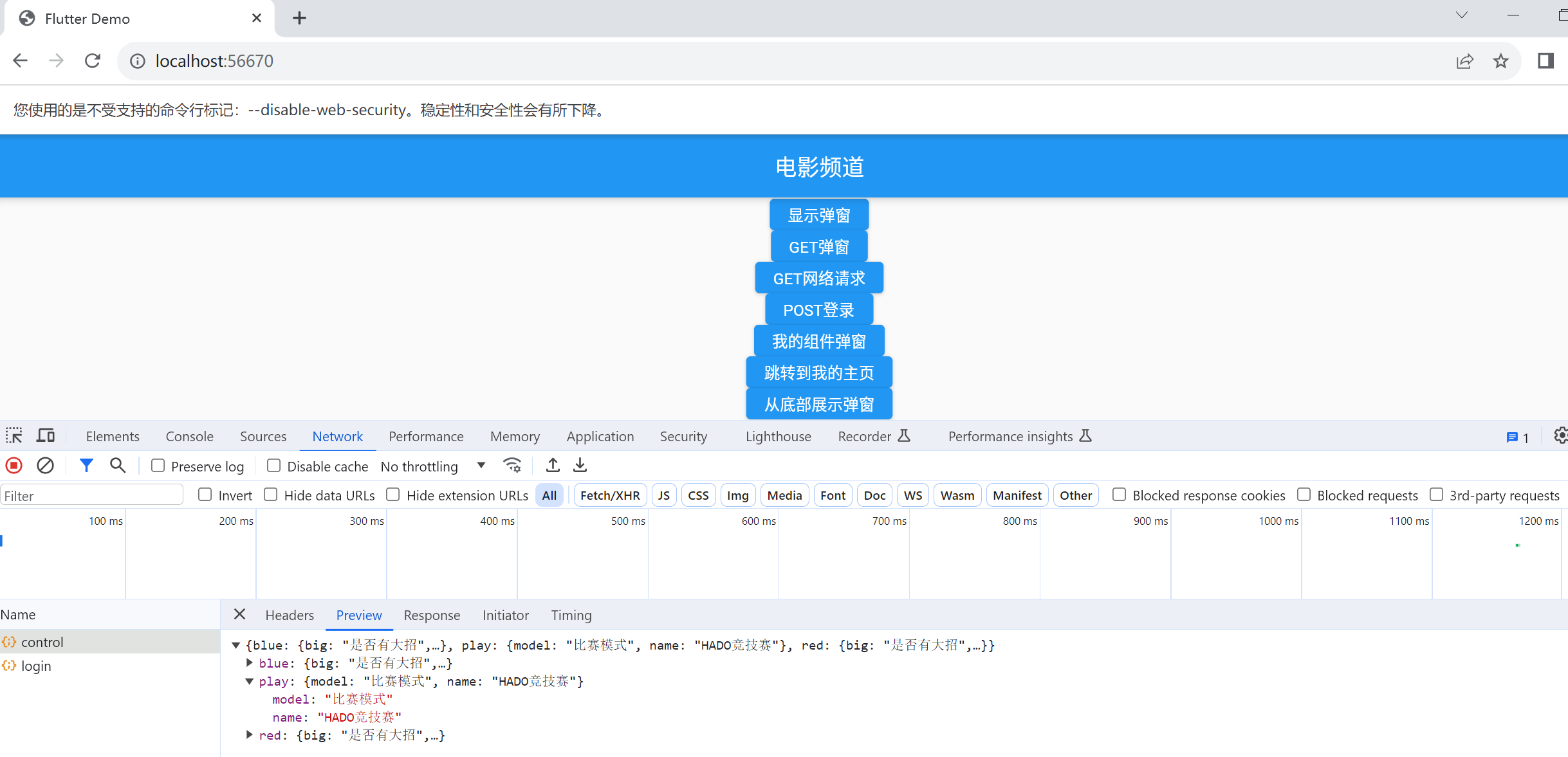

3.连接电路

创建block文件

然后对前面写好的Verilog文件,去创建子模块文件,如图所示,鼠标右键,点击创建子模块文件。如图所示:

点开元器件,这里我们就可以看到project文件夹下面有我们前面Verilog文件的模块元器件。

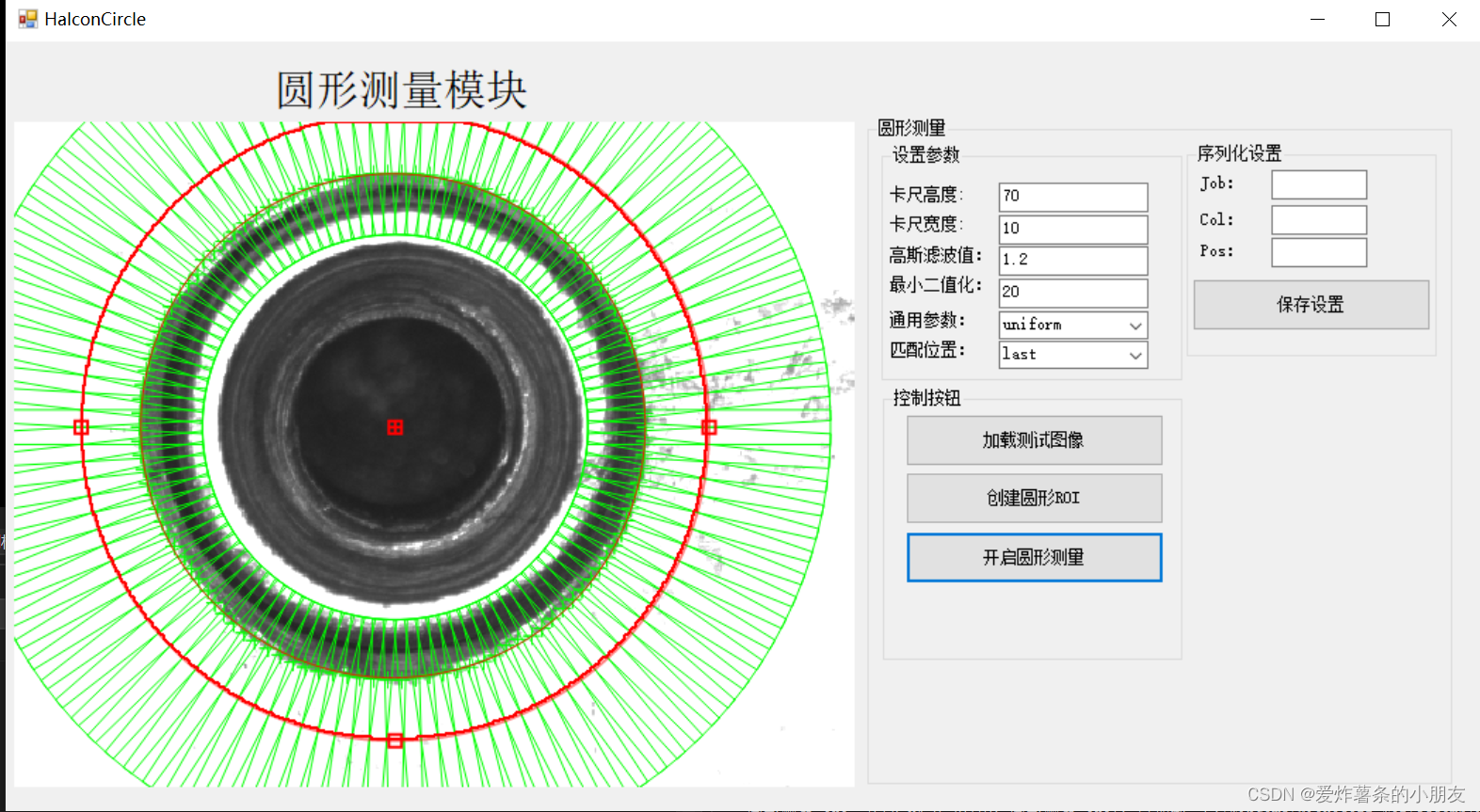

锁相环的创建

锁相环的创建

根据实验的要求,我们要去创建一个锁相环,所以这里我单独拿出来讲这么去创建这么一个锁相环。

这里,我们点击箭头指向的这个按钮。

然后就是勾选第一个,意思是创建一个自定义的元器件。

- 搜索pll

- 下面就会显示出ALPLL,点击选中

- 然后进行命名

- 勾选AHDL,最后点击Next下一步

看到这里,我们根据实验要求,把这个输入频率改为50MHz,然后点击下一步

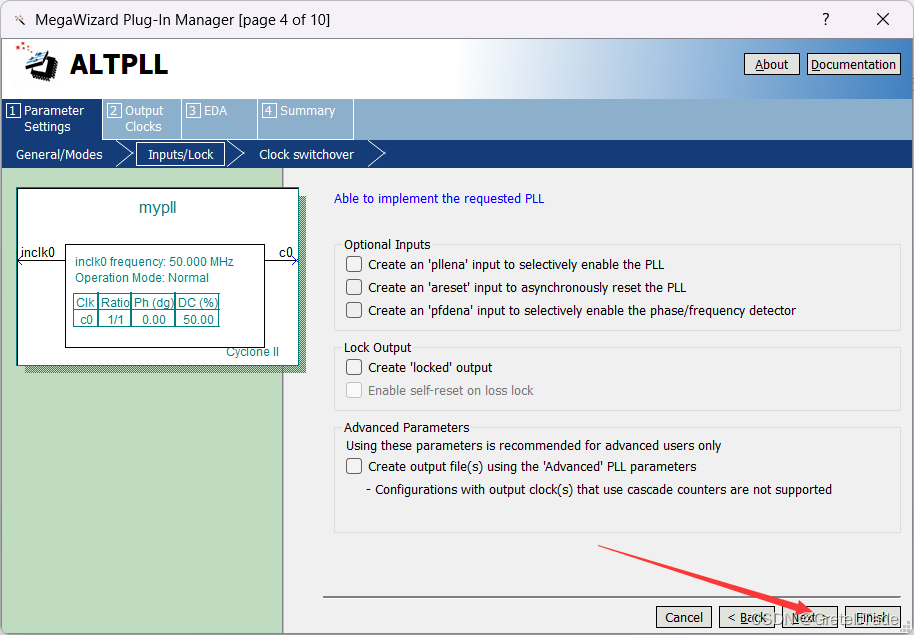

然后就是这选项都不勾选,直接继续下一步

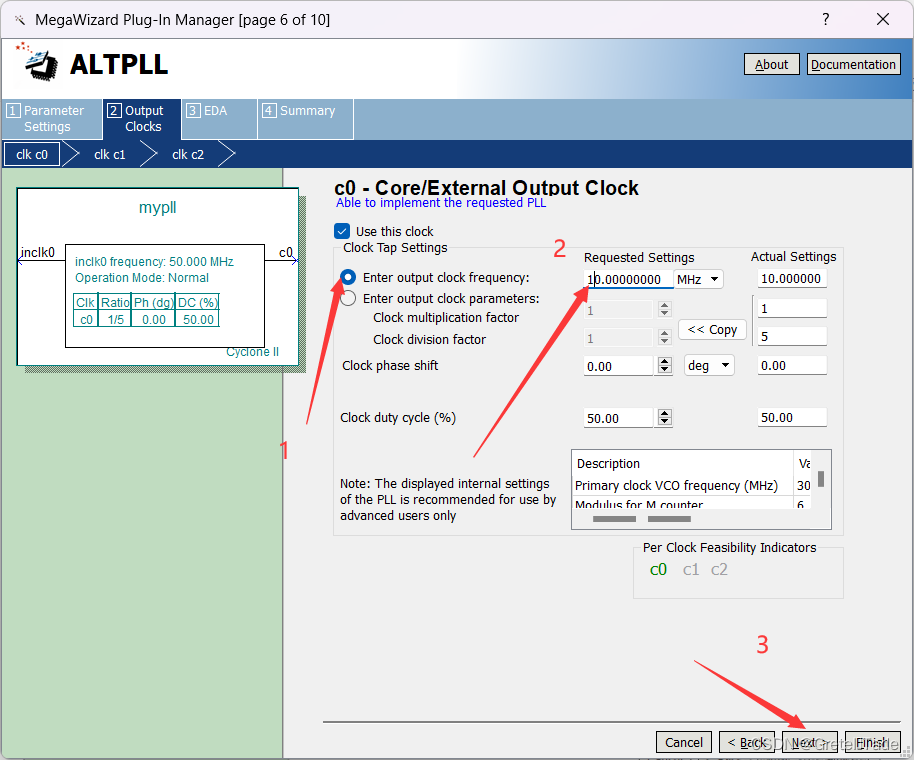

然后,这里我们点击输入你想要的输出频率,这里我们就设置为输出10MHz的频率,最后就是Next下一步。

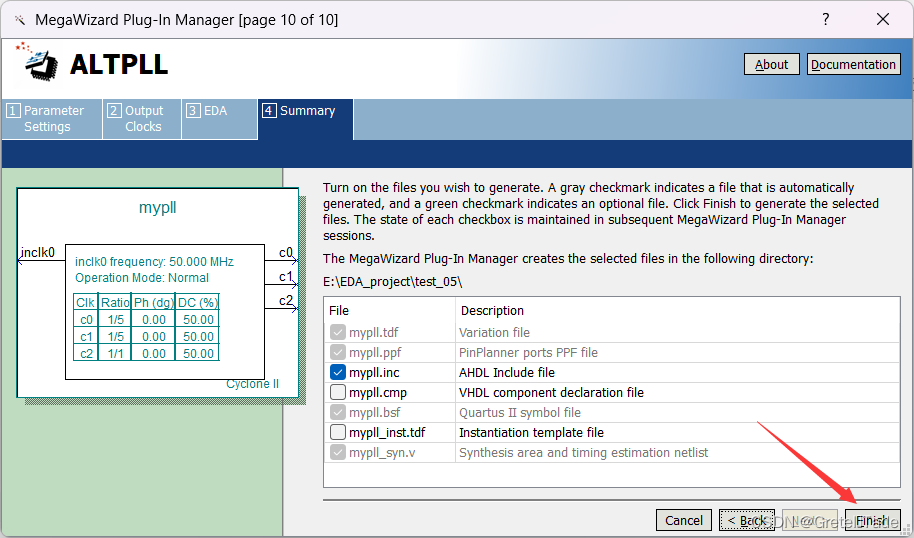

然后下一步就是勾选这个 然后点击完成就行了。

然后点击完成就行了。

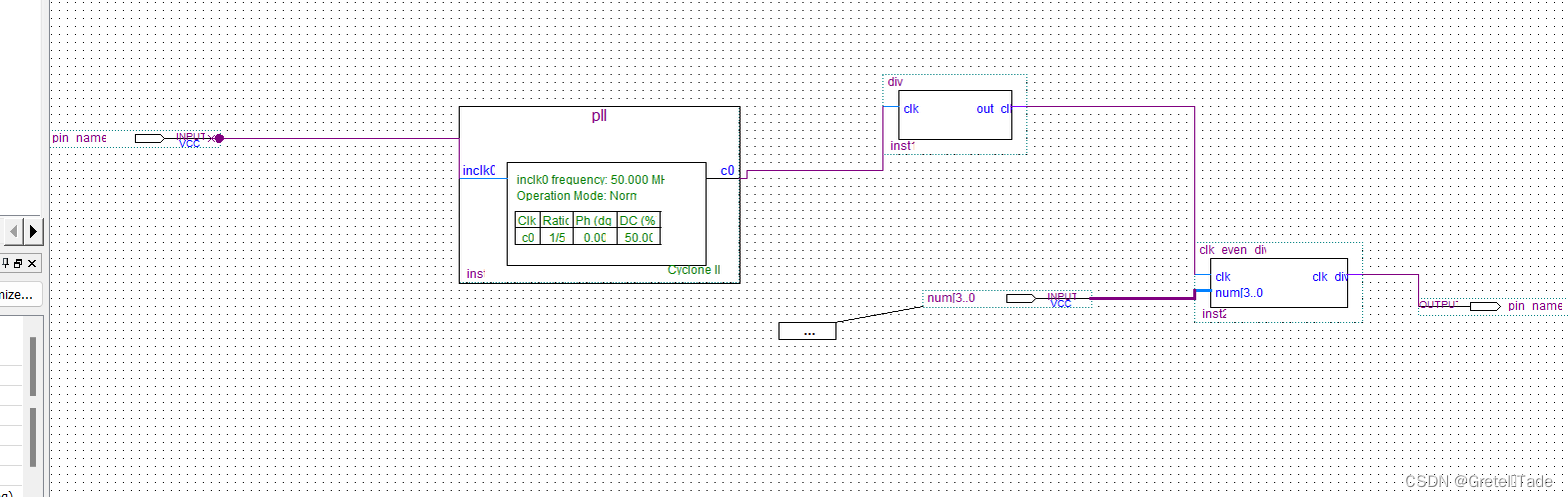

点开元器件,我们就可以看到这里生成了一个我们设置的锁相环了,拿出来用就行了 最后,进行电路图的连接了,我这里就已经连接好了。

最后,进行电路图的连接了,我这里就已经连接好了。

剩下的就是去进行引脚的配置了。

弄完之后,保存这个block文件,然后设置为顶层文件,最后点击编译运行

弄完之后,保存这个block文件,然后设置为顶层文件,最后点击编译运行

运行无误后,我们就可以进行烧录操作了。

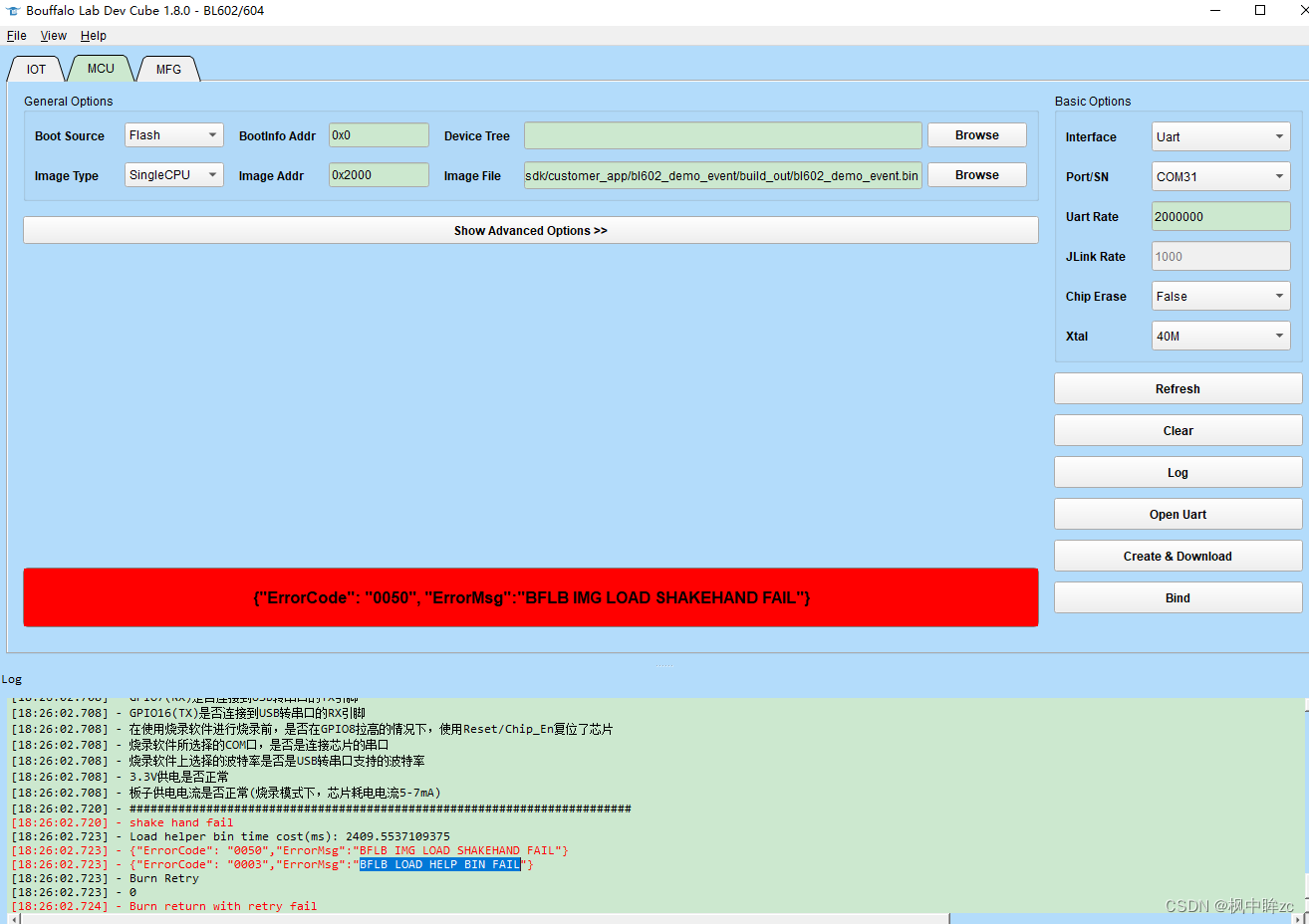

4.烧录文件

点开此处。

这里我们会看到,下面有一个芯片,这个也就是我们写好了的sof文件,然后就是通过你的电脑接口去连接到开发板,如果你看到上面有一个No Hardware的时候,你点击旁边的按钮进行接口设置,设置为USB接口即可(USB线连接了你的开发板就会自动显示出来的)。最后点击start就可以进行烧录了。

以上就是本期的全部内容了,我们下一次见!

分享一张壁纸: