FPGA_边沿检测电路设计

- 边沿检测原理图

- 波形图分析

- 实现方法

- 方法一:与逻辑实现

- 方法二:或逻辑实现

- 方法三:与逻辑实现

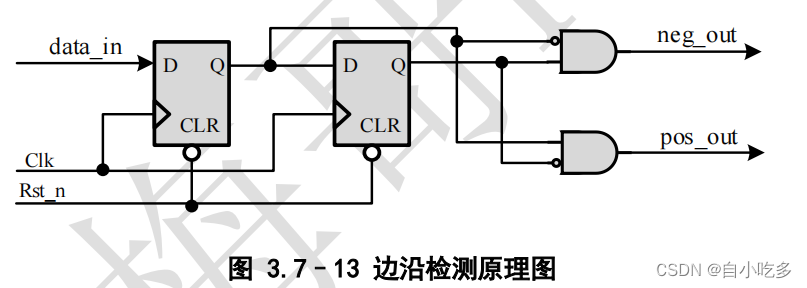

边沿检测原理图

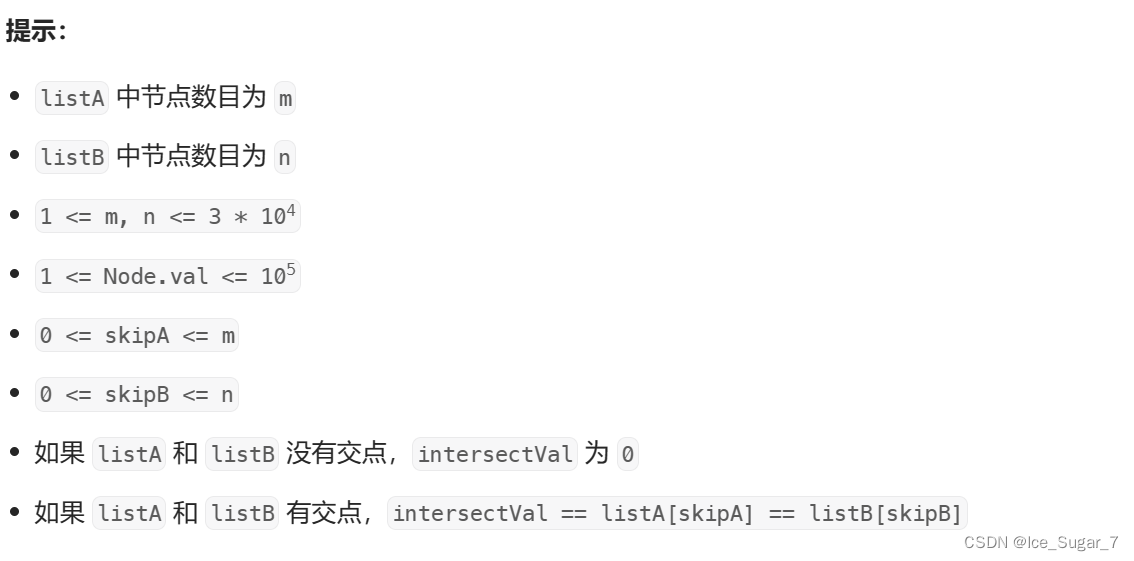

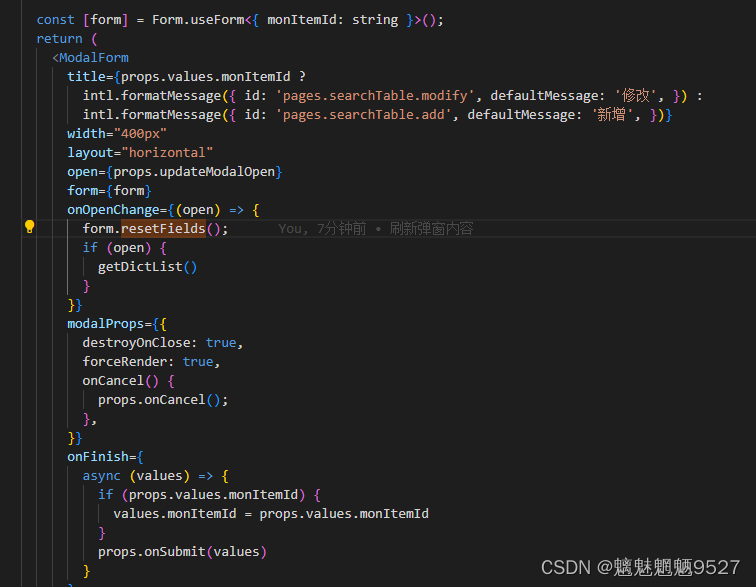

由状态转移表可以看出,其转换条件中需要检测到下降沿以及上升沿,而边沿检测其原理就是利用寄存器在时钟信号的控制下,输入状态即为下一时刻输出状态这一特性进行比较判断,如下图所示。

其检测过程,可以假设 data_in 从 0 变 1,也就是上升沿:

- 第一个时钟到来,第一个寄存器 regA_data 的输出为 0;

- 第二个时钟沿到来后第一个寄存器输出为 1,第二个寄存器输出此时为0,这样对两个寄存器输出进行相关组合逻辑运算则可检测出上升沿;

- 同理 data_in 从 1 变为 0,也就是下降沿:

- 第一个时钟到来,第一个寄存器 regA_data 的输出为 1;

- 第二个时钟沿到来后第一个寄存器输出为 0,第二个寄存器输出此时为1。

本部分逻辑设计如下,这样就实现了当有上升沿时信号 pedge 就会产生一个时钟周期的高电平,当有下降沿时信号 nedge 也会产生一个时钟周期的高电平,没有上升沿或者下降沿变化时 pedge 以及 nedge 保持低电平状态。这里使用的“!”是逻辑非运算,对 4’b0110 逻辑非运算后是 4’b0000;而“~”是按位取反,对 4’b0110按位取反后是 4’b1001。

reg key_tmpa,key_tmpb;

wire pedge,nedge;

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)begin

key_tmpa <= 1'b0;

key_tmpb <= 1'b0;

end

else begin

key_tmpa <= key_in_sb;

key_tmpb <= key_tmpa;

end

assign nedge = !key_tmpa & key_tmpb;

assign pedge = key_tmpa & (!key_tmpb);

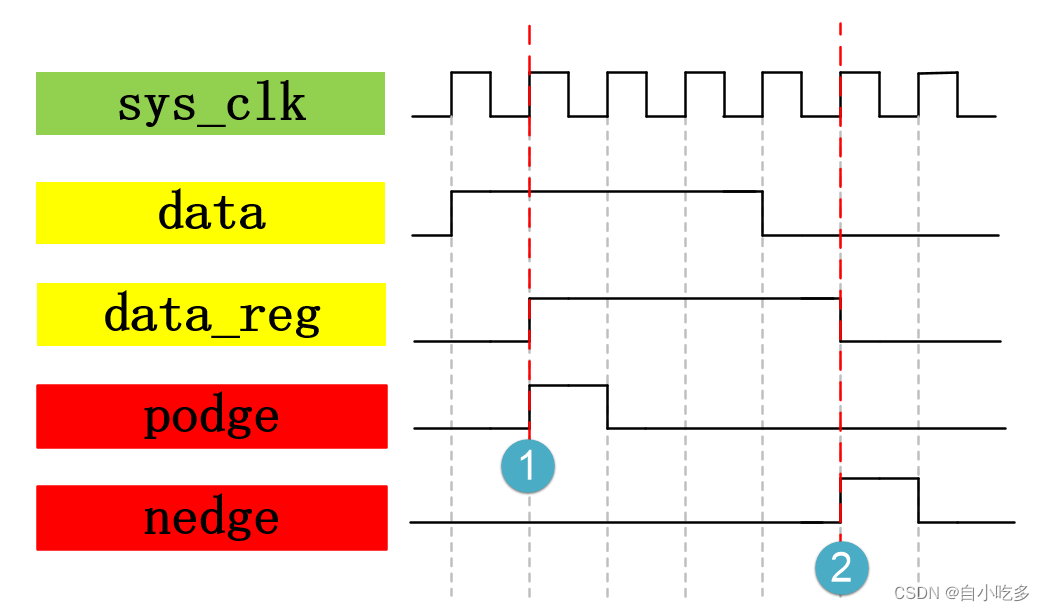

波形图分析

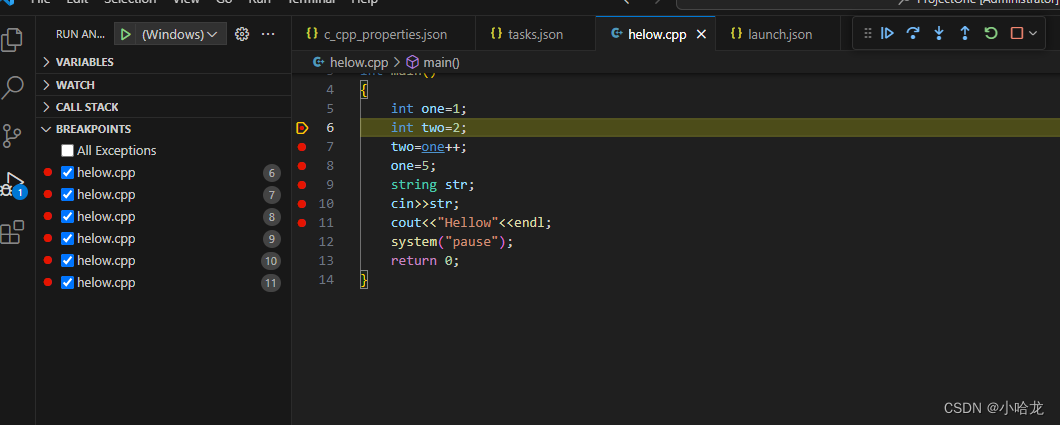

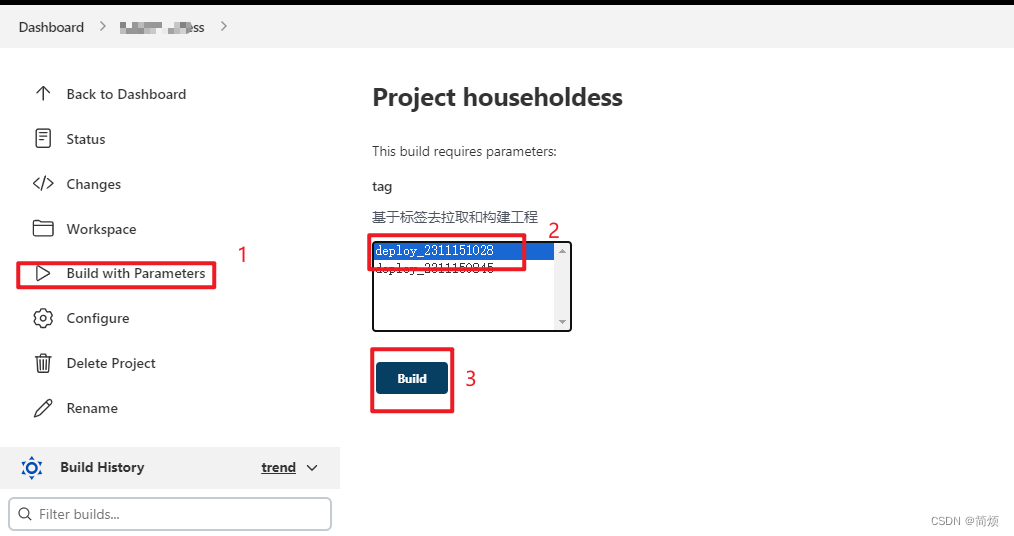

我们该如何准确找到这个下降沿呢?这就引入了另一个新的知识——边沿检测。边沿检测主要作用是能够准确的识别出单比特信号的上升沿或下降沿,也就是我们希望当上升沿或下降沿来到时,能够产生一个唯一标识上升沿或下降沿的脉冲信号来告诉我们上升沿或下降沿来了,我们就可以根据这个脉冲信号作为后续电路功能的启动。如下图所示,我们对同一信号打一拍后在①位置处就可以检测到上升沿,使之拉高一个时钟的脉冲;在②位置处可以检测到下降沿,使之拉高一个时钟的脉冲。要实现这个功能,我们该如何编写代码呢?

上升沿检测核心代码:在①处检测到 data 为高电平且 data_reg 为低电平时,表示有上升沿产生。

实现方法

方法一:与逻辑实现

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

podge <= 1'b0;

else if((data) && (~data_reg)) //核心逻辑

podge <= 1'b1;

else

podge <= 1'b0;

方法二:或逻辑实现

01 always@(posedge sys_clk or negedge sys_rst_n)

02 if(sys_rst_n == 1'b0)

03 podge <= 1'b0;

04 else if((~data) || (data_reg)) //核心逻辑

05 podge <= 1'b0;

06 else

07 podge <= 1'b1;

下降沿检测核心代码:在②处检测到 data 为低电平且 data_reg 为高电平时,表示有下

降沿产生,和上升沿的情况刚好相反。

方法三:与逻辑实现

01 always@(posedge sys_clk or negedge sys_rst_n)

02 if(sys_rst_n == 1'b0)

03 nedge <= 1'b0;

04 else if((~data) && (data_reg)) //核心逻辑

05 nedge <= 1'b1;

06 else

07 nedge <= 1'b0;

方法二:或逻辑实现

always@(posedge sys_clk or negedge sys_rst_n)

02 if(sys_rst_n == 1'b0)

03 nedge <= 1'b0;

04 else if((data) || (~data_reg)) //核心逻辑

05 nedge <= 1'b0;

06 else

07 nedge <= 1'b1;

注:上面的例子是用时序逻辑实现的,和上图所示波形完全一致。其核心逻辑也可以结合三目运算符用组合逻辑 assign 来实现,会使 podge 和 nedge 检测到上升沿和下降沿的脉冲均会提前一拍。希望大家能够记住边沿检测的核心逻辑以方便使用,当看到类似的代码也可以反推出检测的是上升沿还是下降沿。