目录

一、操作结构和流程( Operational Structure and Flow)

二、仿真任务概述(Simulation Task Overview)

三、仿真基本步骤( Basic Steps for Simulation)

3.1 基本概念

3.1.1 文件和库映射(Files and Map Libraries)

3.1.2 什么是库(What is a Library?)

3.1.3 资源库(Resource Libraries)

3.2 基本步骤

3.2.1 Step1 — Create Work and Resource Libraries

3.2.2 Step2 — Compile the Design

3.2.3 Step3 — Optimize the Design

3.2.4 Step4— Load the Design for Simulation

3.2.5 Step5 — Simulate the Design

3.2.6 Step 6 — Debug the Design

四、总结

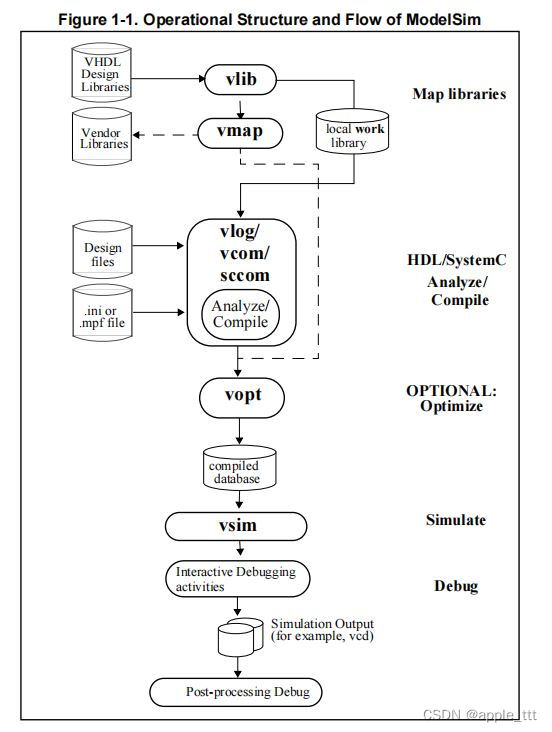

一、操作结构和流程( Operational Structure and Flow)

下图说明了使用ModelSim验证设计的结构和一般使用流程。

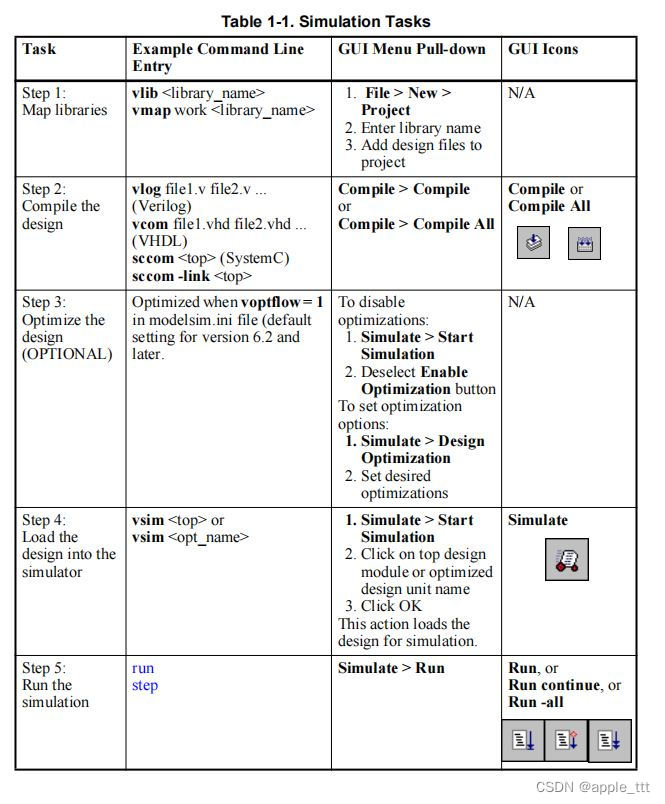

二、仿真任务概述(Simulation Task Overview)

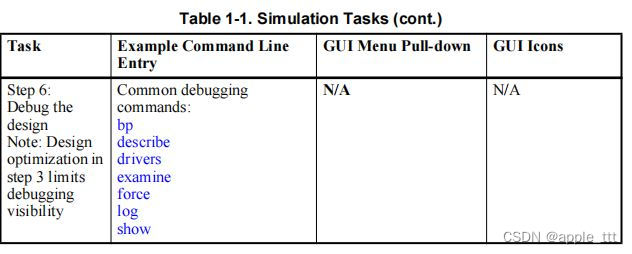

下表提供了在ModelSim中编译、优化、加载和模拟设计所需的任务的参考。

三、仿真基本步骤( Basic Steps for Simulation)

3.1 基本概念

本节描述了使用ModelSim模拟设计所需的文件类型和基本过程。

3.1.1 文件和库映射(Files and Map Libraries)

你需要一些文件来通过Modelsim进行你的仿真。

- 设计文件(VHDL and/or Verilog VHDL, Verilog, and/or SystemC),包括设计的激励。

- 库(工作库和资源库)

- modelsim.ini文件(由库映射命令自动创建)。

3.1.2 什么是库(What is a Library?)

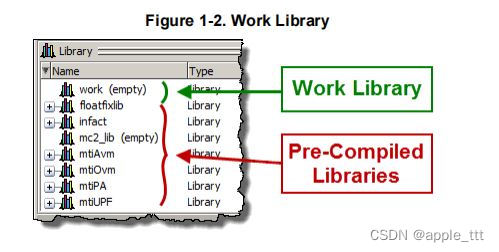

库是文件系统上的一个位置,ModelSim在这里存储用于仿真的数据。ModelSim在仿真之前使用一个或多个库来管理数据的创建。一个库还有助于简化仿真调用。

你可以通过以下方式使用库:

- 作为一个包含你的设计的编译后版本的本地工作库

- 作为一个资源库

3.1.3 资源库(Resource Libraries)

资源库通常是不变的,并作为一部分设计的资源。你可以创建自己的资源库,也可以由另一个设计团队或第三方提供它们。

资源库示例:

- 团队的共享信息

- 供应商库

- 包

- 以前编译过的关于你自己的工作设计的元素

ModelSim使用安装树中提供的预编译资源库,而不是在每次仿真时编译所有设计资源数据。使用预编译库有助于减少在编译和模拟启动期间的错误。此外,如果你对单个Verilog模块进行了更改,那么ModelSim将只重新编译该模块,而不是在设计中的所有模块。

3.2 基本步骤

3.2.1 Step1 — Create Work and Resource Libraries

第一步——创建工作和资源库。在编译源文件之前,必须使用vlib命令创建一个工作库,以便在其中存储编译结果。工作库的内容将在您重新编译和更新设计时发生更改。

默认情况下,Vlib会创建一个"flat"库类型。与传统库类型相比,平面库将库信息压缩成一个小的文件集合。这补救了在非常大型的库中看到的性能和容量问题。

步骤:

3.2.2 Step2 — Compile the Design

第二步——编译设计。收集设计文件并创建工作目录之后,将编译设计。你必须根据用于编写设计代码的编程语言来选择适当的编译器命令。对于verilog语言来说,使用的命令是vlog。

你可以以任何顺序编译Verilog文件,因为它们并不依赖于顺序。例如:

vlog gates.v and2.v cache.v memory.v3.2.3 Step3 — Optimize the Design

第三步——优化设计。优化是一个可选的步骤,它可以通过限制设计对象的可见性来提高性能。ModelSim使用vopt命令执行全局优化。

在命令行输入如下指令:

vopt top -o topopt其中,top是是已编译好的顶层模块的名称。-o topopt 指定设计的优化版本的名称。

3.2.4 Step4— Load the Design for Simulation

在编译设计后,您需要使用任何顶层模块的名称(多个设计只能包含一个顶层模块),使用vsim命令加载设计。例如,如果您的顶层模块被命名为“测试台”和“全局模块”,那么就调用仿真器vsim testbench globals 。

在命令行输入如下指令:

vsim testbench globals其中,testbench 和 globals 是两个顶层模块。

仿真器加载顶层模块后,在设计层次中迭代加载实例化的模块和udp,通过连接端口和解析层次引用将设计连接在一起。

3.2.5 Step5 — Simulate the Design

成功加载设计后,模拟时间将设置为零,并且必须输入运行 run 才能开始模拟。用于运行仿真的基本命令有:

- add wave

- bp

- force

- run

- step

3.2.6 Step 6 — Debug the Design

ModelSim GUI提供了许多对调试设计很有用的命令、操作和窗口。此外,您还可以使用命令行来运行以下基本的模拟命令以进行调试。

- describe

- drivers

- examine

- force

- log

- checkpoint

- restore

- show

四、总结

本文介绍了 Modelsim 进行验证时候的基本操作结构和流程,简要说明了在ModelSim中编译、优化、加载和模拟设计所需的任务,解释了Modelsim中库的基本概念。