文章目录

-

- 一、问题描述

- 二、verilog源码

- 三、仿真结果

一、问题描述

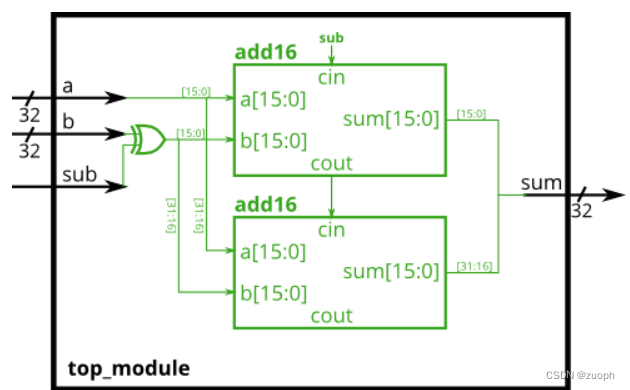

可以通过将其中一个输入变为负来从加法器构建加法器-减法器,这相当于将其输入反相然后加 1。最终结果是一个可以执行两个操作的电路:(a + b + 0) 和 (a + ~b + 1)。如果您想更详细地解释该电路的工作原理,请参阅维基百科。

加减法器维基百科

在下面构建加法器-减法器。

您将获得一个 16 位加法器模块,您需要实例化该模块两次:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

使用 32 位宽的 XOR异或 门在 sub为1时 反转 b 输入。(这也可以看作是 b[31:0] 与sub异或后复制 32 次。请参阅复制运算符。同时将 sub 输入连接到加法器的进位。

二、verilog源码

mod