1、错误现象

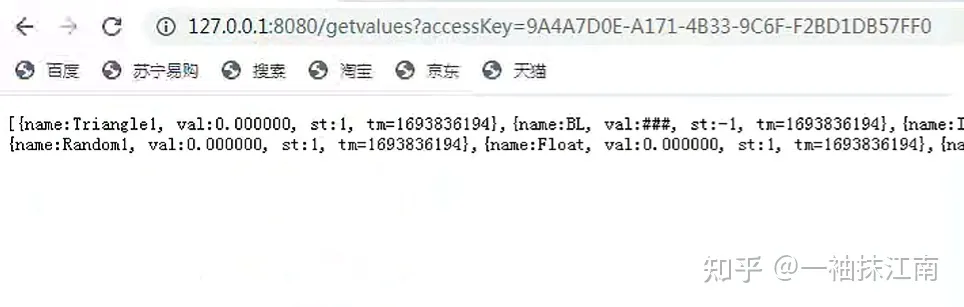

错误现象如下,在IIC数据传输8位数据后,IIC DEBUG的应答位无法显示应答位

2、错误原因

我们打开信号传输的示波器,直接去查看IIC从机校验位的数据波形,可以看到从机示波器显示的的波形为半高ACK,那错误原因就理所当然的了。

我们不妨分析一下,IIC在等待从机校验的时候,通常会将SDA和SCL拉高,SCL拉高是用于接收,SDA拉高是默认将从机应答置为到无应答或忙碌状态,然后在等待从机应答将SDA拉低,表示IIC通讯的应答位。

那在上述波形中,我们可以看到在上一个8位数据位传输完后,SDA和SCL都拉高了,但是SDA的数据位只出现了半高的数据信号,这是为什么呢,那必然是传输完八位数据后,从机自然而然地拉低了SDA以表示了应答信号,但是又由于从机的某些原因(下文会讲到),导致SDA信号无法完全拉低,就出现了信号半高的状态,IIC DEBUG无法识别半高SDA信号,所以显示?

当然这样表示从机同样收到了应答,IIC是可以正常通讯的,但是IIC DEBUG无法显示而言。

3、解决方案

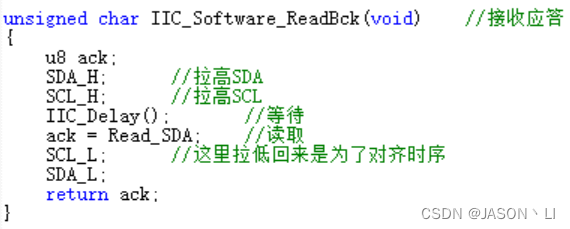

软件解决方案:

由于问题原因出在IIC的从机应答无法完全拉低,那我们可以在接收应答信号前直接将SDA拉低,然后再接收从机信号,当应答信号无应答或忙碌而置为时会拉高SDA,出现SDA半高的情况,这样同样会出现?情况,但是我们就只需要将?当成无应答就好。那当应答信号成功发送,无置为后,那IIC DEBUG自然而然就正常了。(当然这种硬件问题用软件解决肯定不是最佳方案,但是胜在软件解决的方案方便实用)

硬件解决:

如果要通过硬件解决的话,就得分析一下为何会出现上述的半高情况了,而这里我是参考一位大佬的分析结果的

问题原因为:ACK响应位出现半高电平

这种情况说白了就是IIC链路上的器件接口不是纯粹的OD/OC,一般多出在可编程器件上,比如说MCU,CPLD。如果IIC总线上挂了多个器件,在ACK位的时候,有器件管脚没有配置为OD或者OC,导致芯片内部将该管脚拉高,此时链路上其他的器件又需响应想拉低总线,如果两边链路上都存在串阻,则通过电阻分压会出现中间电平;如果没有串阻,或者串阻过小,则可能烧坏器件(灌电流)。总之非常危险,这个半高电平可能出现在任何位置,只不过ACK位容易被忽视,更容易出问题。

原文链接:IIC的ack信号为何会出现半高电平?_iic ack-CSDN博客

当然硬件方法的解决方案我还没有找到,如果有大哥知道怎么用硬件解决,可以分享一下,不胜感激,当然我也在不断探讨,要是我找到硬件解决方案我会第一时间发出来的。