always的block之间,采用并行执行

always之内,采用非阻塞赋值,为顺序执行

一些代码分析

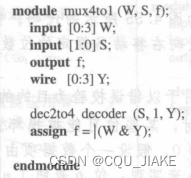

这个把使能信号和W信号组合在一起,进行case语句,即只有合并信号最高位为1时,才进行操作

always后面要写@,assign不用

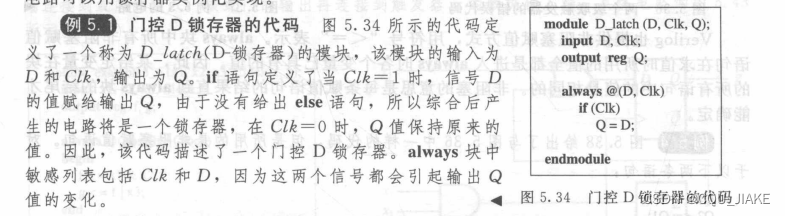

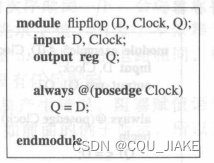

存储元件代码

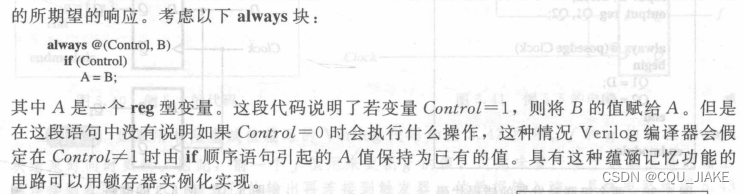

这没有期望的边沿,就是只要发生变化就会触发

加上posedge,negedge就可以标记期望的边沿

按位操作与逻辑操作

一个操作符就是按位操作,两个就是逻辑操作

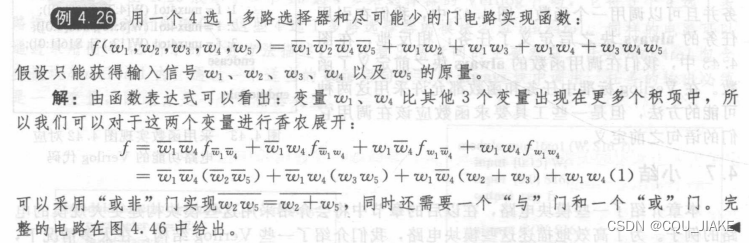

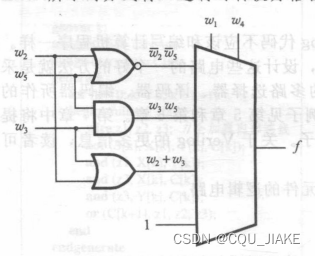

香浓展开与选择器实现电路

对四变量提取w1,做出香浓展开,则w1为选择信号,其他w2,w3,w4组合成被选择的信号

提取出n个量,就有n个选择信号,就需要传进2^n的被选择信号

例一

香浓展开的提取项,就是选择器的选择信号

对两个量进行展开,考虑出所有情况

对于各子项里没有出现的提取项,可以放到任意一个里去,但必须有对应的提取项,最后的目标是各种情况能凑齐子项

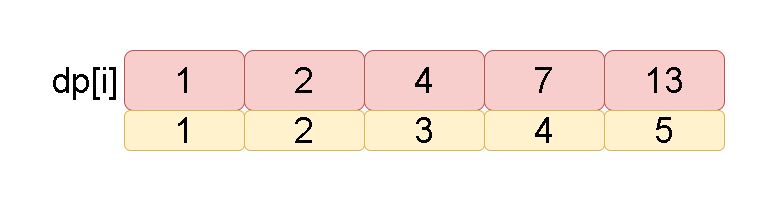

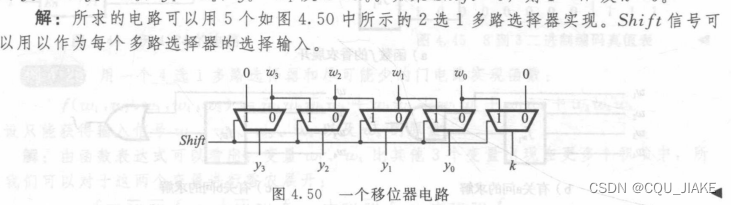

移位器

就是移位信号为1时,y3选为0,y2为w3,y1为w2,y0为w1,即整体左移一位

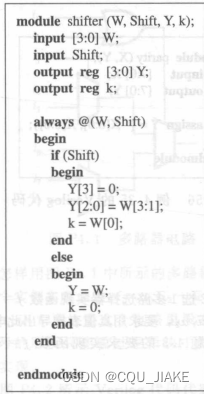

代码

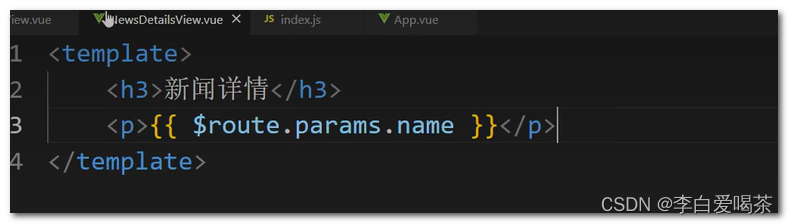

由于采用了always,所以输出信号在模块内要定义成reg

由于采用了always,所以输出信号在模块内要定义成reg

always@(W,Shift)就是说,只要这里面有一个变化,就进行触发

如果用assign就是时刻都在触发,而always是标定信号发生变化时才触发

另一种实现![]()

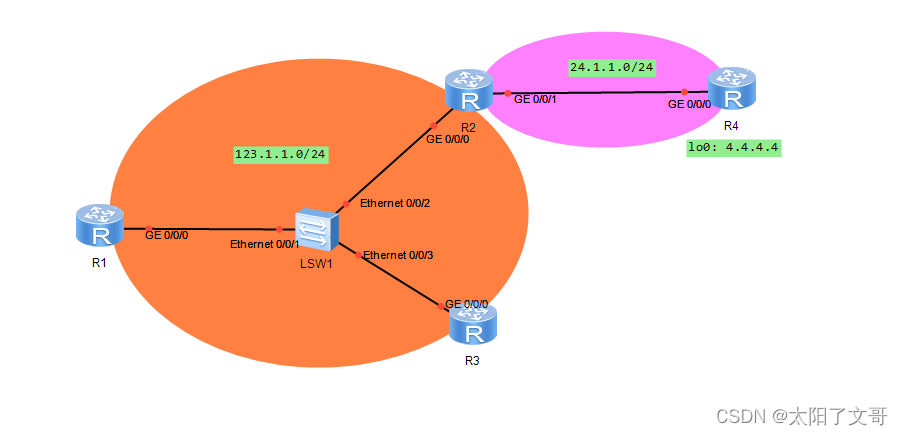

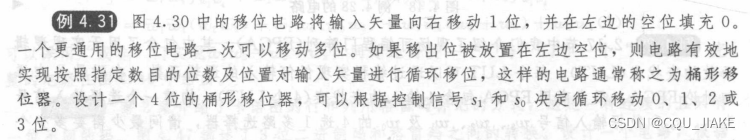

桶形移位器

就是一个可以指定移动位数的移位器,并且循环

y3,y2,y1,y0是实际输出的每位,每位都是一个四选一选择器,被选择信号就是循环出现的四个信号,然后s1s0组合在一起构成移位信号对每个选择器进行选择。

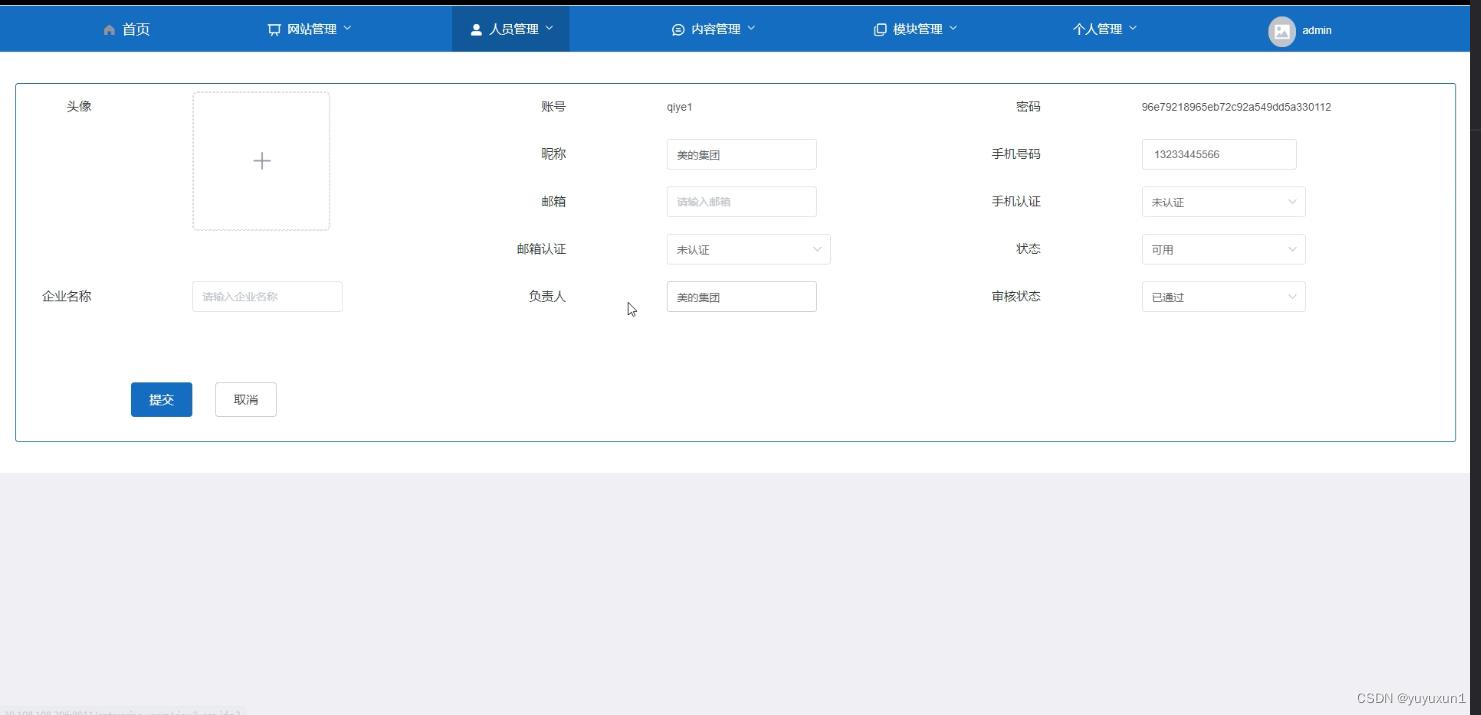

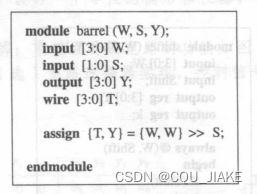

代码

多位宽信号在运算时,是整成实际大小意义进行的

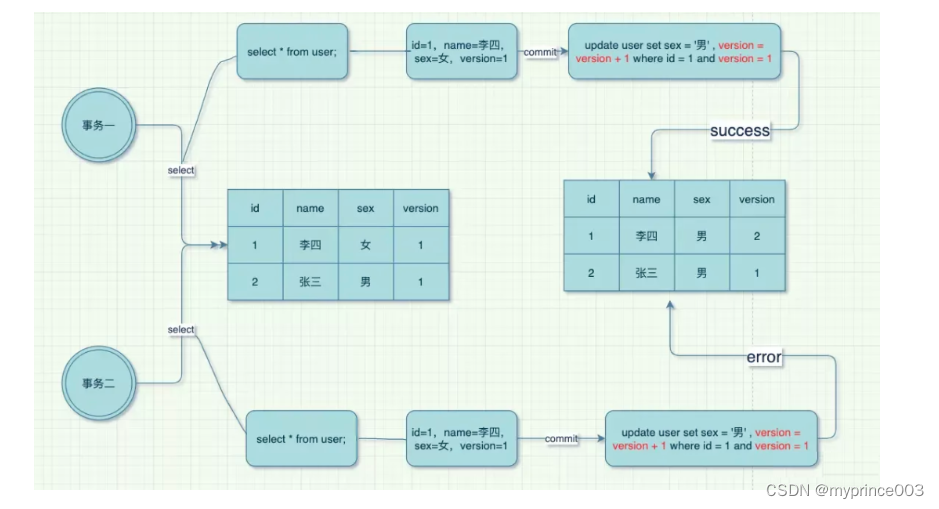

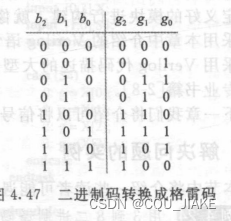

二进制转格雷码函数

就是从低位与高位两两异或,最高位独自保留

异或实现

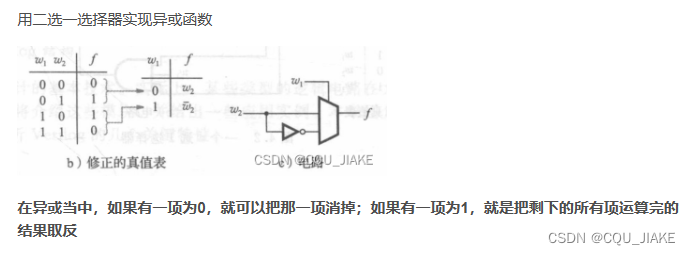

选择器的上是0,下是1的情况,即异或式中,认为一个信号是选择信号,剩下的所有信号的异或运算结果和它的非为被选择信号,选择信号为0时,不做改变,直接消掉,即输出剩下所有的运算结果,即选择上部直接出;为1时,对前面的所有信号的异或运算结果取反,输出取反后的结果;

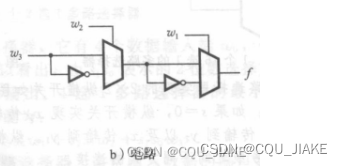

三个项异或电路

n个项就是往后不断递归加二选一选择器,延长电路长度

这个原理也可说明异或函数能检验一串二进制数的1的个数

如果个数为奇数,则输出结果为1;

如果个数为偶数,则输出结果为0;