一.简介

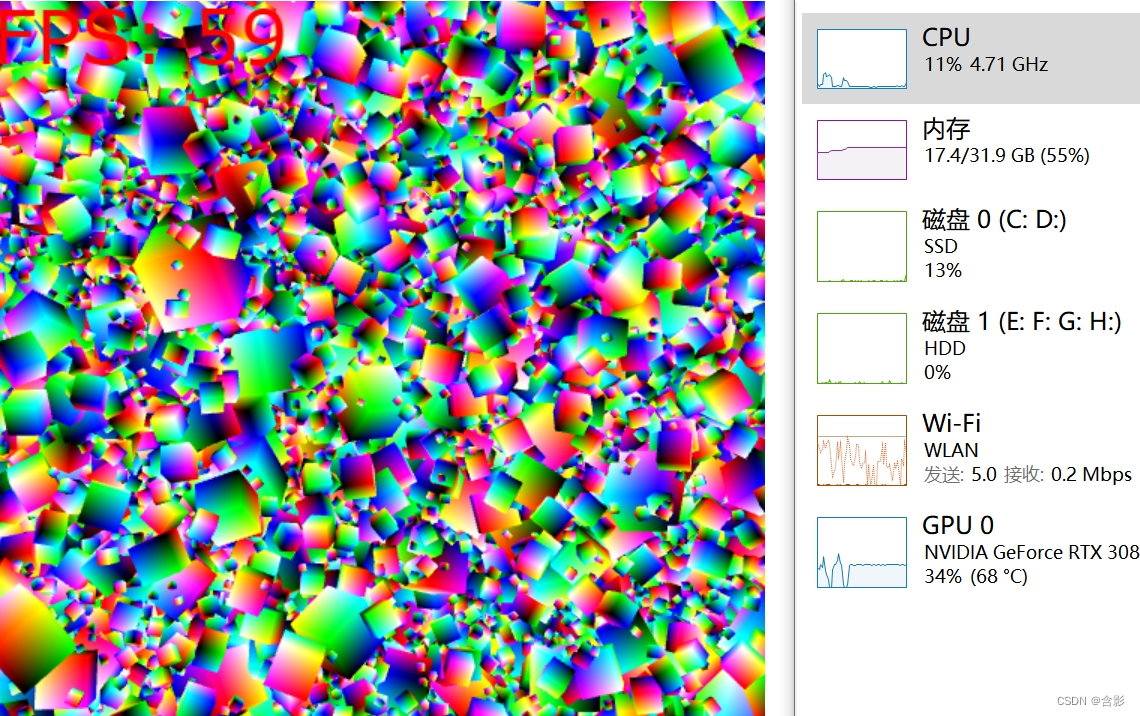

DDR3 SDRAM,以其单位存储量大、高数据带宽、读写速度快、价格相对便宜等优点 吸引了大批客户,占领市场较大份额。同时,作为内存条中不可缺少的一部分,DDR3 SDRAM 在计算机领域也占有一席之地。

要掌握 DDR3 SDRAM 的基本概念、数据存取原理、操作命令以及操作时序等相关知识。在掌 握 DDR3 SDRAM 的相关理论知识后,讲解 AXI4 接口,并且使用该接口配置 Xilinx 的 MIG IP 核,设计一个可进行读写操作的 DDR3 SDRAM 控制器,并上板验证。

1.DDR3 SDRAM基础概念

DDR3 SDRAM 英 文 全 称 “ Double-Data-Rate Three Synchronous Dynamic Random Access Memory”,译为“第三代双倍速率同步动态随机存取内存”或“同步动态随机存储 器”,是动态随机存储器(Dynamic Random Access Memory,简称 DRAM)的一类。 同步、动态、随机是其性能特点的外在说明。

双倍速率(Double-Data-Rate):DDR3 SDRAM 存储器与 SDRAM 有一个很大的不同, DDR3 SDRAM 或者说带 DDR 开头的。包括 DDR1、DDR2、DDR3、DDR4、DDR4,他们都有一个很大的相似点,就是双边沿输出输入数据,通俗来讲就是在一个周期内输出 2 次 数据,上升沿输出一次数据,下降沿输出一次数据。而 SDRAM 则是在一个周期内的上升 沿输出一次数据,下降沿不输出,所以同频率的 DDR3 SDRAM 与 SDRAM 相比速度快一 倍。

同步(Synchronous):与通常的异步 DRAM 不同,DDR3 SDRAM 存在一个同步接口, 其工作时钟的时钟频率与对应控制器(CPU/FPGA)的时钟频率相同,并且 SDRAM 内部的命 令发送与数据传输均以此时钟为基准,实现指令或数据的同步操作;

动态(Dynamic):DDR3 SDRAM 需要不断的刷新来保证存储阵列内数据不丢失;

随机(Random):数据在 DDR3 SDRAM 中并不是按照线性依次存储,而是可以自由指定地址进行数据的读写。

第一代 SDR SDRAM 采用单端时钟信号,SDRAM 只在时钟的上升沿进行数据采样; 而后面的四代 SDRAM 由于工作频率比较快,所以采用可降低干扰的差分时钟信号作为同步时钟,双沿采样,速度更快,且功耗更低。同时技术的不断发展、制造工艺的不断提 高,使得五代 SDRAM 的更新过程中,集成度越来越高、内核电压越来越低(SDR:3.3V、 DDR:2.5V、DDR2:1.8V、DDR3:1.5V、DDR4:1.2V),这也是 SDRAM 速度提高、功耗降低的重要原因。

由于 DDR3 SDRAM 需要不断刷新来保证数据的可靠性,以及行列地址线分时复用等原因,使其对操作时序的 要求较为严格,进而导致控制逻辑较为复杂。

2.DDR3 SDRAM存取原理

对于 DDR3 SDRAM,我们将类比于单元格的存储空间称之为存储单元,N(行列个数乘积)个存储单元构成一个存储阵列,这个存储阵列我们称之为一个逻辑Bank(LogicalBank)简称 L-Bank、Bank)。DDR3 SDRAM 内部并不是一个全容量的 L-Bank,而是分割为若干个 L-Bank,目前大多为 4 个。若干 L-Bank 的分割,原因有二,一是技术、成本等诸多因素;二是由于 DDR3 SDRAM 的工作原理限制,单一 L-Bank 可能会造成非常严重的寻址冲突,大幅度降低内存效率。

这样一来,在对 DDR3 SDRAM 进行数据存取时,要先确定 L-Bank 地址,定位到指定 逻辑 Bank,再依次确定行地址和列地址,选中存储单元,进而进行数据的存取操作,而且 一次只能对一个 L-Bank 的一个存储单元进行操作。

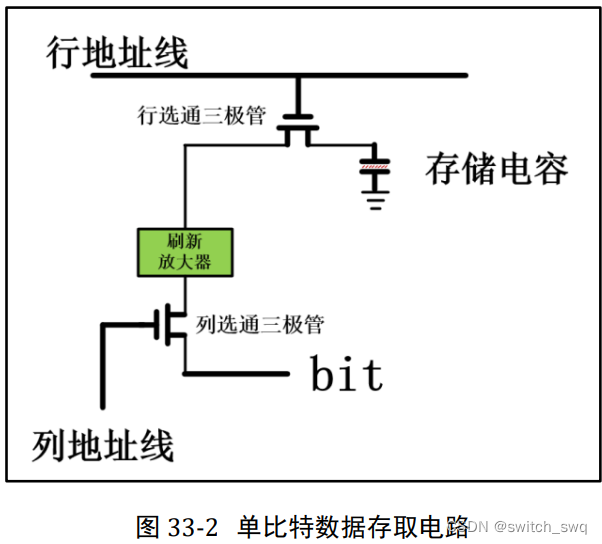

DDR3 SDRAM 的基本存储单位是存储单元,而一个存储单元的容量为若干个 Bit,对 于 DDR3 SDRAM 而言就是芯片的位宽,每个 Bit 存放于一个单独的存储体中,存储体是利 用电容能够保持电荷以及可充放电的特性制成,主要由行选通三极管、列选通三极管、存 储电容以及刷新放大器构成。电容所存储的电荷会随时间慢慢释放,这就需要不断刷新为 电容充电,以保证存储数据可靠性。

将每个存储单元简化为单 Bit 的存储体,再将若干存储体排列为矩阵,同一行将行地 址线相连,同一列将列地址线相连,就构成了一个存储阵列的简化模型。

3.DDR3 SDRAM器件引脚

注:x4、x8、x16 分别表示位宽 4bit、8bit、16bit;#符号表示信号为低电平有效;短 划线-表示 x8 和 x4 引脚功能相同,x16 引脚功能相同与前者不同,我们的是 x16。

我们以镁光公司生产的、容量为 4Megx16x4Banks 的 DDR3 SDRAM 芯片为例,对其做一下功能介绍。

注:表格中某些信号只介绍了后文设计实验中所涉及到的功能,更多功能介绍请查阅 芯片对应数据手册。

SDRAM 内部功能框图:

DDR3 SDRAM 内部包含一个逻辑控制单元,内部包含模式寄存器和 命令解码器。外部通过 CS_N、RAC_N、CAS_N、WE_N 以及地址总线向逻辑控制单元输 入命令,命令经过命令解码器进行译码后,将控制参数保存到模式寄存器中,逻辑控制单 元进而控制逻辑运行。

外部通过地址总线输入地址信息,地址信息在逻辑控制单元进行逻辑控制时起到辅助 作用,除此之外,复用的地址总线与 Bank 控制逻辑、行地址复用器、列地址计数锁存 器、列地址解码器等内部器件共同作用,精确选定存储阵列中与行列地址相对应的存储单 元,进而进行数据存取操作。

容量计算方法可简化为: 存储容量(Bit)=L-Bank 存储单元数×数据位宽(Bit)×L-Bank 个数

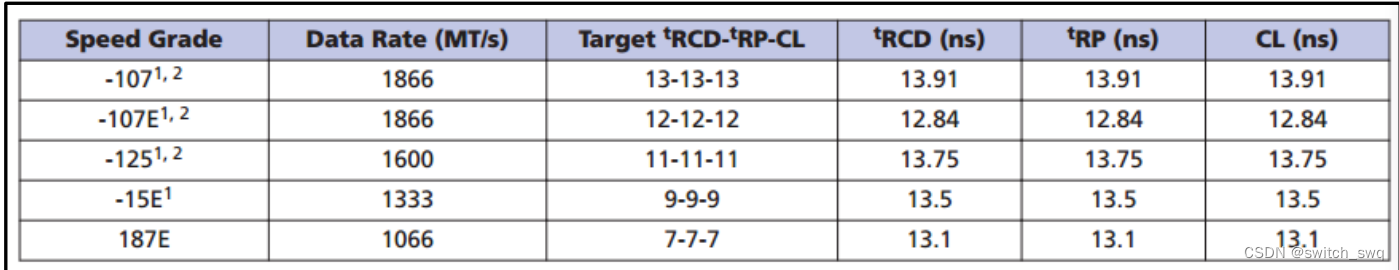

SDRAM 芯片的另一个概念:速度等级。DDR3 SDRAM 速度等级相关参数截图,具体见图

包括速度等级在内的 6 个相关参数。时钟频率(Clock Frequency),单位 MHz,所列举的具体参数为 SDRAM 正常工作的最高时钟频率,SDRAM 工作时只能等于 或低于这一时钟频率;tRCD 表示写入自激活命令到开始进行数据读写,中间所需的等待时 间,列举的数值表示等待时间的最小值,单位为 ns;tRP 表示自预充电指令写入到预充电完成 所 需 的 等 待 时 间 , 列 举 的 数 值 表 示 等 待 时 间 的 最 小 值 , 单 位 为 ns ; CL(CAS(READ)latency)列选通潜伏期,表示自数据读指令写入到第一个有效数据输出所需 等待时间,单位 ns;TargettRCD-tRP-CL 表示最大工作频率下,tRCD、tRP、CL 等待的最小时 钟周期数。

4.AXI 接口概述

Advancede Xtensible Interface,即高级可扩展接口,它是 ARM 公司 所提出的 AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。之所以要采 用 AXI4 接口对 ddr 进行读写是因为 Xilinx 的 mig ddr Ip 核,无论是 6 系列还是 7 系列还是 最新的 FPGA,都集成了 AXI4 接口,为了采用 AXI4 接口进行读写,后续可以兼容 xilinx 的其他 fpga,可复用性更强。

AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、总线的地址/控制和数据通道是分离的;

2、支持不对齐的数据传输;

3、支持突发传输,突发传输过程中只需要首地址;

4、具有分离的读/写数据通道;

5、支持显著传输访问和乱序访问;

6、更加容易进行时序收敛。

AXI4 协议支持以下三种类型的接口:

1、AXI4:高性能存储映射接口。

2、AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信。

3、AXI4-Stream:用于高速数据流传输,非存储映射接口。

在这里我们首先解释一下存储映射(MeamoryMap)这一概念。如果一个协议是存储 映射的,那么主机所发出的会话(无论读或写)就会标明一个地址。这个地址对应于系统 存储空间中的一个地址,表明是针对该存储空间的读写操作。AXI4 协议支持突发传输,主 要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite 为外设提供单个 数据传输,主要用于访问一些低速外设中的寄存器。而 AXI-Stream 接口则像 FIFO 一样, 数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速 AD、PCIe、DMA 接口等需要高速数据传输的场合。

5.AXI4 接口讲解

在本章我们重点介绍 AXI4 接口,它由五个独立的通道构成:

1、读地址 2、读数据 3、写地址 4、写数据 5、写响应

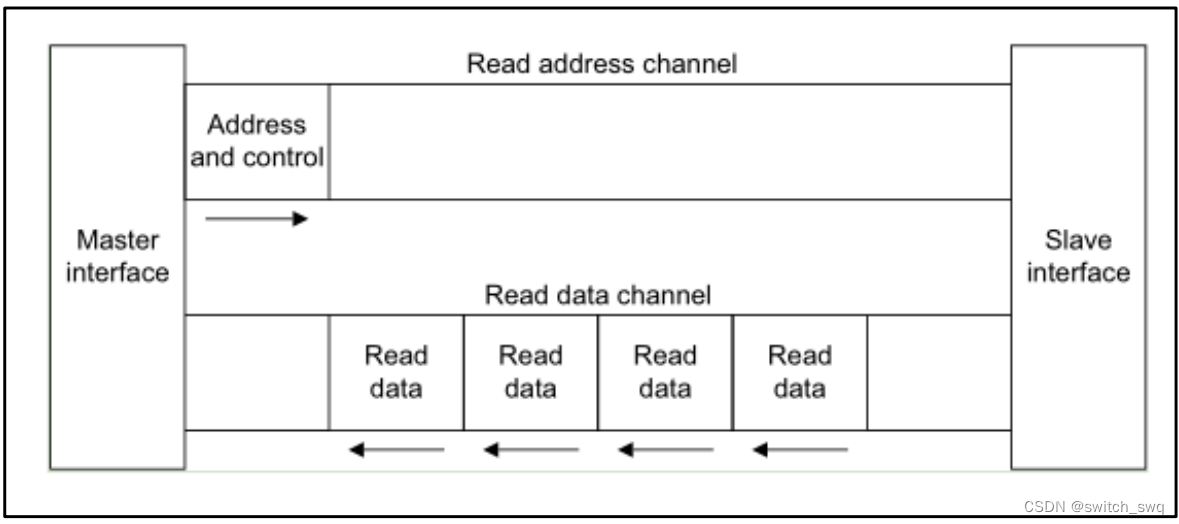

下面是使用读地址和读数据通道实现读传输过程的示意图:

从上图中可以看到,在一个读传输过程中,主机首先在读地址通道给出读地址和控制 信号,然后从机由读数据通道返回读出的数据。另外我们需要注意的是,这是一次突发读操作,主机只给出一个地址,从该地址连续突发读出四个数据。

写传输过程如下图所示,它用到了写地址、写数据和写响应三个通道:

主机在写地址 通道给出写地址和控制信号,然后在写数据通道连续突发写四个数据。从机在接收数据之 后,在写响应通道给出响应信号。

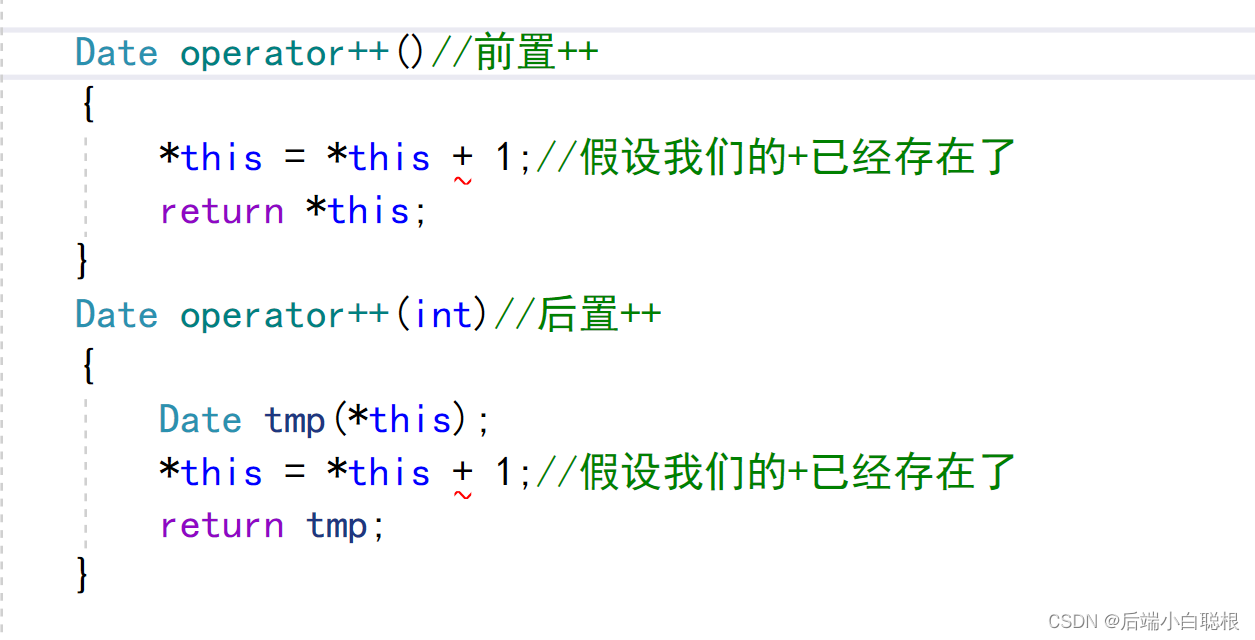

突发写时序:

AXI4 突发写可以分为 7 个状态,写空闲,写通道写地址等待,写通道写地址,写数据 等待,写数据循环,接受写应答,写结束这 7 种状态。之所以划分为 7 个状态是为了后续 写程序的状态机做准备。

写空闲:等待触发突发信号。

写通道写地址等待:准备好写地址 AWADDR,然后拉高 AWVALID。

写通道写地址:从机接受到 AWVALID,发出 AWREADY。

写数据等待:准备好数据 WDATA,拉高 WVALID。

写数据循环:从机接受 WVALID ,确认数据 WDATA 有 效 并 且接 受 , 发 出 WREADY,AXI 是突发传输:循环该操作到接受到 WLAST 最后一个数据标志位。

接受写应答:接受到从机发出的 BVALID,主机发出 BREADY。

写结束:拉低未拉低的信号,进入写空闲。

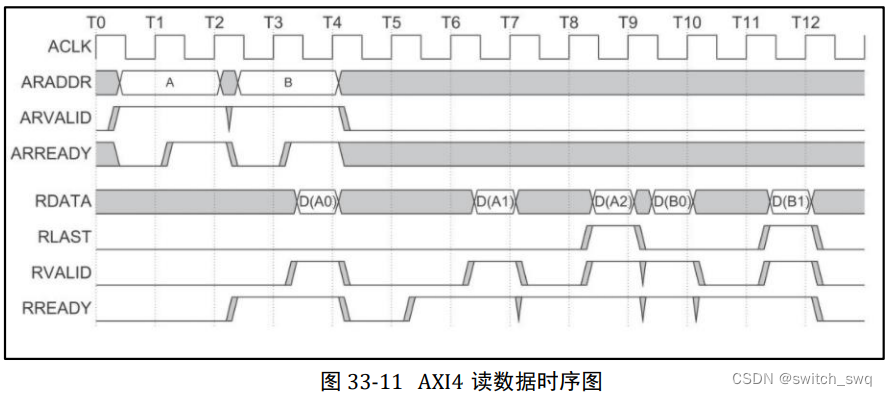

突发读时序:

AXI4 突发读可以分为 6 个状态,读空闲,读通道写地址等待,读通道写地址,读数据 等待,读数据循环,读结束这 6 种状态。之所以划分为 6 个状态是为了后续写程序的状态 机做准备。

读空闲:等待触发突发信号。

读通道写地址等待:准备好写地址 ARADDR,然后拉高 ARVALID。

读通道写地址:从机接受到 ARVALID,发出 ARREADY。

读数据等待:从机器准备好数据 WDATA,从机拉高 RVALID。

读数据循环:主机接受 RVALID,确认数据 RDATA 有效并且接受,发出 RREADY 给 从机,AXI 是突发传输:循环该操作到接受到 RLAST 最后一个数据标志位。

读结束:拉低未拉低的信号,进入读空闲。

从上面的时序图与时序分析可知两种关系必须被保持:

(1)读数据必须总是跟在与其数据相关联的地址之后。

(2)写响应必须总是跟在与其相关联的写事务的最后出现。

![[架构之路-245/创业之路-76]:目标系统 - 纵向分层 - 企业信息化的呈现形态:常见企业信息化软件系统 - 企业资源管理计划ERP](https://img-blog.csdnimg.cn/7eed4a732b4b4651ac4eb92a32e50b6e.png)