名称:温湿度计传感器DHT11控制数码管显示

软件:QuartusII

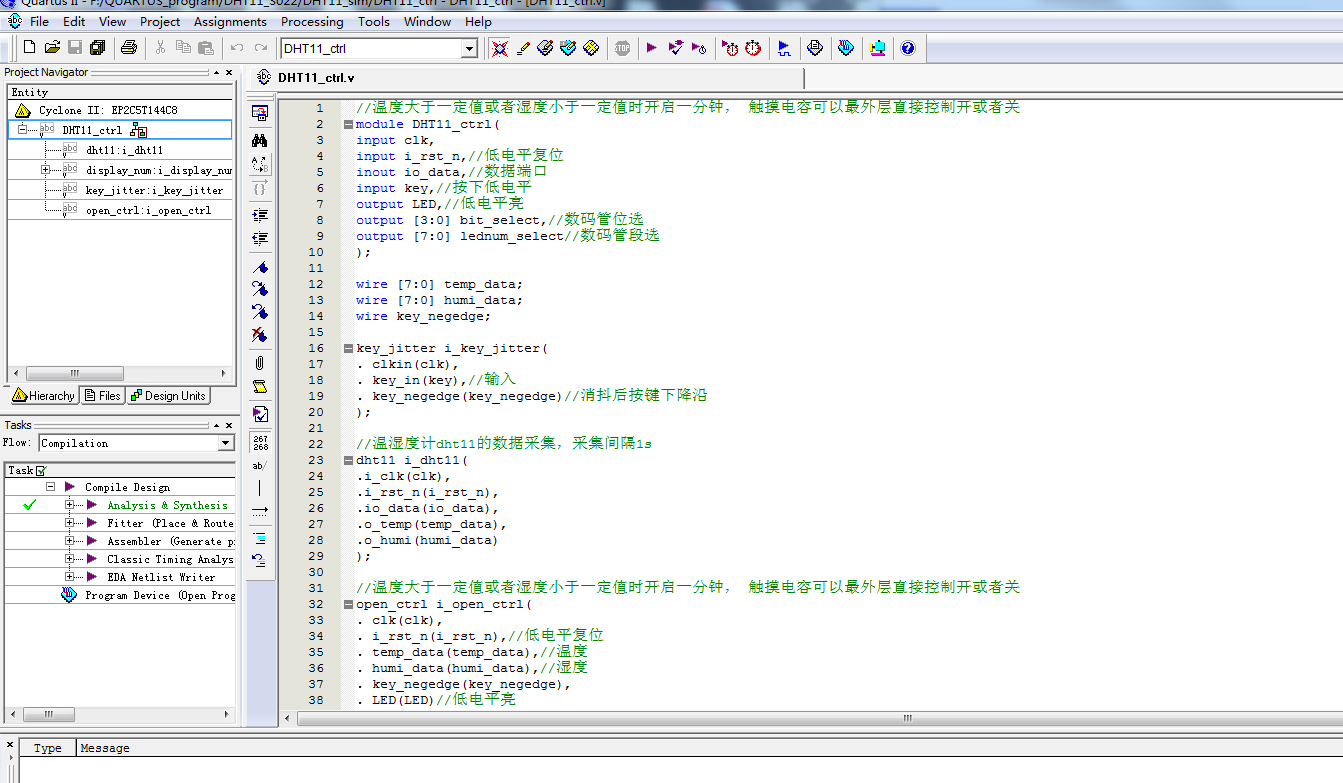

语言:Verilog

代码功能:

使用温湿度传感器DHT11采集环境的温度和湿度,并在数码管显示

本代码已在开发板验证

开发板资料:

大西瓜第一代FPGA升级板原理图.pdf

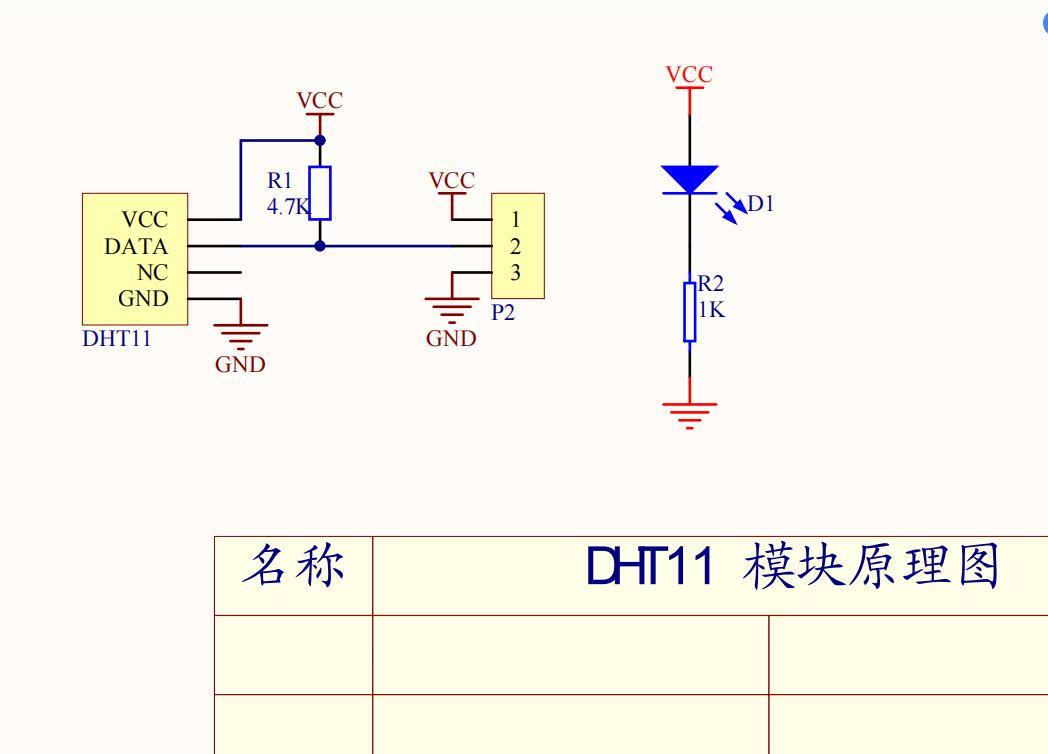

DHT11传感器电路图:

演示视频:温湿度计传感器DHT11控制数码管显示verilog_Verilog/VHDL资源下载

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

温湿度计传感器DHT11控制数码管显示verilog_Verilog/VHDL资源下载名称:温湿度计传感器DHT11控制数码管显示(代码在文末付费下载)软件:QuartusII语言:Verilog代码功能: 使用温湿度传感器DHT11采集环境的温度和湿度,并在数码管显示 本代码已在开发板验证 开发板资料:大西瓜第一代FPGA升级板原理图.pdf DHT11传感器电路图:演示视频:FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=220

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=220

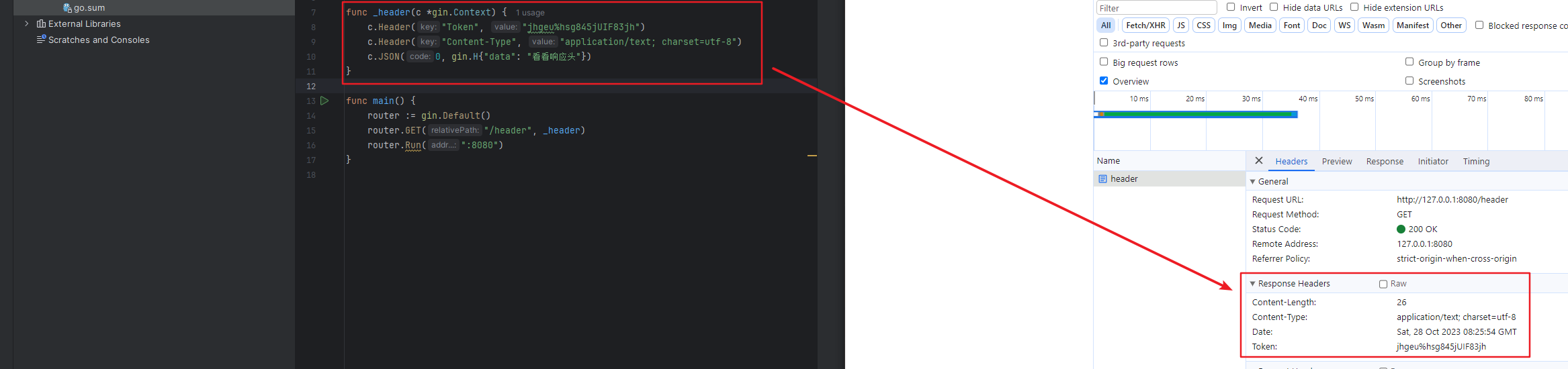

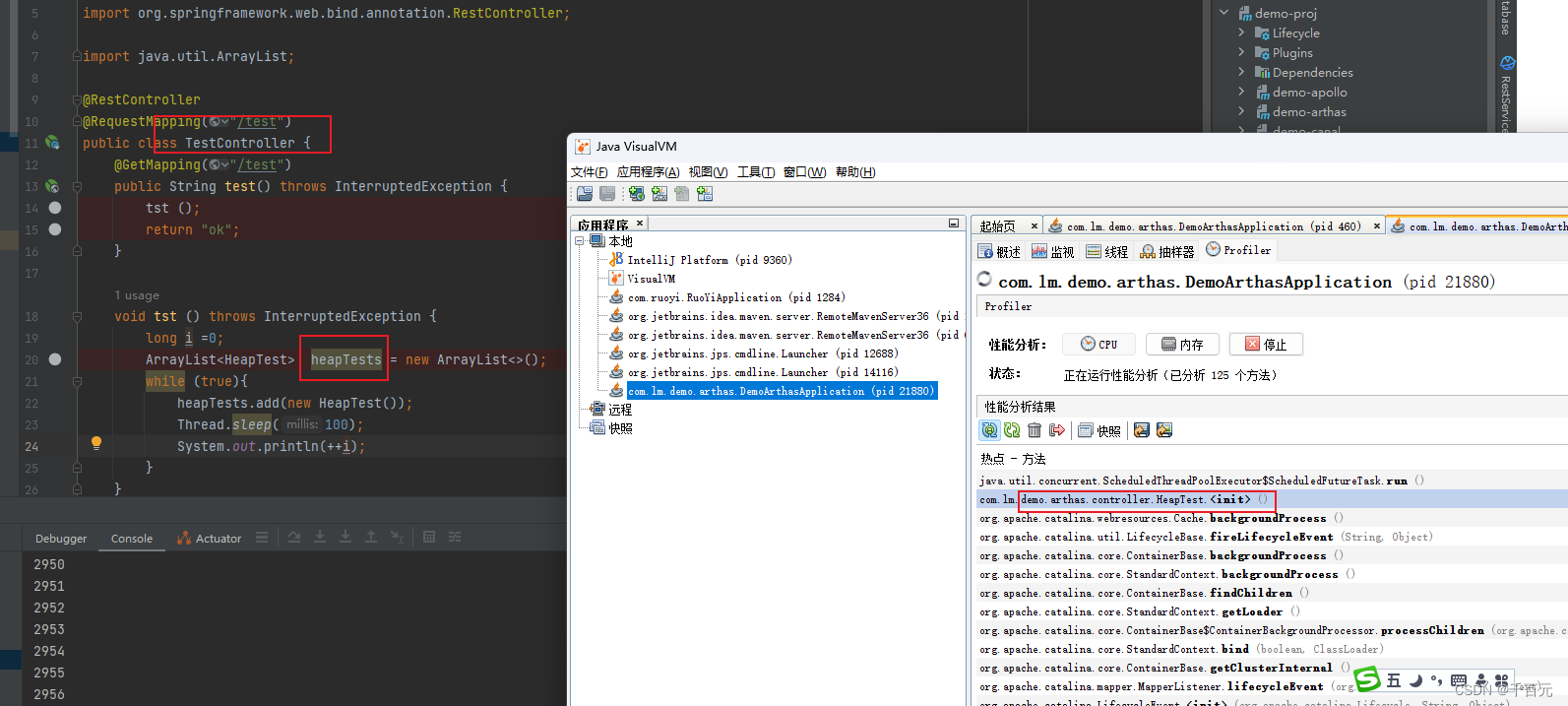

部分代码展示

//========================================================================== //温湿度计dht11的数据采集,采集间隔1s //========================================================================== module dht11( i_clk, i_rst_n, io_data, o_temp, o_humi ); input i_clk;//50mhz input i_rst_n;//低电平复位 inout io_data;//数据端口 output reg [7:0]o_temp;//输出温度 output reg [7:0]o_humi;//输出湿度 reg o_data;//输出数据 reg [39:0]get_data;//dht11获取的数据 reg [5:0]data_num;//获取数据的位数 reg[3:0]crt_state;//三段状态机 reg [3:0]next_state; parameter idle = 4'b0001;//空闲状态 parameter init = 4'b0010;//主机请求复位状态 parameter ans = 4'b0100;//从机应答 parameter rd_data = 4'b1000;//接受数据 reg data_sam1;//输入采样1 reg data_sam2;//输入采样2 reg data_pluse;//检测输入上升沿脉冲 always@(posedge i_clk ) begin data_sam1<=io_data; data_sam2<=data_sam1; data_pluse<=(~data_sam2)&data_sam1; end reg[26:0] cnt_1s;//1s计数器 always@(posedge i_clk or negedge i_rst_n ) if(!i_rst_n) cnt_1s<=27'd0; else if(cnt_1s==27'd49999999) cnt_1s<=27'd0; else cnt_1s<=cnt_1s+1'b1; reg updata=0; reg[26:0] cnt_2s=27'd0;//2s计数器 always@(posedge i_clk or negedge i_rst_n ) if(!i_rst_n) cnt_2s<=27'd0; else if(cnt_2s==27'd99999999) cnt_2s<=27'd0; else cnt_2s<=cnt_2s+1'b1; always@(posedge i_clk) if(cnt_2s==27'd99999999) updata<=1; else updata<=0; /============状态机 always@(posedge i_clk or negedge i_rst_n ) if(!i_rst_n) crt_state<=idle; else if(updata==1)//2s更新一次 crt_state<=idle; else crt_state<=next_state;

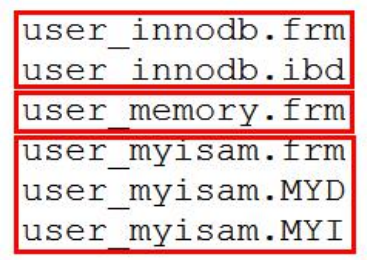

设计文档:

设计文档.doc

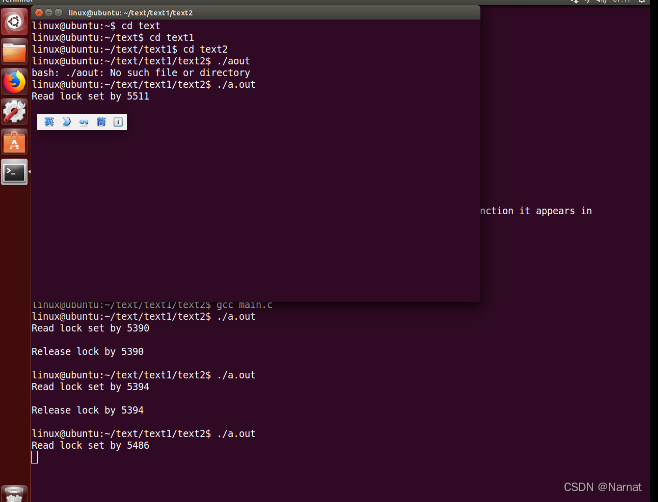

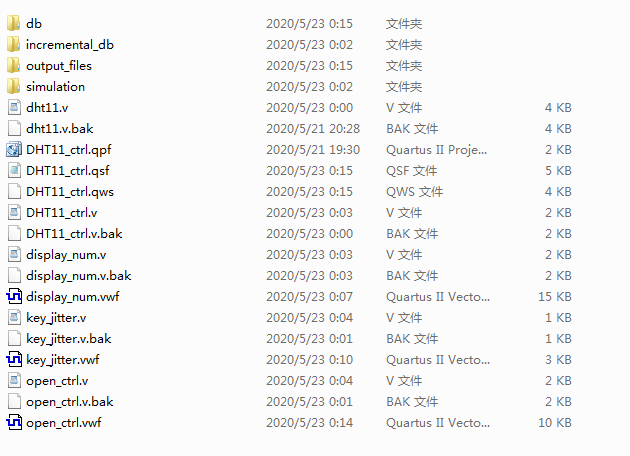

1. 工程文件

2. 程序文件

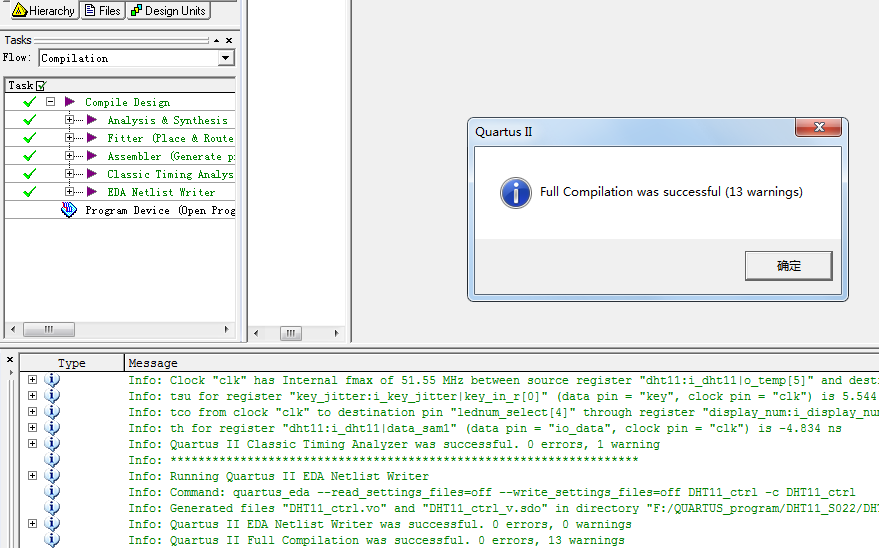

3. 程序编译

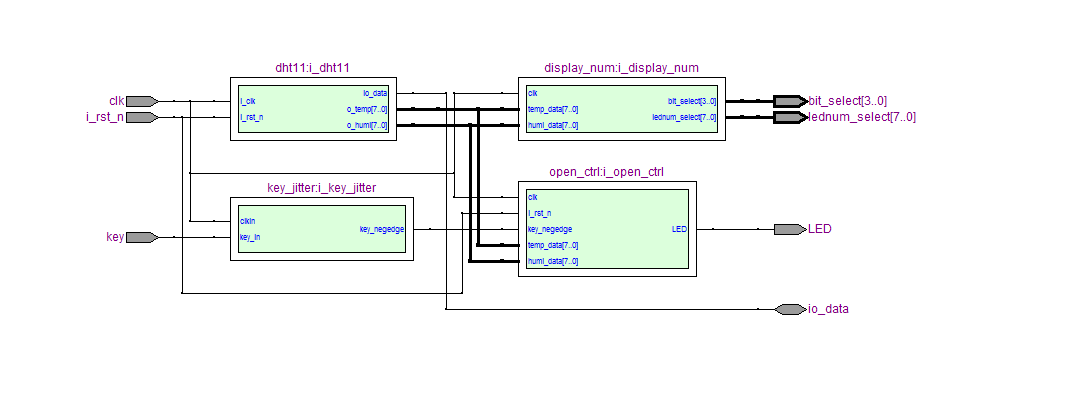

4. RTL图

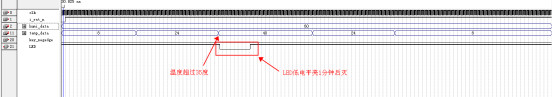

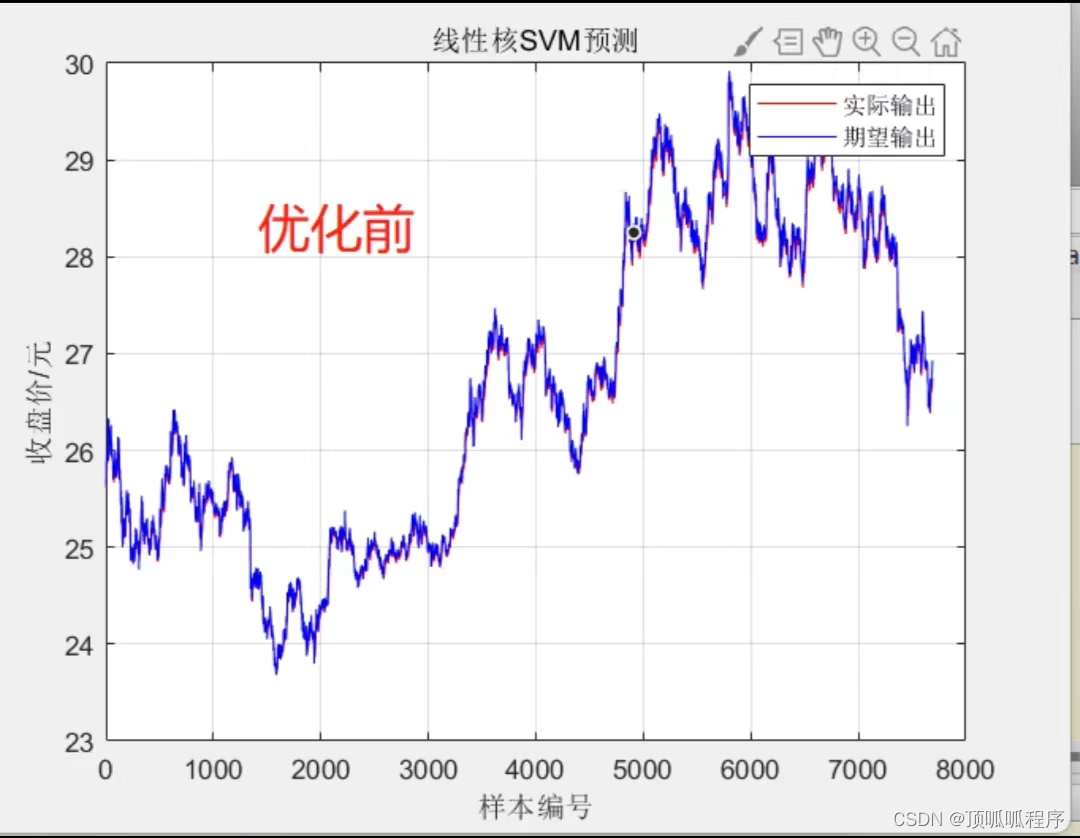

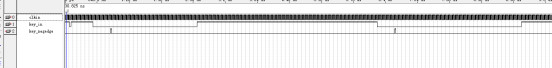

5. 仿真图

按键消抖模块仿真

数码管显示模块仿真

开启控制模块仿真